适用于多通道动态TDMA系统的高速数据复接实现方法

卢华

【摘要】 数据复接是通信中的一个重要环节,本文针对动态TDMA系统的强实时性要求设计了一种基于FPGA的高速低时延数据复接方法,同时解决了数据链对数据复接提出的多通道并发问题,本文着重介绍了数据存储和队列管理的方法,整个设计已经实现,并在实际通信系统中应用。

【关键词】 数据复接 数据存储 队列管理 FPGA

Lu Hua (Southwest China Institute of Electronic Technology, Chengdu 610036, China)

Abstract: Multiplexer is an important part of communication, in this paper a high-speed and low-latency Multiplexer based on FPGA is designed for the real-time requirement of dynamic TDMA system,at the same time this paper solved the multi-channel requirement of the data link.This paper focusing on the data storage and queue management methods.The design is implemented with and has been successfully used in our communication systems.

Key words: multiplexer,data storage,queues management,FPGA

一、引言

信息化战争中空中信息平台、空中武器装备平台之间的通信,正由点对点通信向数据链、网络发展,并从窄带通信向宽带通信发展,通信平台中为了提高网络的通信容量采用多通道频分通信技术。

在链路层接入技术上,随着同步技术(如GPS卫导同步[1]等)的不断发展,时分多址(Time Division Multiple Access,简称TDMA)接入技术凭借频谱利用率高、系统容量大等优点,广泛应用于民用与军用无线网络中。对于多信道互联网络,为了解决子网间负载不均衡,网间中继拥塞等现象,实现时隙资源的全局资源优化采用动态TDMA技术[2]。

数据复接将多路不同类型、不同速率的数据流经过组帧,复接成一路高速数据流[3]。迄今为止国内外数据复接技术在民用领域展开了广泛的研究,主要针对信道独占的点对点通信系统[4-8]。动态TDMA通信网络中具有突发性,通信对象多变等特点,传统数据复接采用连续数据流水设计不适合TDMA通信条件下的突发通信。另外传统数据复接数据缓存设计简单,采用FPGA内部FIFO缓存数据[3,5-8],存储容量小,当通信干扰导致连接短暂断开或者时隙协商失败时从而FIFO溢出导致数据丢帧,通信速率越高该问题越突出;仅仅针对单通道的数据复接[3-8],至今未查阅到多通道数据复接的相关文献。

本文利用FPGA实现数据高速数据的复接,FPGA具有反复可编程,应用灵活,资源丰富等优点,更重要的是其按信号的硬件逻辑运行,速度快,实时性好[9],采用QDRII+缓存数据帧,设计了灵活的队列管理和调度的方式,实现多通道并行的高速低时延数据复接。

二、数据复接系统模型

2.1复接方法

根据参与复接的各支路码元数字结构情况,把复接分为三种:按位复接、按字复接、按帧复接。按位复接,也称“比特单位复接”。这种方法每次复接一位码;按字复接就是每次复接取一个支路的8位码,各个支路的码轮流被复接;按帧每次复接一个支路的一帧数码,复接以后的码序列顺序为:第1路的第一帧、第2路的第一帧、第3路的第一帧、第4路的第一帧、第1路的第二帧、第2路的第二帧,后面的依此类推。也就是说,各路的第一帧依次取过以后,再循环取以后的各个帧。这种复接方法的优点是复接时不破坏原来各个帧的结构,有利于交换,但要求有更大的存储容量[7]。本文应用于TDMA的无线通信网络中,为了进行数据交换采用按帧复接的方法。

图1为复接的帧结构,NDU(Network-layer Data Unit,简称NDU)为来自不同源的数据帧,LDU(Link-layer Data Unit,简称LDU)为数据复接的输出,其由基本报头和若干NDU组成。基本报头包含LDU的目的地址、源地址、长度等信息。同一个LDU的NDU目的地址相同。LDU的长度由当前的通信速率和时隙长度计算得到。

2.2约束条件

2.3 NDU数据帧结构

本文涉及的数据帧结构复杂,是本文的难点之一,每个网络节点需缓存发送到其他节点的NDU数据,NDU数据的长度不固定,NDU数据根据重要性和实时性要求分为4个优先级。

用图2的三维模型表示NDU数据结构,X方向表示优先级,网络节点之间需要通过数据链传输的话音、图像、业务消息、视频数据、管理消息等信息按照优先级分别存入4个队列中;Y方向为以目的地址划分的网络节点,本网络节点需要传输到对应网络节点目的地址的数据存入相应的优先级队列中;Z方向表示NDU数据帧,图2中黑色表示由本网络节点发送到网络节点2、优先级2的第二个NDU数据帧。同一目的网络节点的同一优先级NDU数据为一个先入先出队列,复接时先复接高优先级NDU再复接低优先NDU。

三、数据复接实现方法

3.1硬件架构

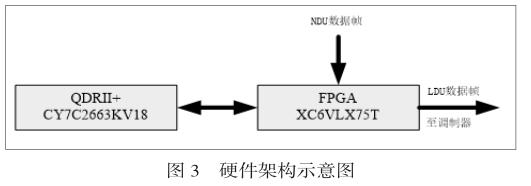

本文选用Xilinx公司的XC6VLX75T FPGA实现数据复接,XC6VLX75T采用40nm工艺,具有速度快、功耗低、内部资源丰富和高速接口丰富的特点。本文通过XC6VLX75T的两对高速串行总线RapidIO接口输入NDU、输出LDU。

多通道动态TDMA系统的高速数据复接需要很高的实时性,对存储器的选择非常关键,NDU数据帧存储器须要满足高带宽和高实时性的要求。现在常用的存储器有可以分为ROM、RAM和Flash等类别。ROM为只读存储器,Flash的写速度慢显然不能满足本文应用需求,RAM由分为两大类SSRAM和SDRAM,两种当前都能够达到很高的带宽,如DDR2,DDR3单颗很容易达到10Gbps以上的带宽,因此两类RAM能够满足高带宽的要求,SDRAM是动态RAM需要刷新因此,刷新时不能进行数据读写,因此实时性不如SSRAM[10]。

本文采用QDRII+作为NDU数据帧的缓存器,QDRII+是SSRAM的一种,具有两个典型的特点:1、带宽高,读写端口独立,分别独享带宽;2、高实时性,以零等待(100ns以内)完成猝发访问。QDRII+型号为CY7C2663KV18,大小为144Mbit,位宽为18bit,接口时钟速率为200Mhz,由于采用DDR的方式读写数据,因此读、写理论带宽分别为7.2Gbps。

硬件架构如图3所示,CY7C2663KV18和XC6VLX75T直接相连,NDU数据通过XC6VLX75T上的RapidIO接口输入,复接后的LDU数据帧通过XC6VLX75T上的RapidIO接口输出。

3.2队列管理

数据帧存储采用文件存储结构,如图4所示首地址P_ base_address_n和帧长度Length_n可以唯一的确定一帧数据的位置,这两个参数作为帧的索引值,所有帧的索引值组成索引表。索引表和帧数据独立存储,将索引表存储于FPGA内部,数据的存储于QDRII+中,利用FPGA的快速性和QDRII+的容量优势,达到了大容量数据高速存储的目的。

索引表是一个先入先出队列,NDU数据帧输入时,将NDU帧写入QDRII+中,并在索引表的末尾添加一个索引值保存NDU的首地址和帧长度,NDU数据帧复接时,从索引表头上读取一个索引值,根据索引值找到NDU,在索引表中删除该索引值。采用FPGA内部的FIFO来实现索引表, FIFO为Xilinx官方提供的先入先出队列IP Core,如图 5所示,DIN为FIFO的输入信号,其中DIN[31:0]连接P_base_ address_n表示输入NDU初始地址,DIN[47:32]连接Length_ n表示输入NDU长度,输出信号DOUT定义和DIN相同,RD_DATA_COUNT[9:0]表示FIFO索引表中存储的索引值总数,即索引表长度。

本文包含4个通信节点,NDU数据分为4个优先级,每个优先级单独建立数据队列,每个通信节点内建立16个数据队列。每个数据队列单独建立索引表,建立16个索引表,消耗FPGA内部16个FIFO。QDRII+空间划为16份,本文将QDRII+平均分配为9Mbit的16份,每一份独立存储一个数据队列。

队列管理FPGA逻辑实现如图 6所示,FPGA从RapidIO接收NDU数据后,根据输入NDU数据目的通信成员节点地址和优先级,分流到16个优先级管理队列中,如图6所示。

本文设计的队列为循环队列,用FPGA内部P_head_ address_n、P_tail_address_n两个寄存器分别表示队首和队尾。当NDU数据写入后队列管理器移动P_head_address_n,P_head_address_n通过n-1帧的首地址P_head _address_n-1加上n-1帧的长度Length_n-1得到,队列管理器将P_base_ address_n和Length_n写入到队列索引表中。当数据复接器需要从数据队列中读取出NDU时,根据从索引表FIFO中读取出NDU的基地址和NDU帧长度从QDRII+中读取一帧完整的NDU数据,数据读取成功后移动P_tail_address_n将其指示到新的队尾。

3.3数据复接

数据复接器由FPGA内部的一个状态机实现,如图 7所示,FPGA复位后或者一帧复接结束后状态机处于IDLE状态,等待时隙开始时刻,数据复接器启动数据复接,状态机进入Queue_sel状态;Queue_sel状态数据复接器选择数据帧队列,首先通过一个16选4的选择器选择目的通信节点地址的4个NDU数据队列,然后通过轮询的方式选择其中一个数据队列,选择数据队列后状态机进入Arbitrage状态。

当多路数据并行复接时,多路同时读取QDRII+中的数据,由图 6所示的数据仲裁器进行QDRII+读权限的仲裁,数据仲裁器的工作流程如图 8所示,数据复接器在Arbitrage状态时向数据仲裁器提出仲裁请求,仲裁器根据先来先获取的原则,判决QDRII+的使用权限,数据复接器获取QDRII+读取权限后进入Read状态,复接器在Read状态控制Rd_ Cmd和Rd_Addr信号产生图9所示的时序向QDRII+发起读数请求,Rd_Cmd表示读数请求,Rd_Addr表示读数地址。QDR II+数据通过Data_Valid和Data输出,Data_Valid表示输出数据有效,Data为数据输出总线。从发起到Rd_Cmd到数据输出之间有一定时延,在复接器读请求发送完成后进入Wait状态等待QDRII+数据输出,当Rd_Cmd数量和Data_ Valid数量相等时表示数据从QDRII+全部读出,状态机进入Multiplexer状态进行复接。

NDU数据从QDRII+中读出后存入FIFO中跨时钟域处理,FPGA在Multiplexer状态将若干NDU和基本包头拼接为图1所示的LDU数据帧,复接过程中的LDU缓存在内部RAM中,待复接NDU存入FIFO后,计算该NDU数据在缓存RAM中的起始地址,然后将数据从FIFO中搬入缓存 RAM中,直到NDU的长度达到最大长度或者对应节点的队列为空,状态机进入Head状态,向RAM中写入LDU头。状态机结束一次LDU复接,重新回到IDLE状态。

四、测试结果

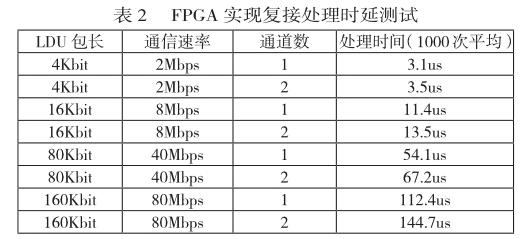

外部激励产生NDU测试数据包,测试通信速率从2Mbps-80Mbps,LDU包长度从4Kbit-160Kbit,测试NDU数据通过RapidIO总线写入到FPGA中, FPGA每2ms发起一次复接,复接分为单通道和双通道并行复接两种情况,FPGA内部计时器(5ns步进)计算LDU复接过程消耗的时间,测试结果见表2。

从表2测试结果可见:

1、本文的高速数据复接方法处理时延短,在160Mbps通信速率下,双通道同时进行数据复接仅需要不足200us的通信时间,在2ms时隙情况下,复接环节仅占时隙的十分之一,数据链协议,编码调制留下了充足的处理时间,能够满足多通道动态TDMA下对数据复接提出的强实时性要求。

2、FPGA的数据复接处理时延单通道和双通道没有明显差异,通信速率2Mbps、8Mbps, 40Mbps,80Mbps时双通道的复接时间分别是单通道复接时间的1.12、1.18、1.24、1.29倍,本设计可以适用多通道高实时性的数据复接。

五、结论

本文设计一种基于FPGA的数据复接方法,满足由于动态时隙TDMA环境下低时延强实时性的要求,能够实现高速、多通道并行的数据复接,重点研究了复接过程中的数据存储和队列管理,本文根据FPGA的特点用FIFO实现基于文件存储结构的分布式排队管理器,对于通信、图像处理等需要快速数据队列调度的应用具有参考意义。

参 考 文 献

[1] 徐世许,王涛. INS/GPS组合导航系统的数据精确同步方法[J]. 中国惯性技术学报,2008,16(5):563 – 565.

[2] 王昭. 一种适用于多信道联合组网的时隙分配新算法[J].电讯技术,2014,54(4):506-512.[WANG Zhao. A New Algorithm for Time Slot Assignment in Multi-Channel Networking Environments[J].Telecommunication Eengineering, 2014,54(4):506-512.].

[3] 杨保平,陈永光,陈军,徐忠富.基于FPGA 的战术数据链中继传输复接技术[J].系统工程与电子技术.2010,32(12):2628-2631.

[4] 宋学瑞,蔡子裕,段青青.基于FPGA 的同步数字复接系统设计与实现[J].计算机测量与控制.2008,16( 8):1174-1176.

[5] 赵妍.高速数据复接器. [D].西安:西安电子科技大学,2007:10.

[6] 肖勇军.基于FPGA的数字复接器的设计与实现[D].武汉:武汉大学,2004.5.

[7] 黄飞.高速数据复接器的研究与实现[D].武汉:武汉大学,2004.5.

[8] 王琦.异步高速数据复接器. [D].西安:西安电子科技大学,2010:12.

[9] Wolf Wayne.FPGA-Base System Design [M].Beijing:Prentice Hall PTR,2005.

[10] 杜贵然,张民选,谢伦国.Pentium 系统采用SSRAM/ SDRAM存储器的性能分析[J].计算机工程与科学.1996.18(3):16-20.