阵元失效对相控阵天线低副瓣的影响分析*

潘 超 张 任 李 瑞

(中国船舶重工集团公司第七二二研究所 武汉 430205)

阵元失效对相控阵天线低副瓣的影响分析*

潘超张任李瑞

(中国船舶重工集团公司第七二二研究所武汉430205)

摘要针对相控阵天线时常发生阵元失效这一问题,以一维均匀直线阵为模型,分析了阵元失效对相控阵天线低副瓣电平的影响,主要考察了失效阵元个数和失效阵元位置这两个要素。计算机仿真结果表明,当失效阵元位于阵列两端位置时,低副瓣电平恶化较轻,而当失效阵元位于阵列中间位置时,低副瓣电平恶化较严重。对于预先设计-30dB低副瓣电平的24元均匀直线阵,当失效阵元超过2个时,最大副瓣电平大于-20dB的概率超过0.9。

关键词相控阵天线; 阵元失效; 副瓣电平; 波束形成

Class NumberTN821.8

1 引言

低副瓣是相控阵天线一项非常重要的性能指标[1~2]。在接收状态下,低副瓣能够抑制从副瓣进来的干扰和杂波,从而有效提高接收信号的信噪比[3]。在发射状态下,低副瓣能够降低从副瓣泄露出去的能量,从而有效提高系统设备的抗敌方侦查能力[4]。然而,由于高低温变化以及振动等较恶劣的外界环境以及硬件的使用寿命等原因,相控阵天线时常会产生阵元失效的问题[5~6]。失效的阵元会破坏阵列原有的几何结构特性,直接导致阵列的副瓣级明显升高,严重影响了阵列的性能。鉴于此,研究阵元失效,如失效阵元个数以及失效阵元分布位置等,并评估这些要素对低副瓣的影响程度具有重要的工程实践价值。本文以一维均匀直线阵为模型,对阵元失效对低副瓣的影响进行了统计分析,并给出了相应的结论,这些结论对相控阵天线的监测与维护具有指导意义。

2 低副瓣方向图合成

2.1阵列方向图合成

以一维均匀直线阵为模型,图1展示了N元阵列示意图,设阵元间距为d,且各阵元均为各向同性阵元,于是该阵列的导向矢量可表示为

a(q)=[1,ejb,…,ej(N-1)b]T

(1)

图1 阵列空间位置关系示意图

阵列方向图定义为给定阵列权矢量W对不同角度信号的阵列响应

F(q)=WHa(q)

(2)

W=[ω1,ω2,…,ωN]T

(3)

其中,wi=Iiejφi为第i个阵元的激励,Ii、φi分别为激励的幅度与相位。

2.2低副瓣方法

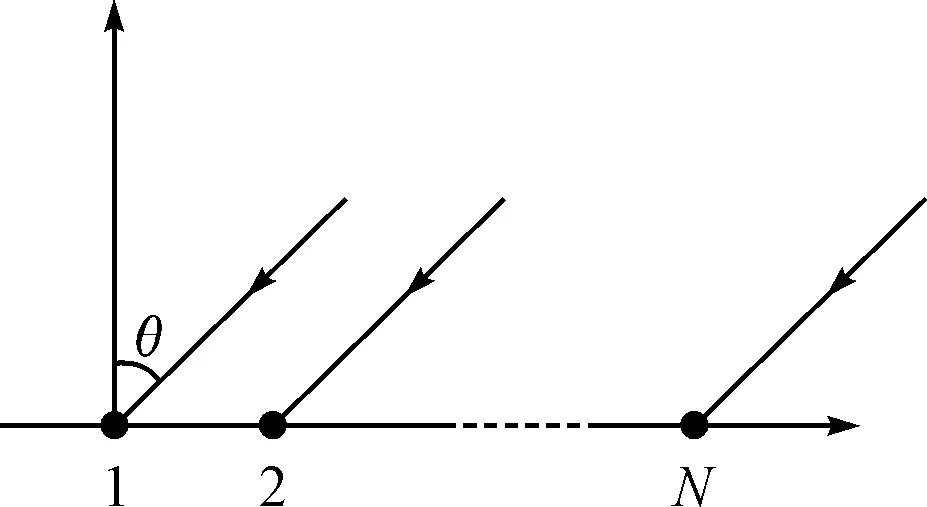

图2 -30dB低副瓣电平的加权系数

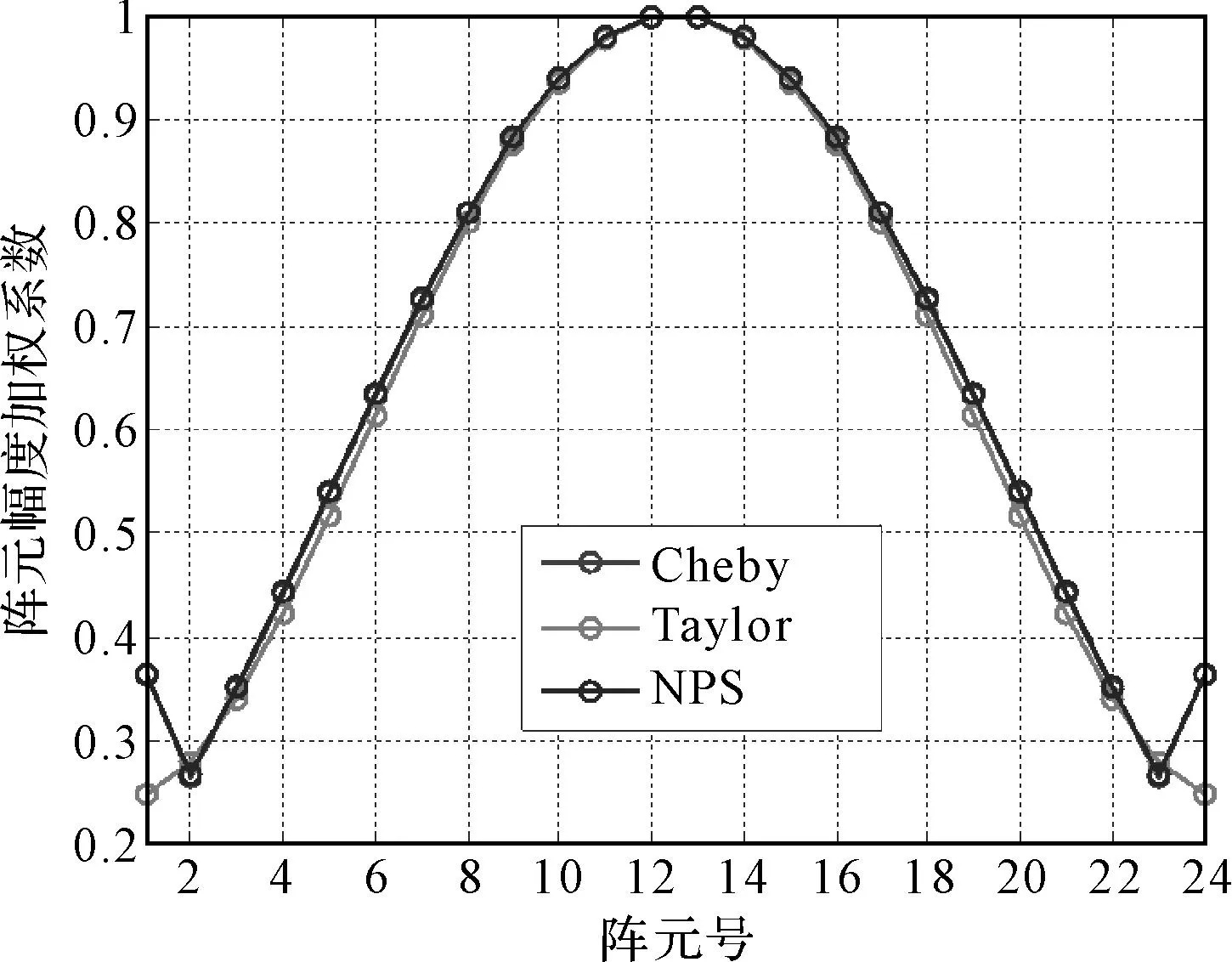

图3 -30dB低副瓣电平方向图

低副瓣方向图合成就是要寻找特定的阵列权矢量W使得合成的方向图F(θ)具有满足实际需求的低副瓣电平。常见的低副瓣合成方法有经典的Chebyshev加权法[7~8]、Tayler加权法[9]以及基于自适应阵列理论的方法,如数值综合法NPS[10~12]。本文重点讨论阵元失效对低副瓣的影响,对于低副瓣方法的具体实现不做介绍。图2展示了使用三类加权方法对24元均匀直线阵实现-30dB低副瓣电平的加权系数,图3展示了相应的低副瓣方向图,其中常规波束形成的最大副瓣电平为-13.21dB,低副瓣波束形成实现了-30dB的低副瓣电平。

3 阵元失效对低副瓣的影响

阵元失效,意味着失效阵元的激励ωi=0。失效的阵元会破坏阵列原有的几何结构特性,为了评估阵元失效对低副瓣的影响,这里引入两个副瓣电平恶化参数,最大副瓣电平恶化量和最大副瓣电平超限概率。

1)最大副瓣电平恶化量

最大副瓣电平恶化量TSLL计算如下:

TSLL=SLLP-SLLC

(4)

其中SLLP为设计的最大副瓣电平,SLLC为存在阵元失效时的最大副瓣电平。

2)最大副瓣电平超限概率PC

假设各个阵元失效是独立同分布事件,设定最大副瓣电平容忍值为SLLS,当已知阵元失效个数,计算出SLLC>SLLS的概率,

PC=NS/NC

(5)

其中,NS为使得SLLC>SLLS的阵元失效位置组合数,NC为阵元失效位置总组合数。

4 计算机仿真

以24元均匀直线阵为例,使用Chebyshev加权法预先设计了-30dB的均匀副瓣电平,对此分析失效阵元个数分别为1、2、3、4情况下阵列方向图的最大副瓣电平。

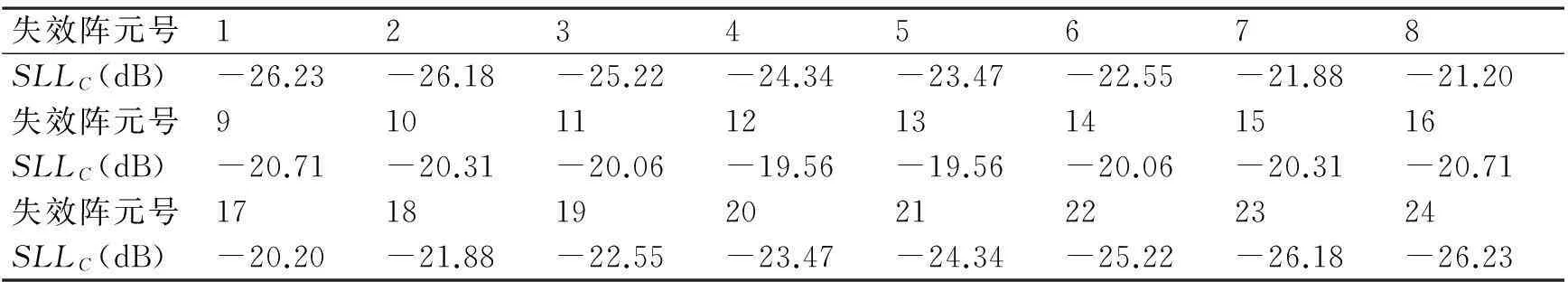

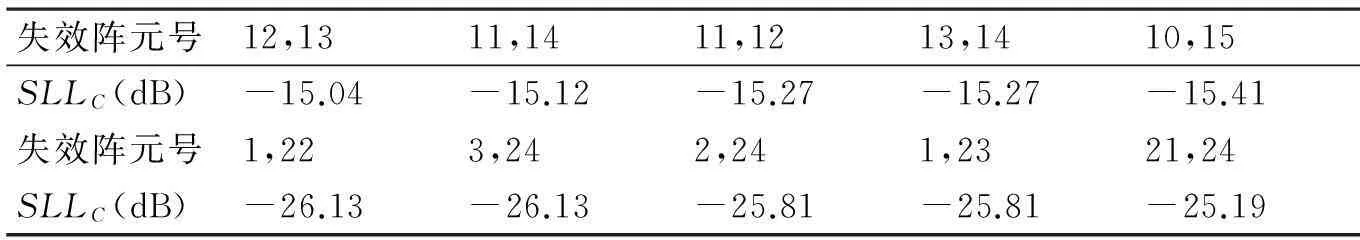

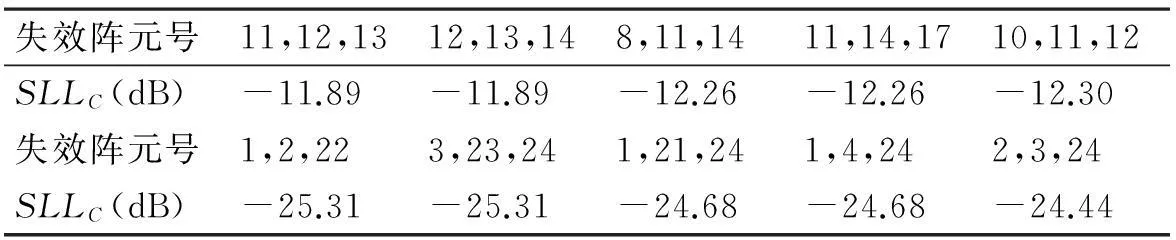

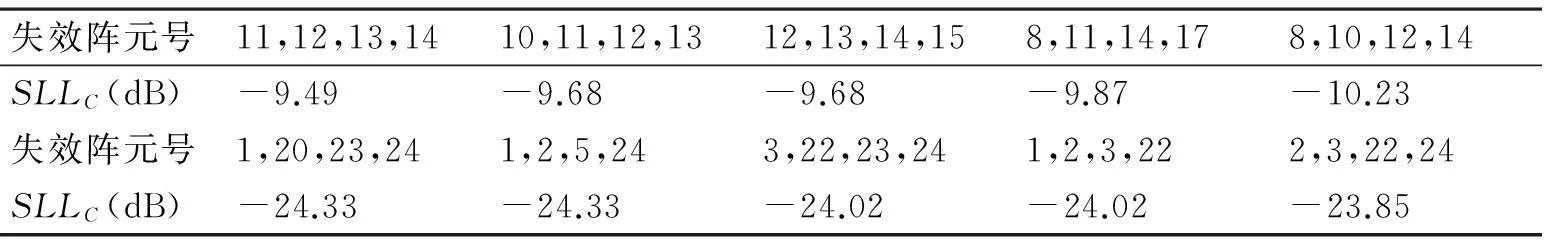

表1列出了存在1个失效阵元时阵列方向图的最大副瓣电平,表2~表4则分别列出了存在2、3、4个失效阵元时,副瓣电平恶化最严重和最弱的五种失效阵元组合下的最大副瓣电平。可见,当失效阵元位于阵列中间位置时,副瓣电平恶化较严重,而当失效阵元位于阵元两端时,副瓣电平恶化较弱。

表1 失效1个阵元时的最大副瓣电平SLLC

表2 失效2个阵元时的最大副瓣电平SLLC

表3 失效3个阵元时的最大副瓣电平SLLC

表4 失效4个阵元时的最大副瓣电平SLLC

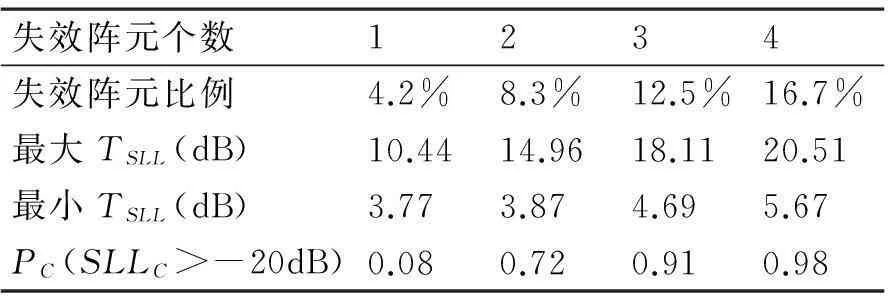

表5列出了最大副瓣电平恶化参数,其中最大副瓣电平容忍值设为-20dB,可见当监测到失效阵元个数超过2时,最大副瓣电平高于-20dB的概率大于0.9,即预先设计的低副瓣已经恶化到不可接受的程度,此时应该考虑对相控阵天线的失效阵元进行更换或者采取补偿算法进行补偿。

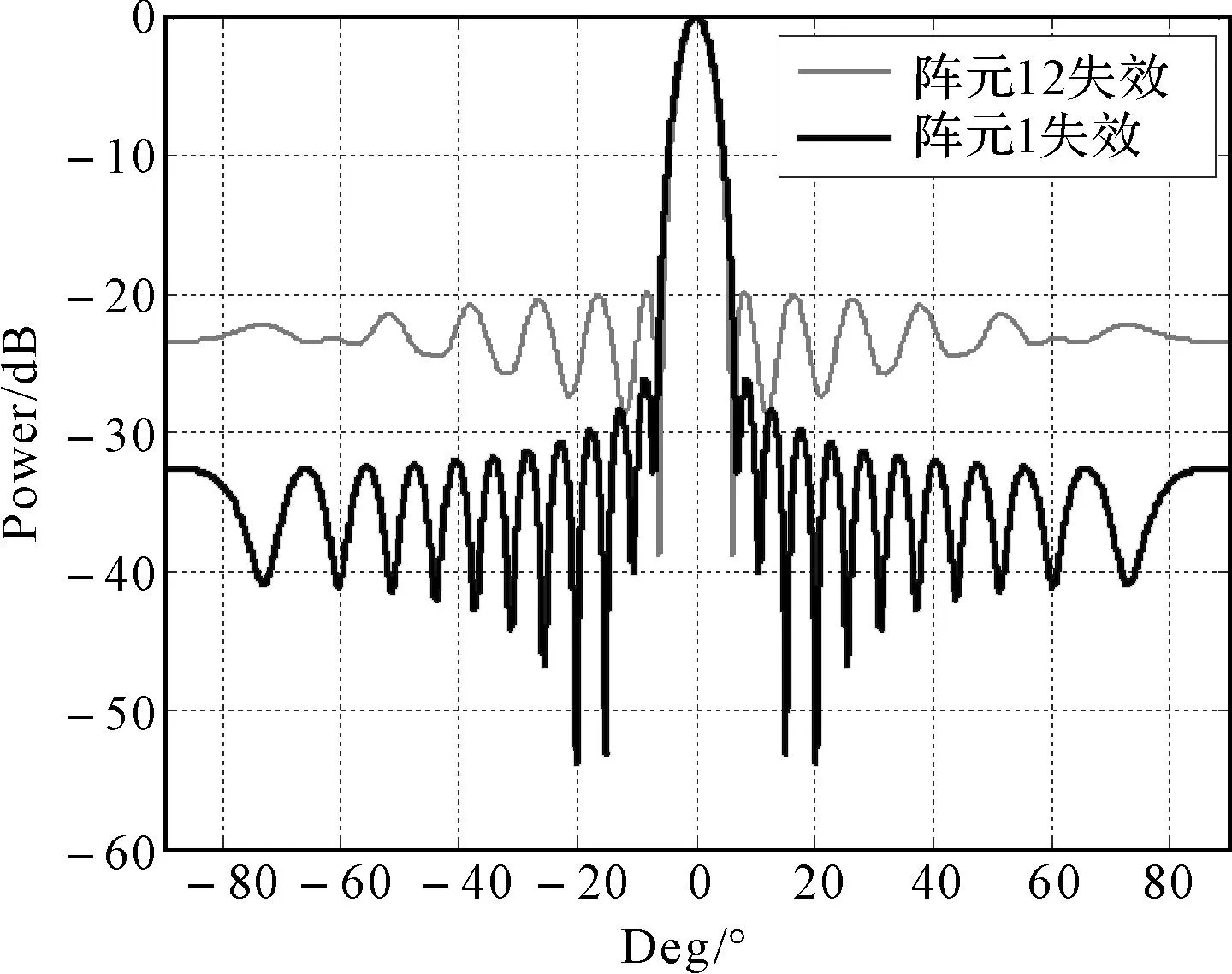

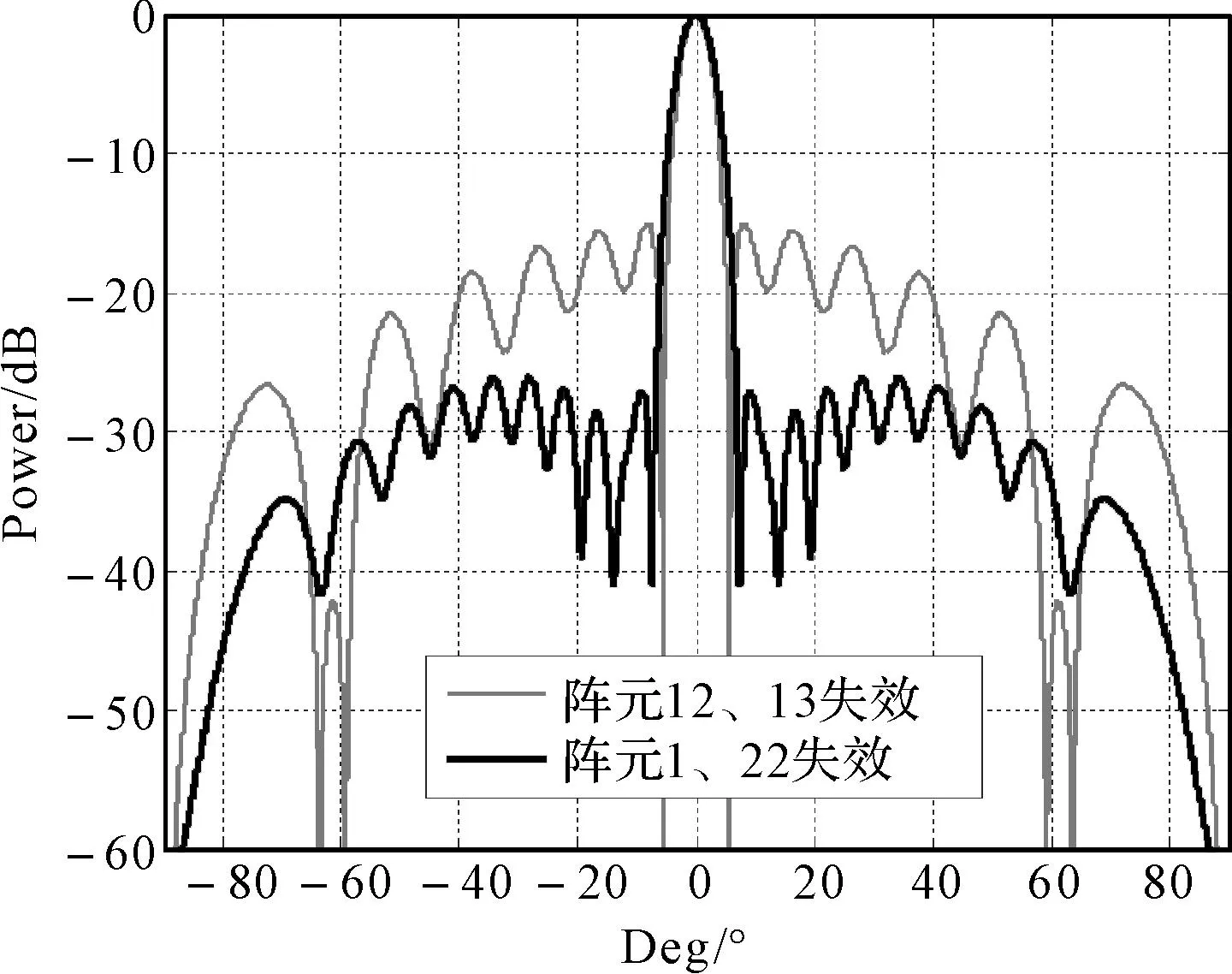

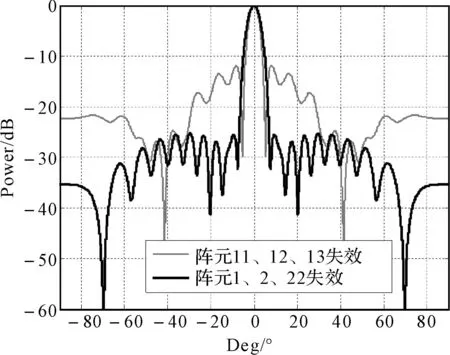

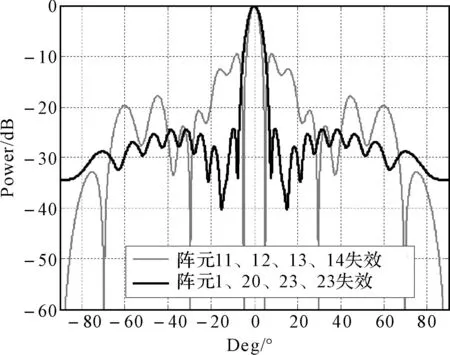

为了更加直观地了解阵元失效对低副瓣电平的影响,图4~图7分别展示了阵元失效个数为1、2、3、4时,最大副瓣电平恶化最严重和最弱时的阵列方向图。

表5 最大副瓣电平恶化参数

图4 失效1个阵元时的方向图

图5 失效2个阵元时的方向图

图6 失效3个阵元时的方向图

图7 失效4个阵元时的方向图

5 结语

本文分析了阵元失效对相控阵天线低副瓣电平的影响,主要考察了失效阵元个数和失效阵元位置这两个要素。计算机仿真结果表明,当失效阵元位于阵列两端位置时,低副瓣电平恶化较轻,而当失效阵元位于阵列中间位置时,低副瓣电平恶化较严重。对于预先设计-30dB均匀副瓣电平的24元均匀直线阵,当失效阵元超过2个时,最大副瓣电平大于-20dB的概率超过0.9。该结论可以给相控阵监测与维护提供一定的指导。

参 考 文 献

[1] 李丽娴,胡俊毅,王建中.一种新型C波段轻型低副瓣线阵天线[J].无线电工程,2014,44(10):55-58.

[2] 孟明霞,丁晓磊,丁克乾,等.低副瓣有源相控阵天线测试方法研究[J].遥测遥控,2011,32(4):55-60.

[3] 黄飞,周焯,郑巧珍.弹载相控阵自适应低副瓣杂波抑制方法[J].制导与引信,2015,36(2):24-28.

[4] 李学森,桑成军,沙祥.雷达对抗反辐射导弹技术综述[J].电子信息与对抗技术,2008,23(1):26-31.

[5] 徐朝阳,章新华,韩东,等.阵元失效条件下拖线阵波束形成的优化方法[J].系统仿真学报,2009,21(19):6017-6019.

[6] 周志增,丁桂强,康鹏,等.基于失效阵元位置优化的天线方向图重构[J].现代防御技术,2015,43(5):129-134.

[7] Dolph C L. A current distribution for broadside arrays which optimizes the relationship between beamwidth and side-lobe level. Proc IRE,1946,34:335-348.

[8] Bresler A D. A new algorithm for calculating the current distributions of Dolph-Chebyshev arrays[J]. IEEE Transaction on Antennas and Propagation,1980,28:951-952.

[9] Taylor T T. Design of line-source antennas for narrow beamwidth and low sidelobes[J]. IEEE Transaction on Antennas and Propagation,1955,AP-3:16-28.

[10] Olen C A, Compton R T. A numerical pattern synthesis algorithm for array[J]. IEEE Transaction on Antennas and Propagation,1990,38(10):1666-1676.

[11] Dufort E C. Pattern synthesis based on adaptive array theory[J]. IEEE Transaction on Antennas and Propagation,1989,37(8):1011-1018.

[12] Suzuki Y, Chiba T. An algorithm for pattern synthesis improvenments[J]. IEEE Transaction on Antennas and Propagation,1986,34(6):825-829.

*收稿日期:2015年10月5日,修回日期:2015年11月27日

作者简介:潘超,男,博士,工程师,研究方向:相控阵天线技术。张任,男,硕士,工程师,研究方向:相控阵天线技术。李瑞,男,硕士,工程师,研究方向:信息安全技术。

中图分类号TN821.8

DOI:10.3969/j.issn.1672-9730.2016.04.022

Effects of Element Failure on Side-lobe Level of Phased Array Antenna

PAN ChaoZHANG RenLI Rui

(No.722 Research Institute, CSIC Wuhan430205)

AbstractArray-element can fail during working usually because of various reasons. Aimming at this question, the effects of element failure on the side-lobe level of phased array antenna are analyzed based on the model of one-dimension uniform linear array. And the number and the distribution position of the failed elements are studied. Simulation results show that the side-lobe level will deteriorate slightly when the failed elements are located at the both ends of the array, but it will deteriorate seriously when the failed elements are located at the middle of the array. For the 24-element uniform linear array with -30dB side-lobe level, the probability of the side-lobe level is higher than -20dB exceeds 90 percents when the number of failed elements is more than 2.

Key Wordsphased array antenna, element failure, side-lobe level, beamforming