基于FPGA的水下数据存储系统设计*

孙 昕 张世海

(91439部队96分队 大连 116041)

基于FPGA的水下数据存储系统设计*

孙昕张世海

(91439部队96分队大连116041)

摘要为了解决在水下多通道数据采集系统中不能满足高速大容量数据脱机存储的问题,设计了一种基于FPGA的磁盘阵列存储方案。在以Cyclone Ⅳ FPGA为核心的SOPC系统上实现了IDE接口控制,并完成了硬盘参数检测与初始化配置以及基于PIO模式的数据读写。基于磁盘阵列存储的设计思想,采用IDE/SATA双接口和双通道的双存储设计,利用FATFS文件系统进行文件的管理,在完成数据备份任务的同时,增强数据存储系统的扩展性和灵活性。

关键词数据存储; 磁盘阵列; FPGA; SOPC; IDE

Class NumberTP274.7

1 引言

随着数字信号处理领域和电子技术的飞速发展,数据存储系统在各个领域的研究中发挥着越来越重要的作用。水声设备的不断推陈出新对存储介质的体积、容量和读写速度以及便携性等诸多方面提出了更高的要求。但是,在水下电池供电的系统中,环境恶劣,数据无法实时传输,只能现场完成信息的快速采集和准确存储,事后对数据回传或存储器回收,再由计算机对数据进行处理和测试。针对这一问题,设计一种能够在水下节点工作的数据存储系统有着十分重要的意义。传统的数据采集系统一般利用CPU或者MCU完成,这种方法将AD数据读入并转存至少需要四个时钟周期,在串行指令执行的方式下,速度和效率都会降低[1]。因此,多年来针对不同类型的处理芯片和研究方法对存储系统的研究开展广泛[2~6]。

文献[2]中介绍了一种基于16位AVR单片机的IDE(Integrated Drive Electronics)硬盘高速数字图像采集和存储系统。系统利用单片机对硬盘进行接口控制,并采用硬盘直写技术,利用两片SRAM以乒乓方式将CMOS图像传感器采集到的数字图像信息存储到硬盘中。但是由于整个系统内部的逻辑器件较多,因此产生的干扰较大。文献[3]中介绍了一种基于S3C2410嵌入式ARM处理器的IDE硬盘存储系统,该系统通过在ARM处理器内部移植Linux操作系统来对硬盘进行控制,将系统的测量数据、波形以及其它相关信息进行存储。不过处理器本身的灵活度和扩展性不够,功能实现起来较为复杂。文献[4]中介绍了一种基于TMS320系列DSP处理器的IDE硬盘数据存储系统。该系统采用了DSP作为主控制芯片,负责硬盘控制和数据的传输;FPGA和SDRAM作为辅助芯片,负责实现DSP与IDE接口之间时序的转换和数据的缓存,从而完成硬盘的控制和数据传输。但是DSP多用来做算法实现,功能比较固定,做数据存储不是其强项,并且需要其它逻辑芯片的配合,设计过程较为复杂,兼容性不强。

本文结合当前技术发展形势,研制开发了一种以FPGA为核心,基于蓄电池工作的IDE/SATA双接口和双通道的磁盘阵列存储系统。换能器是完成电能与声能转化以实现水下目标探测和通信的基本部件。

2 系统总体硬件结构设计

2.1系统设计思路和硬件设计

Nios Ⅱ是Altera公司的一款软核处理器,其最大的特点是可由用户按功能需求进行配置,易于和其他IP(intellectual property)核互联完成系统设计,可有效降低开发周期和成本。

基于Nios Ⅱ的SOPC设计是一种灵活、高效的嵌入式解决方案,它将完整产品的各个功能模块集成到一块FPGA芯片上,构成一个可编程偏上系统[7]。因此本系统采用Cyclone Ⅳ GX系列器件的EP4CGX110CF23C7作为主控芯片,其自带的8个可独立操作的全双工高速收发器作为数据的输入接口,在FPGA内部建立基于NIOS Ⅱ处理器的SOPC片上系统将接收到的数据存储到硬盘阵列中。

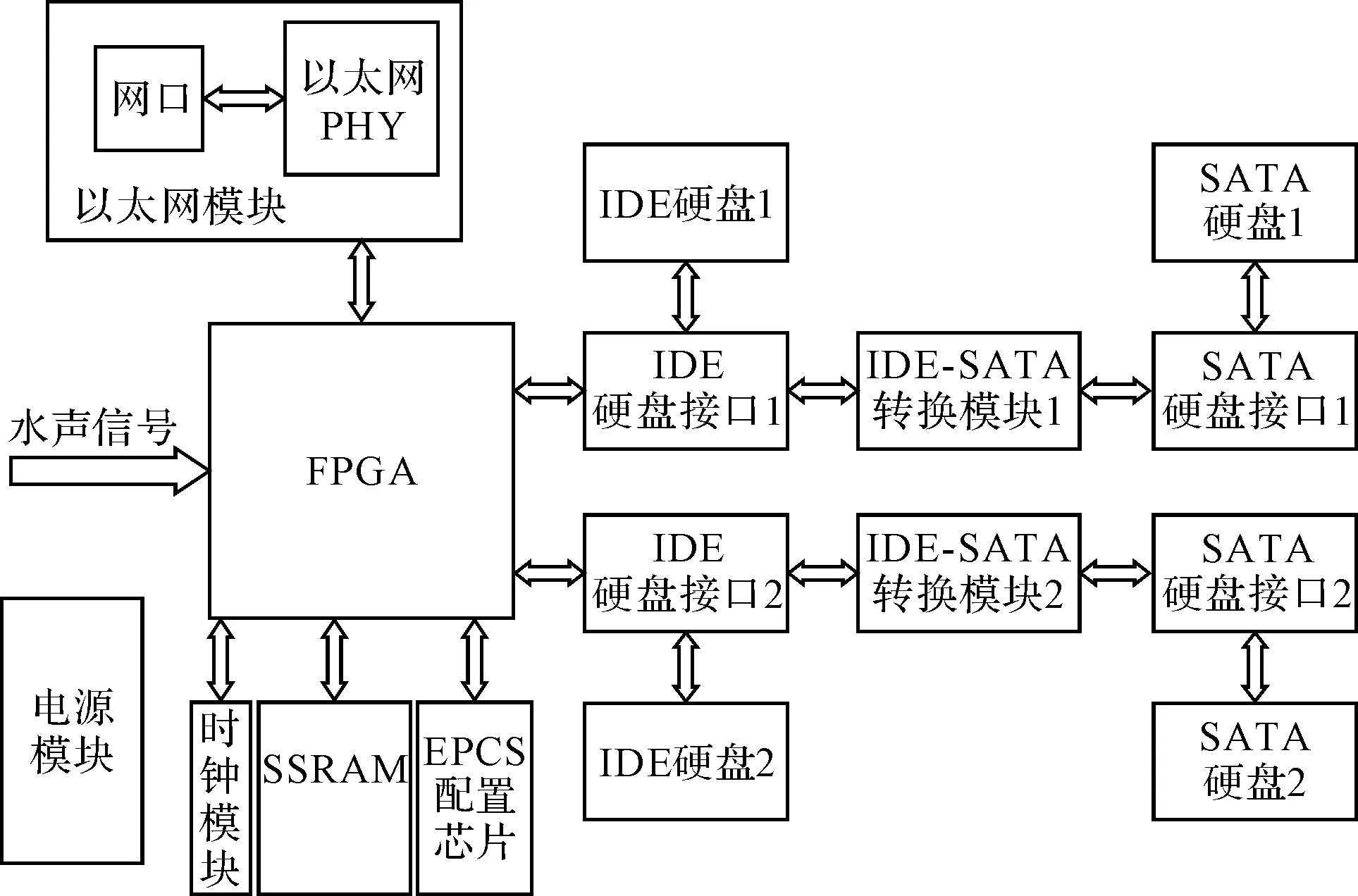

系统选用EPCS串行配置芯片在系统上电视对FPGA进行配置[8],用于存储FPGA的配置数据以及Nios Ⅱ处理器中的软件程序。采用IDE协议实现硬盘数据的传输,而目前SATA接口硬盘的使用更为广泛。因此,系统中使用了IDE-SATA接口芯片JM20330,使IDE与SATA两种硬盘均可以在系统中正常使用。另外,系统预留了以太网接口,便于后续开发过程中系统与计算机之间进行基于以太网协议的控制或数据回传。整个系统的总体结构框图如图1所示。

2.2FPGA内部硬件结构设计

FPGA是系统的核心,整个系统的任务调度和管理都由FPGA上架建的片上系统来完成。系统中包含的功能模块包括Nios Ⅱ处理器、System ID、内部定时器、JTAG_uart、片上RAM、SSRAM控制器、Avalon三态桥、IDE接口控制器和EPCS控制器等,FPGA内部的总体结构图如图2所示。

图1 数据存储系统总体结构框图

图2 FPGA内部总体结构框图

3 Nios Ⅱ系统软件设计

3.1硬盘物理介质

硬盘驱动器的磁碟由一定量的可写表面组成,每张磁盘上都有一些被称为磁道的同心圆,数据就存储在磁道上,磁头被定位在某个磁道上,磁道上的能被磁头访问的某一位置被称为柱面。同时磁道被进一步划分为扇区,扇区是最小的读写单位。访问扇区时,读写头首先被定位在正确的磁道上,等到正确的扇区转到读写头下面的时候,驱动器就开始读取数据。驱动器的每个扇区都可以被柱面、磁头和扇区号所唯一确定。

3.2IDE接口控制方法的实现

Nios Ⅱ处理器对硬盘的控制是通过接口寄存器实现的,ATA标准中定义的接口寄存器分为命令寄存器和控制/诊断寄存器两组,其中命令寄存器组用于主机与设备之间命令与参数信息的传输,控制/诊断寄存器组用于主机对设备的参数控制以及设备诊断信息的传输[9]。

系统中使用逻辑寻址方式进行寻址,因此扇区号、柱面号以及磁头号等地址信息均通过对逻辑地址的分段截取而得到。在软件程序中地址寄存器写入命令的具体实现过程如下:

IOWR_ALTERA_AVALON_CF_IDE_SECTOR_NUMBER(ide_base,LBA & 0xFF);

LBA >>=8;

IOWR_ALTERA_AVALON_CF_IDE_CYLINDER_LOW(ide_base,LBA & 0xFF);

LBA >>=8;

IOWR_ALTERA_AVALON_CF_IDE_CYLINDER_HIGH(ide_base,LBA & 0xFF);

LBA >>=8;

IOWR_ALTERA_AVALON_CF_IDE_DEVICE_HEAD(ide_base,(LBA & 0x0F));

其中,ide_base为IDE基地址,LBA为硬盘操作的逻辑地址。

3.3硬盘参数检测与初始化

为了对硬盘进行控制和操作,在硬盘使用之前应对硬盘的特性参数进行检测,以确定硬盘所支持的寻址方式、可用扇区数以及支持的操作模式等特性信息。硬盘参数检测使用IDENTIFY DEVICE指令。当主机检测到驱动器空闲且准备好时,向命令寄存器中写入参数检测指令,驱动器向扇区缓冲区中写入硬盘信息的参数块,主机利用读扇区命令进行参数的读取。

以IDE为接口的硬盘传输模式和协议分为两种:PIO(Programmed I/O)和DMA(Direct Memory Access)两种。两种模式的区别在于:PIO模式需要处理器的参与来读取数据,DMA模式则不需要[10]。为了设计简单,因此采用PIO模式作为传输协议。

图3为硬盘参数检测及初始化程序的流程图。需要完成对硬盘特性参数的检测、PIO模式的初始化以及触发中断时传输的扇区数的设置。每一步都通过对不同地址写寄存器写参数来完成。

3.4扇区数据读写软件设计

PIO操作模块接收系统控制模块发送的模式选择信号,产生硬盘PIO操作模式对应的时序控制信号,包括硬盘寄存器地址信号读写控制信号数据写入或读出信号。PIO模块通过片选信号和地址信号将要读写的硬盘扇区地址发送至硬盘,同时发送硬盘读写信号DIOR或DIOW,如果是写硬盘则将写入数据发送至数据寄存器,如果为读硬盘则从数据寄存器中读出数据[11]。

图3 硬盘参数检测及初始化程序流程图

下面以PIO模式的写操作为例进行扇区数据读写程序的设计,读命令程序的执行过程与写命令程序类似,只是数据的传输方向相反。

PIO模式的数据写操作时序要求如图4所示,在写操作过程中,处理器在将命令操作码发送到命令寄存器之前,首先要把该命令执行所需的参数写入相应寄存器,之后等待DRDY位有效,硬盘驱动器设置状态寄存器的DRQ位,准备接收数据,处理器将数据写入扇区缓冲区。当扇区缓冲区填满之后,硬盘驱动器清除DRQ位,同时置位BSY位,将扇区缓冲区中的数据写入硬盘。当数据写入硬盘后,清除BSY位,同时产生INTRQ中断请求,处理器查询硬盘状态,并清除INTRQ。如果进行的是多扇区写操作,此时硬盘驱动器重新设置DRQ,开始处理下一个扇区。

图4 PIO模式写数据时序图

图5中利用流程图的方式对PIO模式写操作程序的编写过程进行了详细的描述。

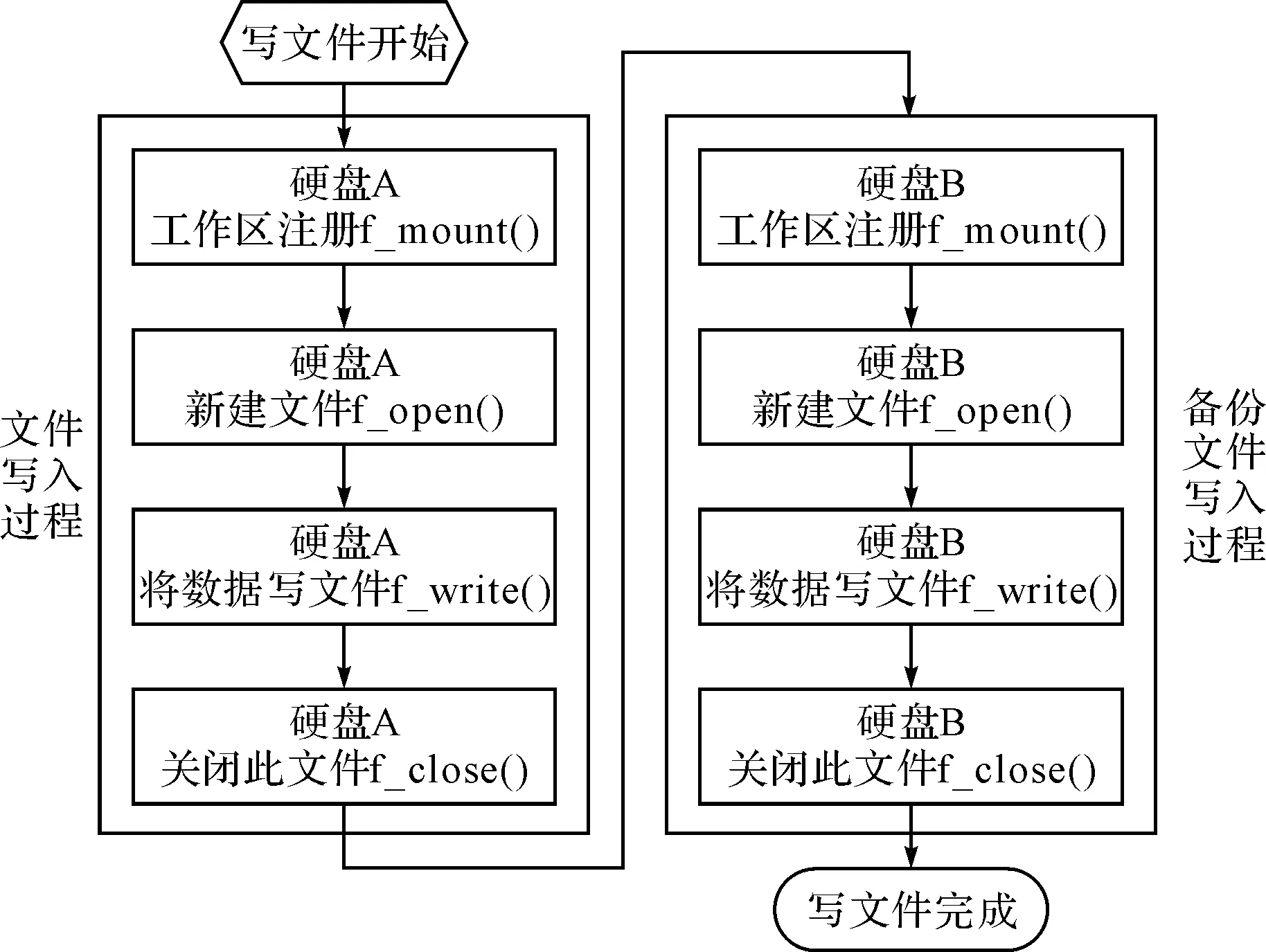

3.5磁盘阵列文件读写软件设计

系统使用了两块硬盘进行数据的存储与备份,在进行文件写入操作时,在硬盘A中完成一包数据的写入文件操作之后,开始执行数据文件备份程序,在硬盘B中写入相同的文件。文件备份完成后,在硬盘A中继续写入下一个数据文件,如此反复,完成原始数据文件和备份文件的写入,实现RAID1级别磁盘阵列的程序设计。磁盘阵列中单文件的写入过程与每一步所需调用的函数如图6所示。

图6 磁盘阵列中文件写入程序流程图

4 系统测试

将两块格式化后的硬盘连接到本数据存储系统,向硬盘A中写入数据并保存成txt文本文件,为了方便校验,写入内容为16bit递增计数器的值不断循环,并在硬盘B中进行文件的实时备份。

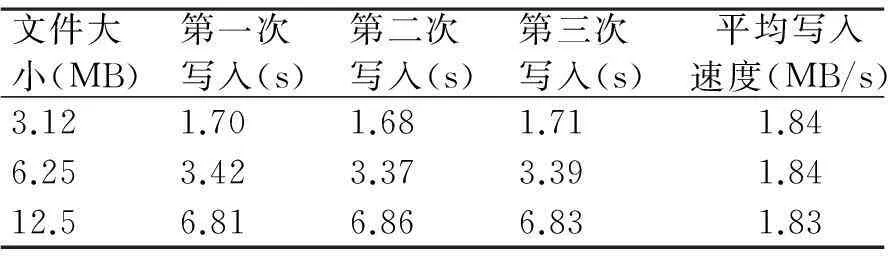

向系统中分别写入3.12MB、6.25MB和12.5MB大小的.txt文件,为了测量准确,分别进行三次写入,记录文件的写入时间。

程序执行结束后讲两个硬盘断开数据存储系统,分别连接到计算机上,编写Matlab程序对所存储的文件内容进行校验,经检查,文件内容与存储系统写入的内容相一致。测试速度结果如表1所示,可知文件的平均写入速度大约为1.84MB/s。

表1 文件写入速度测试

5 结语

本文设计实现了基于FPGA芯片为核心处理器的,能在水下节点使用的数据存储磁盘阵列系统,在FPGA内部使用了SOPC技术,利用FATFS文件系统进行文件的管理,采用IDE/SATA双接口和双通道的双存储设计,增强数据存储的灵活性和可扩展性,同时满足数据的备份需求。

参 考 文 献

[1] 王强,文丰,任勇峰.基于FPGA的高速实时数据采集存储系统[J].仪表技术与传感器,2009(1):50-52.

WANG Qian, WEN Feng, REN Yongfeng. High-speed Real-time Data Acquisition and Storage System Based on FPGA[J]. Instrument Technique and Sensor,2009(1):50-52.

[2] 李川.基于IDE硬盘的数字图像存储技术研究[D].长春:长春理工大学,2008:32-36.

LI Chuan. Research of Digital Image Storage Technique baed on IDE Hard disk[D]. Changchun: Changchun University of Science and Technology,2008:32-36.

[3] 蒋向辉.嵌入式谐波检测仪的研究与设计[D].长沙:湖南大学,2007:52.

JIANG Xianghui. Design and Research of Embedded Harmonic Measurer[D]. Changsha: Hunan University,2007:52.

[4] 孟凡光.基于DSP的磁盘阵列的研究[D].哈尔滨:哈尔滨工程大学,2004:26-33.

MENG Fanguang. Research of Disk Array based on DSP[D]. Harbin: Harbin Engineering University,2004:26-33.

[5] 宋晓伟,陈伯孝.基于FPGA控制的IDE磁盘阵列设计[J].电子技术应用,2008(4):31-33

SONG Xiaowei, CHEN Boxiao. Realization for protocol of IDE by FPGA[J]. Application of Electronic Technique,2008(4):31-33.

[6] 刘兆宏,李曦.IDE接口的一种新型实现方法[J].计算机工程与应用,2007,43(7):114-116.

LIU Zhaohong, LI Xi. Realization Method of IDE Interface[J]. Computer Engineering and Application,2007,43(7):114-116.

[7] 杨晓飞,沙涛,黄锦安.基于Nios Ⅱ的硬盘存储系统硬件设计[J].计算机工程与设计,2009,30(6):1041-1403.

YANG Xiaohui, SHA Fei, HUANG Jinan. Design of Hard disk Storage System based on Nios Ⅱ[J]. Computer Engineering and Design,2009,30(6):1041-1403.

[8] Altera Corporation. Cyclone Ⅳ Device Handbook,2011:1-12.

[9] 赫建国,倪德克,郑燕.基于Nios Ⅱ内核的FPGA电路系统设计[M].北京:电子工业出版社,2010(4):145.

HE Jianguo, NI Deke, DENG Yan. The FPGA Circuit Design based on Nios Ⅱ Kernel[M]. Beijing: Publishing House of Electronics Industry,2010(4):145.

[10] 王海燕.嵌入式综导系统数据存储管理技术的研究与实现[D].哈尔滨:哈尔滨工程大学,2008:45-49.

WANG Haiyan. Realization and Research of Data Storage and Management on Embedded Intergrated Navigation System[D]. Harbin: Harbin Engineering University,2008:45-49.

[11] 胡鉴.固态硬盘中ATA协议的研究及其FPGA实现[D].广州:华南理工大学,2010:18.

HU Jian. Research and FPGA Implementation of ATA Protocols for SSD[D]. Guangzhou: South China University of Technology,2010:18.

收稿日期:2015年10月8日,修回日期:2015年11月24日

作者简介:孙昕,男,硕士,高级工程师,研究方向:水声测量技术。张世海,男,助理工程师,研究方向:水声测量技术。

中图分类号TP274.7

DOI:10.3969/j.issn.1672-9722.2016.04.045

Underwater Data Storage System Based on FPGA

SUN XinZHANG Shihai

(Unit 96, No. 91439 Troops of PLA, Dalian116041)

AbstractTo solve the problems that in underwater multi-channel data acquisition system cannot satisfy the high speed data rate and large storage capacity with no computer, a disk array storage system based on FPGA is designed. IDE communication and controller run on a SOPC system based on Altera’s Cyclone IV FPGA. The parameters detecting and initialization of the hard disk are accomplished, together with the reading and writing based on PIO mode. By adopting the design of IDE/SATA dual interfaces and dual channels, the system is based on the theory of disk array storage, and FATFS file system is utilized for file management, which enables the promoting of augment ability and flexibility of the system when the data is backed up at the same time

Key Wordsdata storage, RAID, FPGA, SOPC, IDE