基于OpenVPX双冗余交换系统设计

四川九洲电器集团有限责任公司 夏 鸿

基于OpenVPX双冗余交换系统设计

四川九洲电器集团有限责任公司夏鸿

随着电子信息技术的飞速发展,开放式体系架构日趋成熟,综合化设计的趋势越来越明显。电子设备系统架构设计更多的采用高速总线和硬件模块扩展的方式,用以快速系统实现、能力提升、降低成本。基于OpenVPX双冗余交换系统的设计,采用16槽双冗余机架,以RapidIO、千兆以太网为基本交换数据总线,具有稳定性好、传输速率高、计算能力强、扩展配置灵活的特点。

OpenVPX;双冗余交换;RapidIO

近几十年来电子设备的发展正朝着标准化、模块化、更高的传输总线带宽、更好的扩展和灵活配置能力、以及并行计算性能的方向发展,VPX采用RapidIO高速串行总线增加了传输带宽,集成了更多的IO和扩展格式布局。2010年VITA(VME国际贸易协会组织)成员在VPX基础进一步拓展发布了OpenVPX,带宽进一步提高、具备多交换网络模式,统一规定了节点、背板和模块三大类的标准架构。

1.OpenVPX总线协议概述

OpenVPX主要通过背板互连拓扑设计,从传输系统逻辑上划分为5个部分[1]:

管理平面(Management Plane):用于组织和管理标准的硬件资源,管理层的电源可以设计为独立电源,与主电源(供电系统中的各板)分开,这样就可以实现管理层对各板的电源控制。

控制平面(Control Plane):此层应用低延迟、中等带宽、基于数据包的通信模式。OpenVPX通过控制通路和数据通路区分开,保证各通路的带宽,并且一个通路的冲突不会影响到另一个通路。

数据平面(Data Plane):数据传输层在板间以及处理板与底板间构建了一套高宽带,低延迟的数据通路,数据传输层可选择单星状或双星状。RapidIO和10GB以太网均会应用到数据传输层。

扩展平面(Expansion Plane):扩展层主要把主控板与若干紧耦合的处理板或IO板连接起来,与主控板紧耦合的处理板不能独立于主控板工作。PCIe或其他高速通信协议会应用于扩展层,扩展层需要使用低延迟、高带宽的通道支持其通信。

公共平面(Utility Plane):为系统提供最基础的服务,如:电源供给、参考时钟、系统复位等低级别信号。

2.双冗余交换系统设计

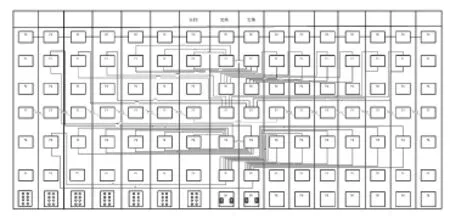

本系统硬件架构由满足总线标准的总线背板、射频/中频采样单元、信号处理单元、双交换模块组成。总线背板上设置了16个标准板卡槽位,16个槽位标准配置为2个交换模块、6个射频/中频采样模块、1个主控模块、6个信号处理模块、2个备用槽位。信号处理模块可互换、中频采样模块可互换、交换模块可互换。系统采用基于交换节点为中心的互连拓扑结构,结构简单。单交换模块、信号处理或者射频/中频采样发生故障时系统均可正常工作。该系统中有三种总线,数据总线、控制总线和管理总线,其中数据总线采用RapidIO总线、主要传输对数据速率及实时性要求高的数据,如采样数据、信道控制数据;控制总线采用千兆以太网总线,总线采用集中交换式拓扑实现,主要是低速控制信息,如控制命令、软件动态加载切换等;管理总线采用I2C实现机内所有模块的管理,为低速总线,主要实现各单元模块运行状态、故障报警、实时温度的上报等。

为了增加系统设计的可靠性和可行性,参照ANSI/VITA 65-2010 OpenVPX标准进行设计,具体型号选择BKP6-CEN16-11.2.2n,由于单交换模块设计了2组MT光口对外传输交互,交换接插件连接数量受限,因此仅实现14个模块互连及2个模块箱内备份。机箱内部模块互连遵照标准规范设计为6U模块,采用双交换方式实现模块的互连。

图1 系统拓扑图

信号处理及中频采样模块采用4x 的RapidIO总线为数据总线,通过交换模块实现互连,单通道速率设置为3.125Gbps[2];标准的信号处理模块与中频采样模块之间采用RocketIO串行流水互连拓扑;信号处理及中频采样模块的控制总线采用集中交换式星型拓扑千兆以太网互连;中频采样模块的采用8个12#射频接触件,隔离度大于90dB[3];交换模块的光纤接触件选择MT形式,可通12路光信号,插入损耗小于1.5dB,误码率不大于10-12。

3.核心板卡设计

OpenVPX定义了交换模块(Switch)、负载模块(Payload)、外围模块(Peripheral)等模块类型。本平台中核心的是交换模块设计,该交换模块原理设计如图2所示:

图2 交换模块设计原理图

PPC选用的CPU是飞思卡尔的P2020双核处理器。P2020可实现单线程极高性能功耗比,单片功耗小于10W,具备e500内核,运行频率高达1.2GHz,具有3个增强型三速以太网控制器,4个SerDes,可实现两路RapidIO。

SRIO交换选用IDT公司的CPS-1432,该芯片基于RadpidIO2.1规范,共有32路串行通道,可灵活配置为8×4、12×2、14×1的端口工作方式,端口数量最多可配置为14个,芯片内部交换带宽达160Gbps,提供无阻塞的全双工交换能力。

以太网选用BCM5396,该芯片支持16端口三层千兆以太网交换,PPC通过一个etsec与BCM5396的IMP口交换,PPC通过SPI操作BCM5396的内部寄存器。

4.信号完整性设计

信号完整性(SI)是指信号在电路中以正确的时序和电压做出响应的能力。从广义上讲,信号完整性问题主要表现在五个方面:延迟、反射、串扰、同步切换噪声(SSN)和电磁兼容性(EMI)[4]。在进行电路版图设计前,利用EDA技术和高速电路仿真设计理论,对电路中的关键信号进行信号完整性分析,并为版图设计提供约束条件,以此作为PCB版图布局、布线设计的依据。在信号完整性分析的基础上进行版图设计将大大减少硬件调试过程中对电路的修改与重新制作过程,缩短产品开发周期,降低开发风险和成本。

本系统方案中,板内板间传输速率较高,需进行信号完整性仿真分析。仿真工具采用Cadence对器件进行建模。同时在版图布局中对线路拓扑进行约束,如DDR时钟采用菊花链拓扑形式;数据总线和地址总线蛇行线作分组等长处理。元器件布局也进行约束,如开关电源距离数据总线远,降低EMI对总线上信号沿干扰。

5.结论

本文设计基于OpenVPX双冗余交换系统,通过对OpenVPX总线标准的架构、组成原理的分析,构建了一个双冗余16槽的系统平台。该平台具备高的传输总线带宽、良好的冗余备份能力、可灵活配置,具有通用化、系统化、模块化的特点。该平台可满足大部分电子设备系统要求,可广泛用于雷达、电子对抗、图像处理等高性能的信号处理系统中。

[1]ANSI/VITA65-2010,OpenVPX System Specification [S].2010

[2]Sam Fuller.RapidIO嵌入式系统互连[M].王勇,译.北京:电子工业出版社,2006.

[3]中航光电.VPX系列模块化加固型混装连接器[M].2015.

[4]夏军成.高速数字设计中的信号完整性问题[J].舰船电子对抗,2003,(04):10-11.