基于FPGA的多通道数据采集系统的设计

史籍, 常越, 李海国

(上海交通大学 电子信息与电气工程学院,上海 200000)

基于FPGA的多通道数据采集系统的设计

史籍, 常越, 李海国

(上海交通大学 电子信息与电气工程学院,上海200000)

介绍了一种基于MachXO2 4000ZE系列的FPGA芯片和模数转换芯片AD7356的多通道数据采集系统,采样率最高可达到5Msps。系统采用多个AD芯片来实现多路模拟量的实时采集。通过verilog编程语言实现FPGA芯片对AD转换的时序控制。FPGA内嵌的双口RAM作为数据缓存器来存储转换结果。通过FPGA控制单元对AD转换部分和数据缓存部分的控制可实现数据采集与数据输出的同时执行。阐述了系统的构成以及各个部分的工作原理,着重分析了FPGA控制策略和数据缓存的实现,并使用Modelsim仿真软件进行仿真与分析。

FPGA;AD7356;多路采集;A/D转换;数据缓存

0 引 言

在电力系统微机继电保护装置中,多通道数据采集系统是重要的组成部分[1]。传统的多通道数据采集系统存在一定的缺陷:每次只能进行单通道的AD转换,当第N路信号转换完毕后才可以进行第N+1路信号的转换[2],或者数据的采集与传输不能够同时进行,这样造成了转换效率不高的问题。传统的AD转换芯片还具有控制信号多,控制时序复杂的弊端。

在本文设计的系统中,由于FPGA集成度高,时序控制精确,片上资源丰富,可灵活对其编程,实现各种逻辑器件功能[3],因此采用FPGA作为主控芯片。AD转换芯片采用AD7356,该芯片可同时采集并且转换两路模拟信号,运用多片AD7356可以对多路信号并行采集和转换,提高了AD转换效率;AD7356还可同时输出两路转换结果,结合FPGA内部的双口RAM,可实现多个通道转换结果的缓存和并行读取[4]。利用系统的工作原理,可将现有规模的系统扩展为拥有更多转换通道数和转换精确度的数据采集系统。系统的转换效率高并具有较好的可靠性,因此确保了继电保护装置准确、快速地动作。

1 系统的结构

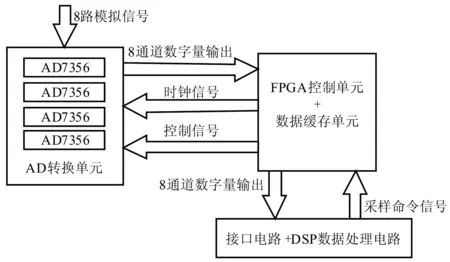

系统的结构框图如图1所示。

图1 系统的结构框图

本文设计的系统由AD转换单元、FPGA控制单元、数据缓存单元、接口电路以及DSP数据处理电路组成。

FPGA控制单元接收DSP的启动信号,并且为AD转换单元和数据缓存单元提供时钟信号和控制信号[5]。本系统采用的FPGA为Lattice公司MachXO2 4000ZE系列器件,该系列器件采用65 nm闪存工艺技术,工作电源电压标称值为1.2 V,支持高达60 MHz的系统性能,可提供低至19 μW的功耗,拥有4 320个查找表(LUTs)和34 KB的分布式内存(Distributed RAM)。

AD转换单元采用4片AD7356芯片同步工作,AD7356是Analog Devices公司出品的转换精度12位的逐次逼近型ADC,以5 Msps采样速率工作时功耗仅35 mW。AD转换单元接收经过调理电路处理后的交流模拟信号,每片AD7356可同时对两路差分模拟信号进行采样和转换,并且两路转换结果可以同时串行输出。FPGA控制单元向所有的ADC提供统一的时钟信号和控制信号,保证了8路模拟信号的同步采集和转换。

数据缓存单元由FPGA内部的双口RAM构成,通过IPexpress软件工具可以任意设置双口RAM的数量和大小。每一个RAM块用来存储一路信号的转换结果[6],分为A和B两部分,当转换结果写入到子块A(B)时,子块B(A)输出上次转换结果,两个子块交替工作[7]。本系统共设置8个双口RAM块,分别存储8路转换结果。FPGA控制单元向所有RAM块提供统一的时钟信号、控制信号以及使能信号,因此8路转换结果被同时写入到8个RAM块的子块A(B),并且8个RAM块的子块B(A)内的转换结果被同时输出。

DSP数据处理电路通过接口电路读取缓存后的AD转换结果,并且对数据做进一步处理。同时,DSP数据处理电路给FPGA控制单元发出系统启动信号。

2 FPGA控制与数据缓存的实现

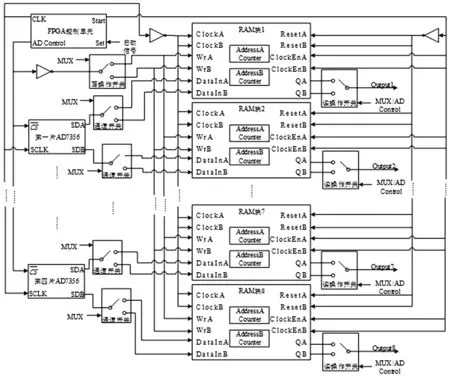

FPGA控制单元与AD转换单元以及数据缓存单元的逻辑连接如图2所示。

图2 FPGA与AD7356的逻辑连接图

2.1FPGA控制单元

FPGA控制单元由两部分组成:(1) 主控逻辑部分;(2) 通道开关、读/写操作开关。

图3 AD7356时序图

由于从AD转换单元输出的转换结果在ClockA/ClockB的上升沿之后才可以被写入到数据缓存单元,因此CLK需要通过反相器再输入到ClockA/ClockB端,在转换结果被写入到数据缓存单元时要保证WrA/WrB为高电平,因此AD Control信号需要通过反相器再输入到WrA/WrB端。

通道开关以及读/写操作开关:MUX为一位的寄存器输出,当控制信号AD Control产生下降沿时,MUX寄存器加1。

通道开关:当MUX=1时,8个通道开关选通各自RAM块的DataInA端;当MUX=0时,8个通道开关选通各自RAM块的DataInB端。

写操作开关:当MUX变为1时,AD Control信号经过反相器输入到WrA端,WrA先获得高电平,加之8个RAM块的DataInA端被同时选通,因此8路转换结果被同时写入到各自RAM块的子块A,写入完毕后AD Control产生上升沿,因此WrA变为低电平(不写入数据到子块A),直到MUX的值再次从0跳变到1时,WrA才重新变为高电平;当MUX变为0时,AD control信号经过反相器输入到WrB端,WrB先获得高电平,加之8个RAM块的DataInB端被同时选通,因此8路转换结果被同时写入到各自RAM块的子块B,写入完毕后AD Control产生上升沿,因此WrB变为低电平(不写入数据到子块B),直到MUX的值再次从1跳变到0时,WrB才重新变为高电平。

读操作开关:AD Control产生上升沿时,根据上升沿时刻的MUX值判断输出子块A还是子块B中存储的转换结果。如果AD Control上升沿时刻的MUX为1,则从QA端输出子块A存储的转换结果;如果AD Control上升沿时刻的MUX为0,则从QB端输出子块B存储的转换结果。

2.2数据缓存单元

一个RAM块有两个数据输入端,分别为DataInA和DataInB,某时刻只有一个输入端输入数据;有两个数据输出端,分别为QA和QB,某时刻只有一个输出端输出数据。如果当前通道开关选中DataInA(DataInB),表示在时钟信号CLK的激励下,AD7356往子块A(B)写入转换结果,在往子块A(B)写入的同时,QB(QA)输出子块B(A)内存储的上一次的转换结果供DSP读取。

子块A(B)由14位构成,用来存储一次转换结果,一个地址对应一位数据。每个RAM块内部实现了两个地址寄存器AddressA Counter和AddressB Counter,分别对应子块A和子块B。在写入子块的过程中,被写入子块的Wrx(x=A,B)=1,ClockA/ClockB的上升沿(SCLK的下降沿)之后一位数据被写入到当前地址寄存器指向的存储空间里,每当往子块里写入一位数据后,对应子块的地址寄存器的值加1;在读取子块的过程中,被读取子块的Wrx(x=A,B)=0,ClockA/ClockB的上升沿(SCLK的下降沿)之后输出当前地址寄存器指向的存储空间里的一位数据,每当输出一位数据后,对应子块的地址寄存器的值加1。

当地址寄存器内的值加到13时,表示子块内写满14位的转换结果或者子块输出14位转换结果,地址寄存器清零,进行下一轮读/写操作。数据缓存单元的写操作流程如图4所示,读操作流程如图5所示。

图4 数据缓存单元的写操作流程

图5 数据缓存单元的读操作流程

3 系统工作过程

图6显示了对一个RAM块写入与读取的过程,系统的8个RAM块按照相同的节拍同时工作。

图6 一个RAM块的工作过程

图6中实线框表示写入数据到子块,虚线框表示读取子块内的数据,框内的数字代表当前的地址,打叉的框为空闲区域(不执行写入操作和读取操作)。t0至t1的时间长度为执行写操作时地址的有效时间,t1至t2的时间长度为执行读操作时地址的有效时间,两个时间长度相同且等于一个SCLK周期时间。日字格表示数据有效的时间域,数据在日字格的时间范围内被写入或读取,日字格的左边沿代表SCLK信号的下降沿(ClockA/ClockB上升沿)时刻。

t3时刻AD Control产生下降沿,MUX值变为0,开启对子块B的写入操作,在t4时刻,14位的转换结果被全部写入到子块B内,AddressB清零;另外在t4时刻,AD Control产生上升沿,而此刻的MUX=0,因此t4时刻以后输出子块B内的转换结果供DSP读取,t6时刻DSP刚好读完14位的转换结果。在对子块B执行读取操作的同时,写入新的转换结果到子块A中:在t5时刻,AD Control产生下降沿,MUX值变为1,写入新的转换结果到子块A,在t7时刻,14位的转换结果被全部写入到子块A内,AddressA清零;另外在t7时刻,AD Control产生上升沿,而此刻的MUX=1,因此t7时刻后输出子块A内的转换结果供DSP读取,t10时刻DSP刚好读完14位的转换结果。在对子块A执行读取操作的同时,对子块B执行写入操作:t9时刻AD Control产生下降沿,MUX值变为0,写入转换结果到子块B,接下来的流程与上文讲述的相同,两个子存储块交替工作。

在上述过程中,t6时刻子块B内的14位转换结果读取完毕,为了保证DSP能够可靠地读取连续两次的转换结果,这时需要插入一个空闲段,空闲段从t6时刻开始至t7时刻结束,持续时间为一个SCLK周期时间长度,在空闲期间,虽然仍然有一位数据从子块输出,但是DSP视其为无效数据,直到t7时刻开始再次读取子块A内的转换数据;同理,在t7时刻,14位转换结果全部写入到子块A内,为了保证可靠地写入连续两次的转换结果,这时需要插入一个空闲段,空闲段从t7时刻开始至t8时刻结束,持续一个SCLK周期的时间长度,在空闲期间,WrA=WrB=0,不写入数据到数据缓存单元,t8时刻开始再次写入数据到子块B。

通过分析系统工作过程看出,每一个子块按照:写-读-空闲2个SCLK周期-写-读-空闲2个SCLK周期……的节拍工作。对一个RAM块的写操作执行过程是:写入转换结果-空闲一个SCLK周期-写入新的转换结果-空闲一个SCLK周期……对一个RAM块的读操作执行过程是:读取转换结果-空闲一个SCLK周期-读取新的转换结果-空闲一个SCLK周期……连续两次写操作或读操作之间只有一个SCLK周期的时间间隔。

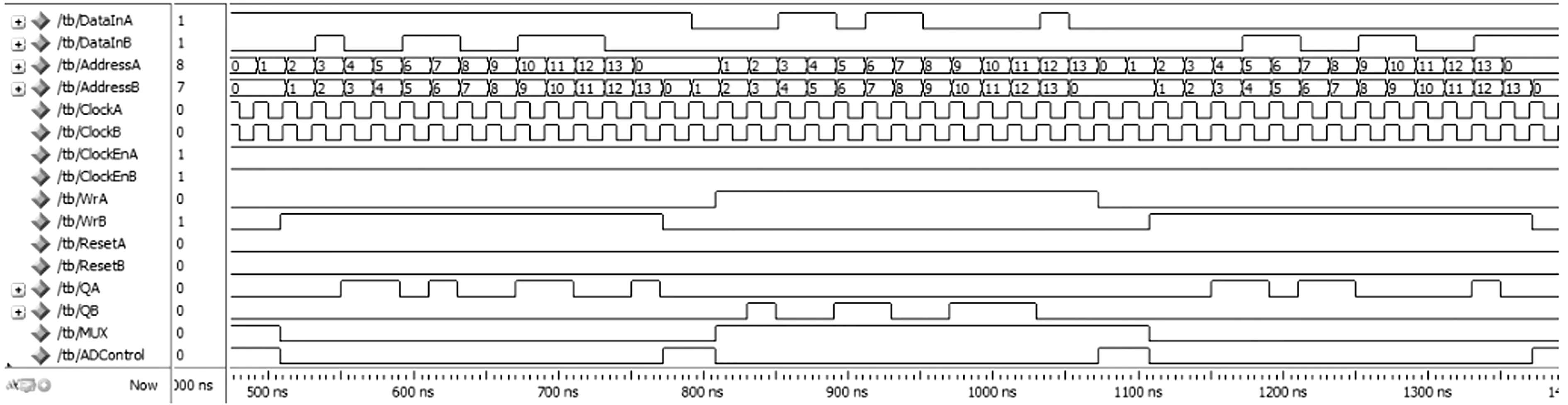

4 系统仿真

根据设计,在Modelsim 10.1a软件中进行仿真,图7为正在工作着的系统中某个RAM块的时序仿真图。图中显示的部分对子块A执行读-写-读操作,对应的数据分别为:00 011010011001、00 011011000010、00 011011000010;对子块B执行写-读-写操作,对应的数据分别为:00 100110011100、00 100110011100、00 001100110011。

图7 正在工作的RAM块的时序仿真图

从仿真波形上看出,在FGPA的时钟信号和控制信号的作用下,可以有效地写入转换结果到RAM块,并且RAM块能够正确输出转换结果供DSP读取。

5 结束语

本文采用了FPGA芯片为主控制器,对8路模拟信号进行同时采集,通过FPGA芯片内部的RAM对转换结果进行缓存,利用每个RAM块有双通道的特点,实现了数据写入与读取的同时进行,提高了系统工作效率。由于IPexpress软件可实现对FPGA内部RAM的大小与数量的任意设置,因此当实际需要测量的交流电压、电流信号的数量增多时,或者对测量结果的精确度提出更高的要求时,本系统可升级为拥有更高精确度与通道数的AD采集转换系统。本方案设想与系统的仿真结果一致,证明了系统的可行性。

[1] 宋锋, 孙未. 基于FPGA的数据采集系统的设计[J]. 信息技术, 2009,23(10):118-120.

[2] 王俊, 郑焱, 王红, 等. 基于DMA的并行数字信号高速采集系统[J]. 电子应用技术, 2010,36(3):42-44.

[3] 张耀政, 王文廉, 张志杰. 基于单路FIFO的多通道同步采集存储系统的研究[J]. 电力系统保护与控制, 2010, 38(8):100-104.

[4] 杨林楠, 李红刚, 张丽莲,等. 基于FPGA的高速多路数据采集系统的设计[J]. 计算机工程, 2007, 33(7):246-248.

[5] 左丽霞, 邓芳芳, 卢山. 基于DSP的高速数据采集系统设计与实现[J]. 电力系统保护与控制, 2010, 38(13):108-112.

[6] 孙炎辉, 丁纪峰. 基于FPGA的数据采集控制模块设计[J]. 现代电子技术, 2009,33(22):189-191.

[7] 梁成志, 王诚, 赵延宾. LATTICE FPGA/CPLD设计(基础篇)[M]. 北京: 人民邮电出版社, 2011.

Design of the FPGA-based Multichannel Data Acquisition System

SHI Ji, CHANG Yue, LI Hai-guo

(School of Electronic Information and Electrical Engineering, Shanghai Jiao Tong University, Shanghai 200000, China)

This paper presents a multichannel data acquisition system based on MachXO2 4000ZE series FPGA chip and A/D conversion chip AD7356, with a sampling rate up to 5 Msps. The system adopts several AD chips to achieve real-time acquisition of multichannel analog quantity. Verilog programming language is used to realize FPGA chip’s timing control over A/D conversion. FPGA- embedded dual-port RAMs are used as data caches to store conversion results. Data acquisition and data output are performed simultaneously through FPGA control unit’s control over A/D conversion section and data caching section. Furthermore, this paper describes the structure of the system and the principle of each part, analyzes the FPGA control strategy and realization of data caching, and uses Modelsim simulation software for simulation and analysis purpose.

FPGA; AD7356; multichannel acquisition; A/D conversion;data caching

10.3969/j.issn.1000-3886.2016.01.006

TP930.12

A

1000-3886(2016)01-0015-04

史籍(1990-),男,内蒙古赤峰人,硕士生,研究方向为电力电子技术。常越(1959-),男,辽宁沈阳人,工学博士,副教授,研究方向为电机控制与特种电源研究;李海国(1990-),男,重庆人,硕士生,研究方向为嵌入式系统的研发。

定稿日期: 2015-11-19