AXI总线加密模块的设计与验证

贺依盟,周亚军

(杭州电子科技大学自动化学院,浙江 杭州 310018)

AXI总线加密模块的设计与验证

贺依盟,周亚军

(杭州电子科技大学自动化学院,浙江 杭州 310018)

结合信息安全的需求以及SoC技术的发展,设计了一种基于AES加解密算法的AXI总线加密IP,达到从CPU到slave的整个数据通路的加解密目的,实现SoC内部的端到端加密.其中通过内置多个FIFO,分别在读写通道缓存CPU发出的AXI Burst传输,保证CPU发出的总线传输可以被顺序的加解密处理.在AES算法实现方面,完成了ECB,CTR两种便于并行处理的加密模式.在读写通道分别加入AES实现模块,保证加解密操作的并行处理.同时构建结构化的UVM验证平台,结合APB和AXI的VIP来实现对该IP的随机约束和覆盖率分析,最终通过Synopsys的VCS仿真工具完成功能验证.

AXI加密;AES-CTR模式;验证VIP;统一验证方法学

0 引 言

随着集成电路的发展,单位晶圆上可集成的晶体管越来越多,可实现的功能越来越多,各式各样的知识产权核(Intellectual Property,IP)开始加入到片上系统(System On Chip,SoC)中.为保证数据通信的安全性,SoC中数据加密技术的研究成为重点.ARM公司早在2008年便提出了Trust Zone技术,在芯片中建立安全系统的概念,并在其处理器和总线矩阵IP中实现了对该技术的支持,在实际芯片设计中得到了广泛的应用[1].已有的运用高级加密标准(Advanced Encryption Standard,AES)加密的IP多是针对某一具体外围设备的实现,作为总线矩阵的从设备端(Slave)来集成在SoC中,这样的IP只能处理单一模块的加密,利用率不高[2].在加密IP中,由于加解密的操作,数据的处理速率会受到很大的影响,所以模块内部需要进行相应的处理来提高数据处理速率,如AXI Burst传输需要模块内部集成有缓存.IP设计时也必须考虑对AXI等数据接口总线支持,如AXI的写地址不对齐访问,需要额外的逻辑来实现.但是目前的加密IP中,都没有考虑这些方面.

本文设计了一种集成在ARM核与AXI总线矩阵之间的数据通路中的加密模块,直接对ARM核输出的AXI事务处理(Transaction)进行加密,再将加密后的事务处理通过AXI Master接口发送给总线矩阵模块.通过地址映射功能来选择性地完成对片内、片外的多个模块进行加解密处理,并支持ARM的Trust Zone技术,通过寄存器的配置和ARM核的处理器状态来限制模块的访问权限,提高芯片整体的安全性.同时为了保证本文IP设计的逻辑正确性,本文完成了基于统一验证方法学(Universal Verification Methodology,UVM)的验证平台搭建,并结合Synopsys提供的AXI和APB的验证VIP,完成对IP的功能验证.

1 AXI总线描述

AXI总线是ARM公司于2004年提出的AMBA3.0协议中的重要组成部分[3],是一种面向高性能,高带宽,低延时的片内总线,在SoC中得到了广泛的应用.AXI协议将操作分为读地址、读数据、写地址、写数据、写响应5个通道.每个通道都由一组独立信号组成,并使用双向VALID和REDAY握手机制.信息源使用VALID信号表明通道上的数据和控制信息何时有效,目的端使用REDAY信号表明何时能够接收数据.读数据通道和写数据通道都包含一个LAST信号,以显示事务处理中的最后一个数据项的传输.而且每个事务处理都会在5个通道有相应的ID号,来支持乱序传输.读写数据通道可配置自己的数据总线宽度为8~1 024位,写数据通道还包含8位的狭窄通道(wstrb)信号,对每8个数据位进行过滤,表明数据总线上哪些字节是有效的,来支持地址不对齐的Burst写操作[3].

2 AES算法描述

AES算法是美国国家标准技术协会(NIST)2001年发布的高级加密算法,用以取代DES算法,满足21世纪的数据安全需求.AES算法的数据块长度固定128位,密钥长度可以是128位、192位、256位相应的迭代次数为10,12,14.数据块包括明文和密钥都以一个4×4的矩阵为单位进行轮循环计算,矩阵的各个元素在有限域GF(28)上进行计算.矩阵元素S00…S33代表128 bit的明文数据流,每个元素表示8 bit的明文.

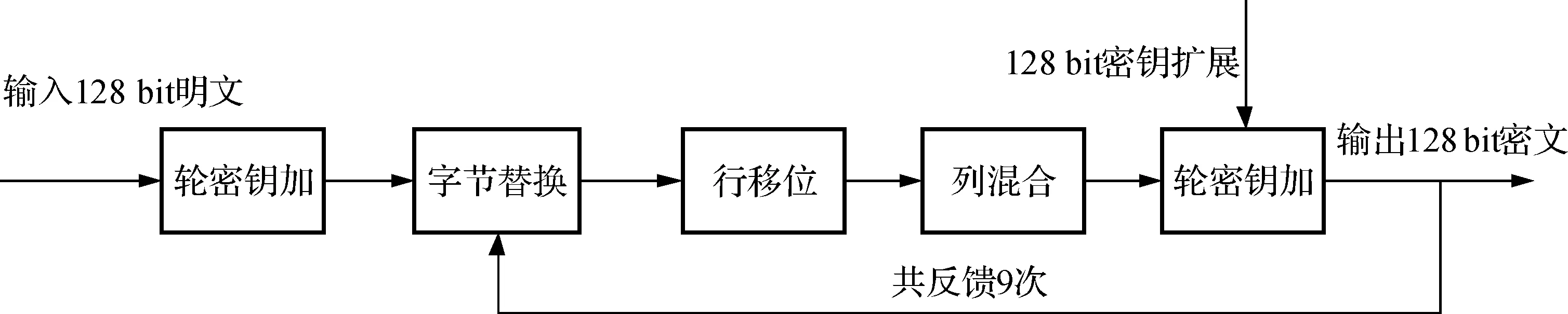

加密流程如图1所示,其中在第一轮开始之前会先进行轮密钥加,来防止直接输入明文.解密流程通过等价变换之后与加密流程相同.AES算法共有5中加密模式:ECB(Electronic Codebook),CBC(Cipher Block Chaining),CFB(Cipher Feedback),OFB(Output Feedback)和CTR(Counter),其中只有ECB和CTR支持并行计算.ECB模式对于相同的明文分组得到的密文完全一样,所以针对已知明文攻击不安全.而CTR模式即能安全地对任意长明文加密,又能通过并行技术提升加密速度[4].本文中通过配置寄存器在ECB和CTR中选择加密模式.

图1 加密流程图

2.1字节替换运算

字节替换又叫做Sboxes,是AES算法中唯一的一个非线性置换.由下面的两个可逆的变换复合而成.

1)在有限域GF(28)内取逆元,00的逆元规定为00;

2)将所得的逆元经过一个有限域GF(28)内的仿射变换.

在ASIC中,实现字节变换的途径有两个[5],一个是查找表(LUT),一个是有限域运算.其中有限域运算在求逆时需要将数据从GF(28)映射到GF(24)内,再从GF(24)映射到GF(22)内才可以进行运算,所以进行时序分析时,关键路径可能会很长,影响整体的运算速率,所以该IP通过查找表的方式来实现.

2.2行移位运算

行移位是一个线性操作,以字节为单位.在加密过程中,第1行不变,第2行左移1个字节,第3行左移2个字节,第4行左移3个字节.解密过程中类似,左移位变为右移位.

2.3列混合运算

列混合运算将状态矩阵中的列逐一与一个固定的多项式做乘积[6]:

S′(x)=c(x)·s(x)mod(x4+1),

(1)

式中:s(x)表示状态矩阵的某一列,“·”表示有限域乘法,c(x)在加密操作中的表达式为:

c(x)={03}·x3+{01}·x2+{01}·x+{02},

(2)

c(x)在解密过程中的表达式为:

c(x)={0b}·x3+{0d}·x2+{09}·x+{0e}.

(3)

在ASIC实现中,在GF(28)域中实现f(x)·x的计算过程可以用xtime函数来计算[7]:

xtime={b[6:0],1′b0}⊕(8′h1b⊕{8{b[7]}}),

(4)

式中:b[7:0]表示输入的8 bit数据.而后通过相加和迭代xtime函数的方式来实现整个列混合的操作.

2.4轮密钥加运算

在基于GF(28)中的运算中,加运算等价于异或运算[7].所以轮密钥加运算等价为将密钥矩阵与经过轮循环的状态矩阵进行按位异或运算.

3 加密IP功能描述

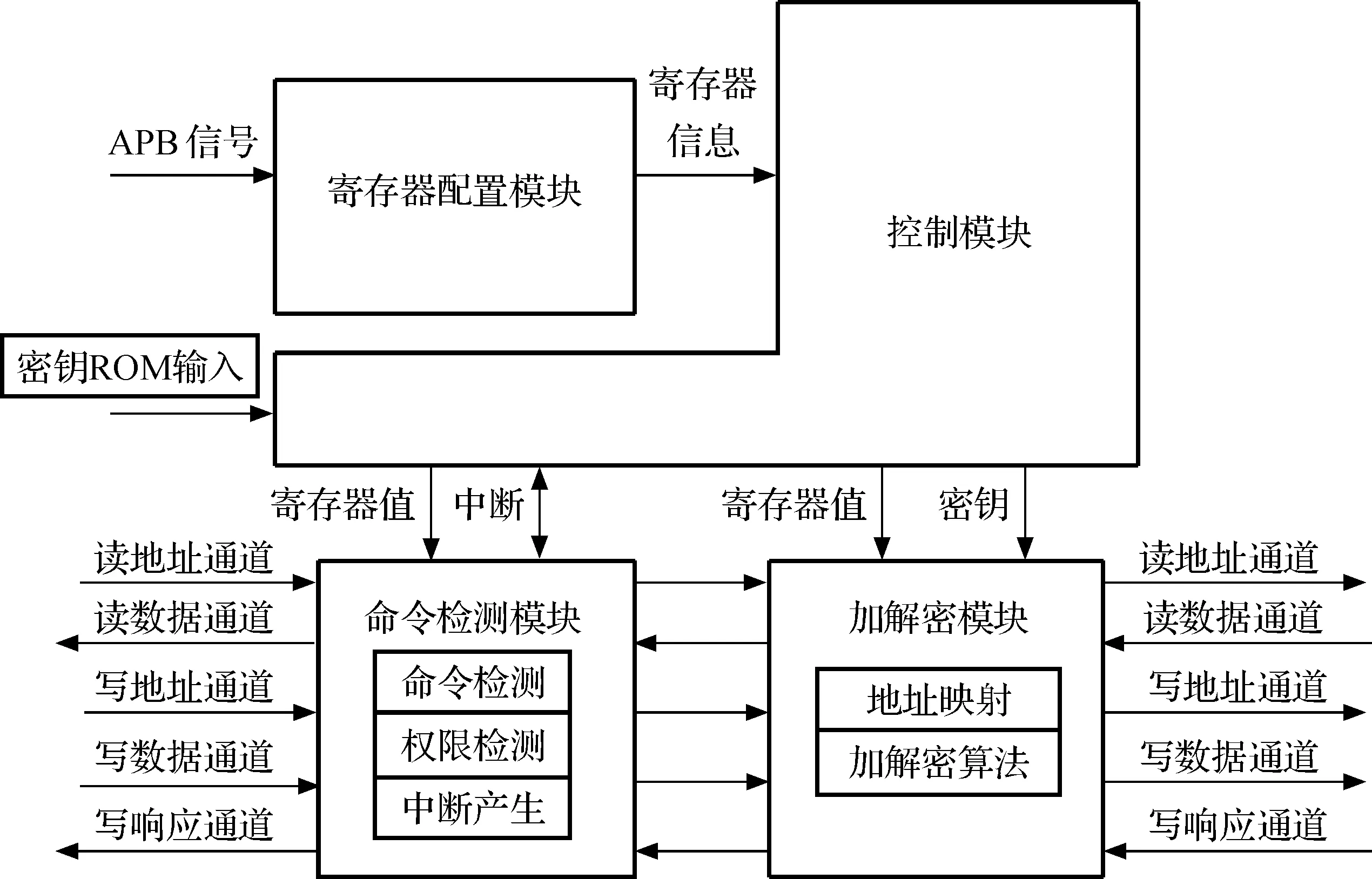

模块主要由4个子功能模块组成:寄存器配置模块(apb_logic),控制模块(ctrl_logic),命令检测模块(valid_check),加解密模块(aes_engine),如图2所示.寄存器配置模块主要实现与CPU的通信,完成自身寄存器的配置;控制模块根据寄存器的值来发出各种使能信号和接受来自命令检测模块的状态信号来置位中断或错误信号;命令检测模块主要检测CPU向该加密IP发送的AXI传输中ax_size与ax_prot信号的值,来决定总线访问是否能够被执行以及访问权限是否足够,并将结果反馈给控制模块;加密模块主要完成AES-ECB,AES-CTR的加解密和地址空间的重新映射,FIFO缓存,并实现对AXI传输中的特殊情况的处理,如Burst地址未对齐等.

因为AXI事务级传输基于Burst来传输的,所以本文中,所有处理AXI数据通道的模块都会内置FIFO,用来缓存transaction,以确保最终的结果无论是返回错误还是发送给存储器都是以Burst为单位.所有FIFO的深度都是4,也就是说最多缓存64 byte的数据,最大支持的Burst长度是4.

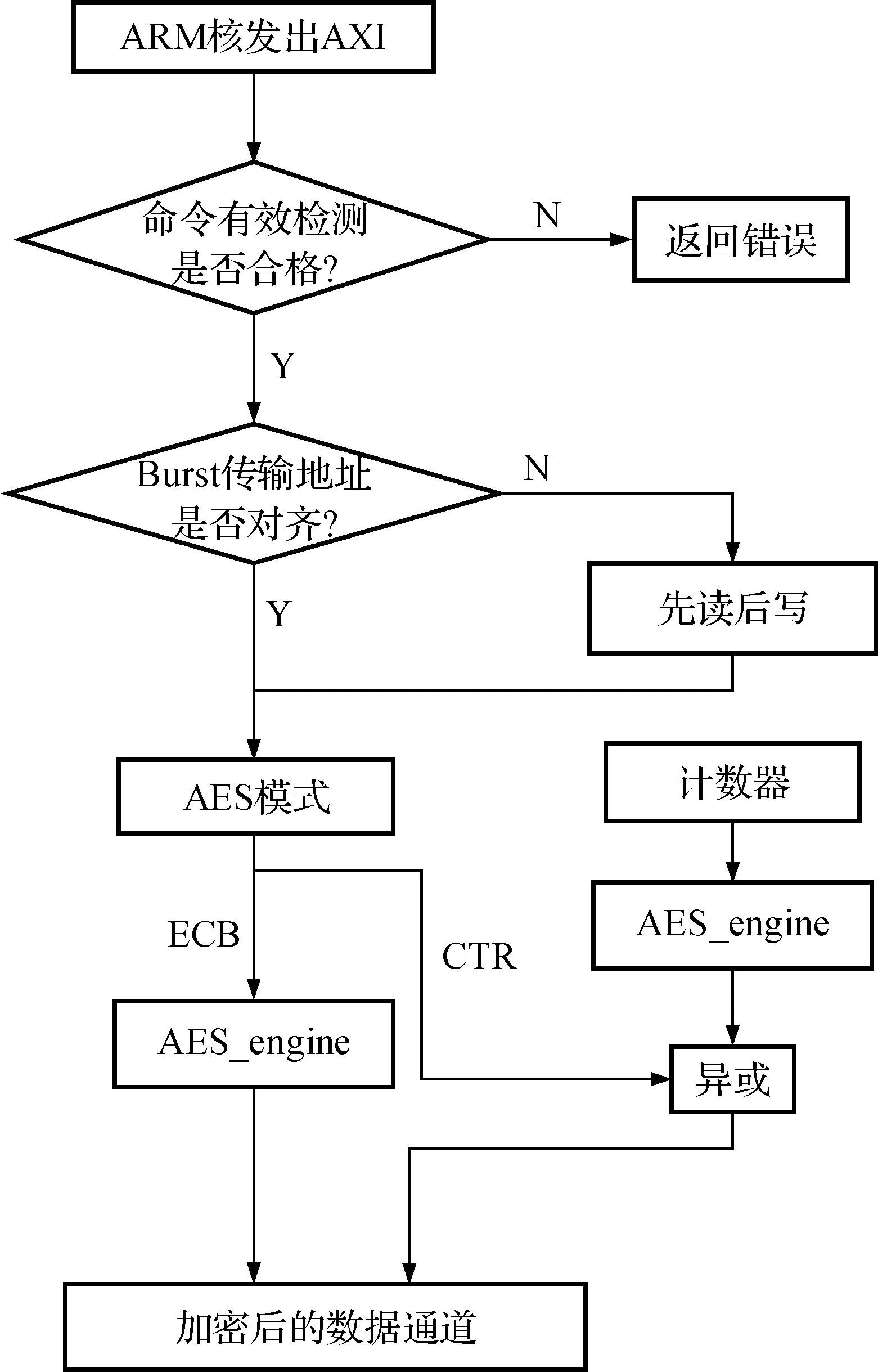

模块接受到CPU发送的AXI写操作时后的数据通道流程图如图3所示.在接收到CPU发送的不对齐的Burst传输时,模块内部针对不对齐的地址进行先读后写操作.

针对AXI的性能影响,以写数据通道信号为例来进行说明.因为AXI transaction经过FIFO锁存之后,ARM核就可以继续发送指令,不受继续的加密操作的影响.所以在ARM核发送的写操作AXI transaction中,AES对ARM核发送AXI transaction无影响.

图2 功能框图

图3 写数据通道流程图

在读数据通道中,AES加密的延时会体现在ARM核这一侧.如图4所示,在1个ID号是2c,Burst等于1的读操作中,从ARM核开始发送读地址信号到最终的收到读数据通道的last信号,共消耗了127个时钟周期.其中消耗在加密操作中的时钟只有20个时钟周期,而剩下的107个时钟周期,会因为slave设备的Ready信号无效和AXI乱序操作的特性而消耗掉.

图4 AXI读操作时钟消耗图

4 基于UVM的模块验证

UVM验证方法学由Accellera组织于2010年推出,基于SystemVerilog编写,结合了随机化约束,功能覆盖率检测,面向对象编程等特点,非常方便建立一种通用的验证平台,大大提高验证效率.UVM主体来源于OVM,同时继承了VMM中的回调函数(callback)、寄存器抽象层(Register Abstract Layer,RAL)等技术[8],使得它成为应用最为广泛且最为成熟的验证方法学.

验证平台最重要的功能在于根据验证计划产生各种各样的激励,并且观察待测试模块(Design Under Test,DUT)的输出结果,判断结果的正确性,由此再来判断DUT的正确性.一个基本的验证平台的组成部分:1)Driver,产生不同的激励施加给DUT;2)Monitor,检测DUT的输出.3)Scoreboard,比较期望值与Monitor检测到的DUT的输出值;4)Reference model,对DUT的高级语言建模,用于产生正确响应,以供Scoreboard进行比较[9].

在UVM中,对Driver的功能进行了细分,把其中负责接口信号转换的部分保留下来,而把数据产生的部分重新定义为事务(Transaction),并在其中实现数据的约束与随机化.并且新定义了2个部件:1)Sequence用来控制Transaction并且方便重载;2)Sequencer用来控制Sequence.这样只需要在Driver中只实现向它们的Sequencer发出数据请求的功能,从而将数据部分与控制部分解耦[9].

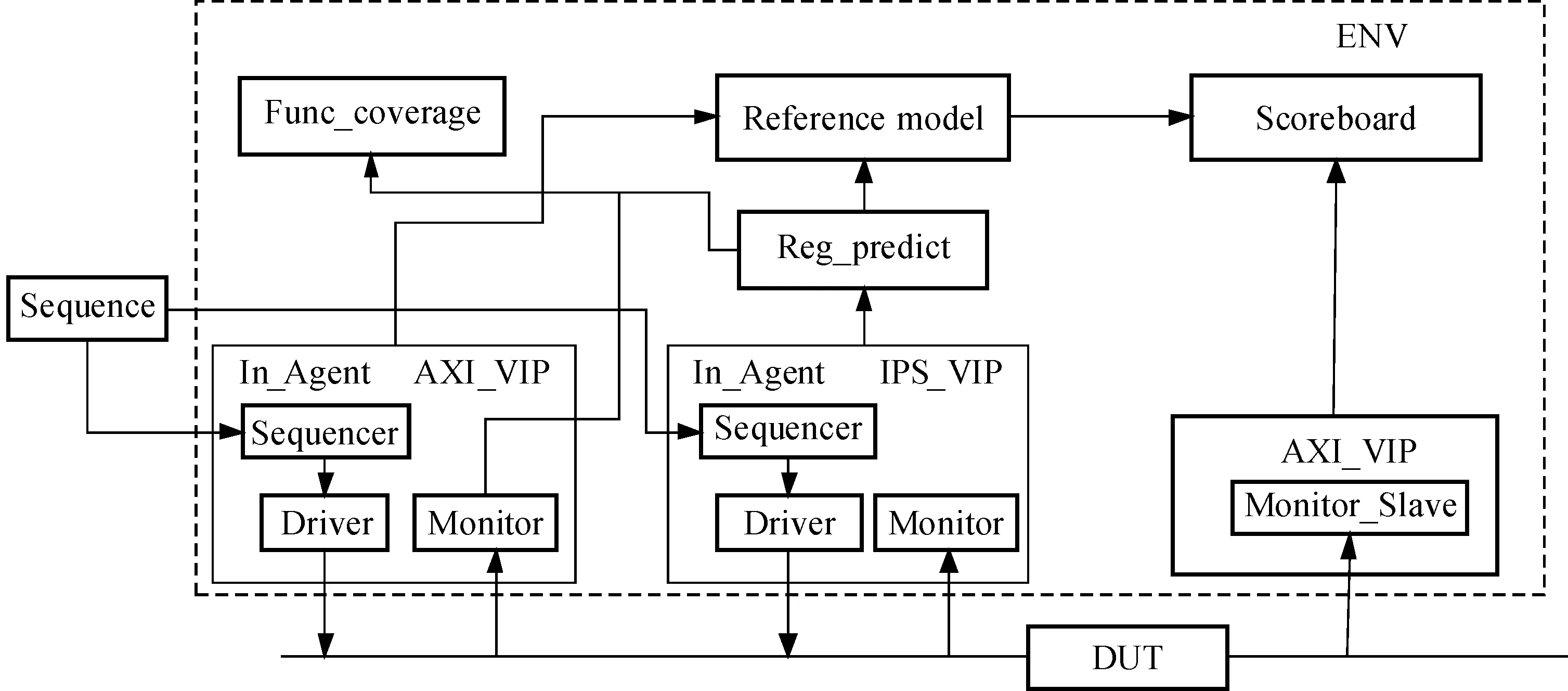

验证平台如图5所示,其中AXI_VIP负责产生AXI的Transaction和响应,即产生AES加解密的明文以及相应的操作,IPS_VIP负责通过APB总线配置寄存器,主要是配置AES的工作方式以及密钥的数值.Reference model通过Systemverilog提供的DPI来调用C语言描述的AES加解密算法.Func_coverage组件在收到AXI_VIP中Monitor、Reg_predictor组件收到IPS_VIP中Monitor发送来的信息后[10],对自定义的覆盖组进行采样,分别得到AXI传输和寄存器配置的覆盖率信息.

图5 UVM组件图

5 仿真波形及覆盖率报告

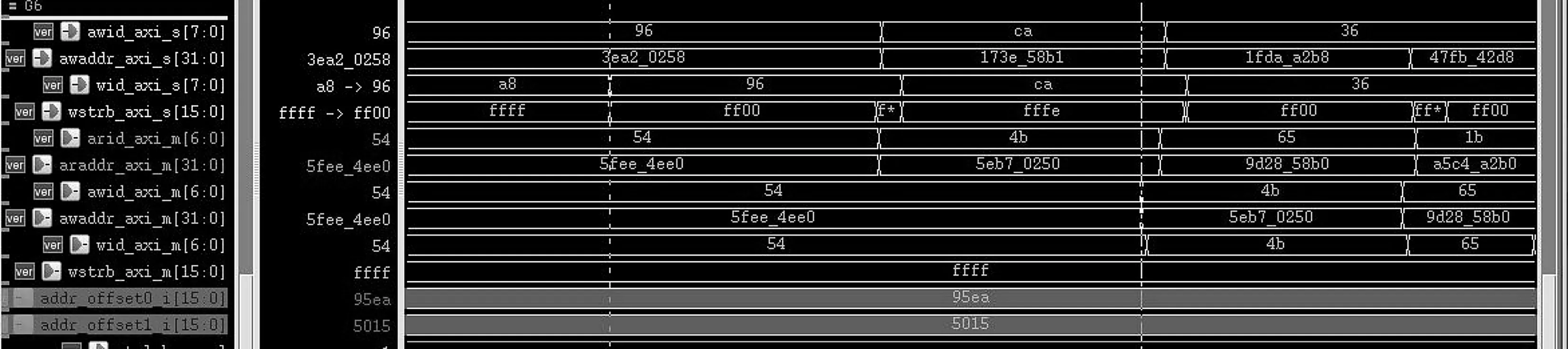

地址不对齐操作波形如图6所示.xx_s信号为CPU发出的信号,xx_m为该IP发出的加密AXI传输.加密IP在SoC中有两块地址空间,addr_offset0和addr_offset1分别对应重映射时的地址偏移量.addr_offset0对应0x1000_000—0x1FFFF_FFFF的地址空间的重映射偏移量,addr_offset1对应0x3000_0000—0x3FFFF_FFFF的地址空间的重映射偏移量.所以当CPU发出写地址0x3ea2_0258时,New_addr=0x3ea2_0258-0x3000_0000+5015_0000.而ID信号,由8 bit变为7 bit,整体右移1位,所以0x96变为0x4b.根据波形可以看出模块在处理不对齐的Burst传输时,先读后写的操作和addr、strb信号的变化.

图6 地址不对齐操作波形

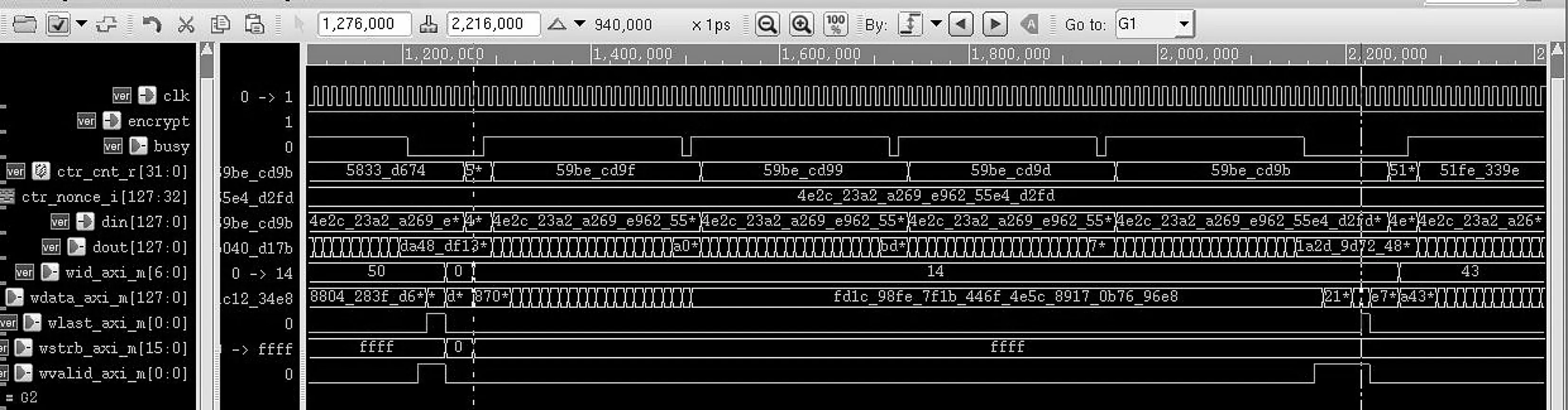

AES-CTR加密仿真结果如图7所示.模块在进行AES-CTR对Burst长度为4的写操作的加密时,明文输入信号由计数器的值和部分密钥值组成.两个时钟周期可以处理AES算法中的一轮操作.在64 byte的数据加密过程中,时钟频率为100 MHz时,共用时940 ps,仅仅写通道的数据处理速率可以达到0.545 Gbit/s.本文设计时读写分别有自己的加解密模块,可以实现读写操作的完全并行,总的数据处理速率可以翻一倍,达到1.09 Gbit/s.

图7 AES-CTR加密仿真图

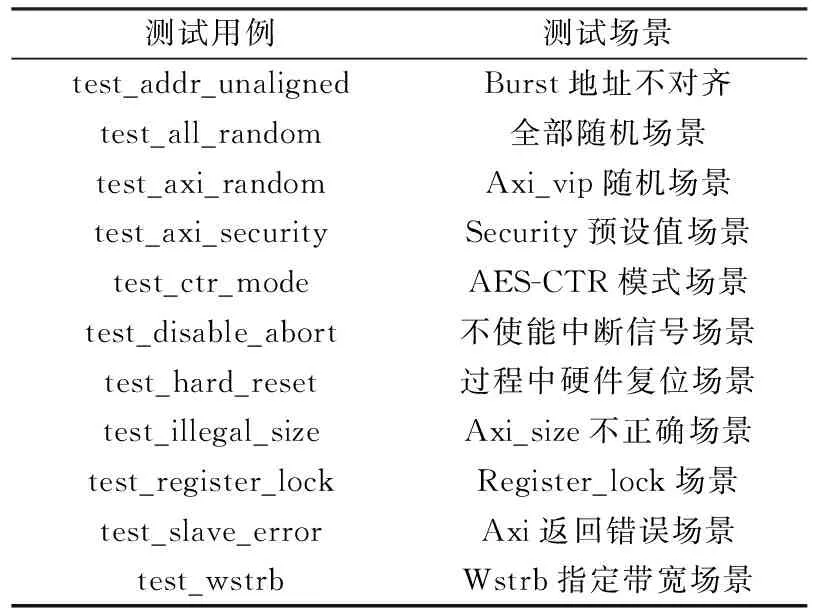

测试用例测试场景test_addr_unalignedBurst地址不对齐test_all_random全部随机场景test_axi_randomAxi_vip随机场景test_axi_securitySecurity预设值场景test_ctr_modeAES-CTR模式场景test_disable_abort不使能中断信号场景test_hard_reset过程中硬件复位场景test_illegal_sizeAxi_size不正确场景test_register_lockRegister_lock场景test_slave_errorAxi返回错误场景test_wstrbWstrb指定带宽场景

测试用例如表1所示,在做该设计模块的回归测试(regression)时,验证平台共创建了11种Testcase,在VCS中运行Testcase并收集覆盖率信息,不断调整随机约束,最终在Coverage中定义的关于寄存器配置信息的覆盖组均被覆盖,功能验证完备.LINE+COND+FSM+BRANCH的覆盖率也均在90%以上,基本完成验证要求.

6 结束语

本文采用AES算法对ARM核的AXI外接总线进行加解密,并将最终的读写操作映射到自定义的地址中,实现SoC片内端到端的加解密,达到对片内模块和外部储存器加密的目的.同时,通过内置FIFO等技术来缓存AXI的Burst传输,减小了加解密操作对AXI总线性能的影响.最终数据处理速率可以超过1 Gbit/s.而且设计组建了基于UVM的验证平台,根据验证计划创建随机约束,最终实现覆盖组的100%覆盖,代码覆盖率也达到90%以上,完成对该加密IP的验证.

[1]ARM.Building a Secure System using TrustZone Technology[EB/OL].[2009-04-01]. http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.prd29-genc-009492c/index.html.

[2]林晓牧.基于AXI接口的多模式AES加解密IP核设计[D].广州:华南理工大学,2010.

[3]COTRET P,GOGNIAT G,DIGUET J P,et al.Lightweight reconfiguration security services for axi-based mpsocs[C]//Field Programmable Logic and Applications (FPL),2012 22nd International Conference on.Oslo:IEEE,2012:655-658.

[4]费雄伟,李肯立,阳王东.基于 CTR 模式的GPU并行AES算法的研究与实现[J].小型微型计算机系统,2015,36(3):529-533.

[5]KSHIRSAGAR R V,VYAWAHARE M V.FPGA Implementation of High Speed VLSI Architectures for AES Algorithm[C]//Emerging Trends in Engineering and Technology (ICETET),2012 Fifth International Conference on.Oslo:IEEE,2012:239-242.

[6]刘晗嘉.AES加密算法IP核的设计与验证[D].上海:上海交通大学,2009.

[7]NIST FIPS PUB 197.Specification for the Advanced Encryption Standard (AES)[EB/OL].[2010-10-15].http://csrc.nist.gov/publications/fips/fips197/fips-197.pdf.

[8]吕毓达,谢雪松,张小玲.基于UVM的可重用SoC功能验证环境[J].半导体检测与设备,2015,3(40):234-238.

[9]张强.UVM实战(卷1)[M].北京:机械工业出版社,2014:1-293.

[10]JAIN A,GUPTA R.Scaling the UVM_REG Model towards Automation and Simplicity of Use[C]//VLSI Design (VLSID),2015 28th International Conference on.Bangalore:IEEE,2015:164-169.

Design and Verification of AXI BUS Encrypt Module

HE Yimeng, ZHOU Yajun

(SchoolofAutomation,HangzhouDianziUniversity,HangzhouZhejiang310018,China)

With the development of SoC technology and information safety needed, this paper provides RTL designs which encrypt and decrypt the AXI on-chip bus on-the-fly with AES arithmetic, to ensure the path to be safety from CPU to slave. The soft-IP provides the support for the AXI Burst transfer mode with some inside FIFO modules. The AES arithmetic can work in ECB and CTR mode and encrypt or decrypt paralleled. And the paper provides a structured universal verification methodology(UVM) verification platform to complete the constraint-random test and coverage analysis with the APB and AXI VIPs. At last using the Synopsys simulation tool—VCS to provide the coverage report.

AXI encrypt; AES-CTR mode; verification VIP; universal verification methodology

10.13954/j.cnki.hdu.2016.01.012

2015-05-05

贺依盟(1990-),男,浙江杭州人,硕士研究生,嵌入式系统设计.通信作者:周亚军教授,E-mail:zyj@hdu.edu.cn.

文献标识码:A

1001-9146(2016)01-0057-06