基于CPLD的多路瞬态冲击信号存储测试系统设计

周继昆,张 荣,李思忠,黄海莹

(中国工程物理研究院总体工程研究所,四川 绵阳 621999)

基于CPLD的多路瞬态冲击信号存储测试系统设计

周继昆,张 荣,李思忠,黄海莹

(中国工程物理研究院总体工程研究所,四川 绵阳 621999)

为了对水平碰撞、跌落等环境试验中的多路瞬态冲击信号进行测试,基于CPLD设计了多路瞬态冲击信号嵌入式存储测试系统;系统采用高速串行AD转换芯片作为数据采集的执行器件,实现了多路冲击信号的同步高速采集;利用铁电存储器对采集到的信号进行在线存储;设计了USB接口模块,实现了PC机与测试系统之间的通信,并在LABVIEW环境下设计了数据回读软件;经试验验证了测试系统的正确性和可靠性。

CPLD;冲击信号;存储测试

0 引言

在武器装备的生产、运输和使用过程中,通常会受到瞬态冲击的影响,对武器装备的性能有着重要影响[1]。因此,需在武器装备研制过程中通过环境试验的手段对其抗冲击性能进行考核。常见的试验方法有水平碰撞[2]、跌落[3]等,由于这类试验所产生的瞬时加速度值可达上万个g,且滑行距离长,很难在线对冲击信号进行测量,需研制嵌入式存储测试系统先将冲击信号进行采集存储,然后通过回读软件将信号回读到PC机进行分析。

文献[4]基于DSP 设计了瞬态冲击信号测试系统,但系统没有在线存储功能,且DSP最多只能实现两路信号的同步采集。文献[5]基于CPLD设计了振动信号的多路存储测试系统,但系统采样频率低,工作过程中需要单片机进行干预,系统架构较复杂,在高速瞬态冲击的作用下可靠性降低,无法满足冲击试验的测试需求。本文以CPLD作为系统控制芯片,采用ADC121 12位高速串行AD转换芯片对冲击信号进行采样,利用铁电存储器对信号进行在线存储,设计了多路冲击信号同步高速测试系统,单路采样频率可达500 kHz,而冲击信号的有效频率段在100 kHz以内[1],可满足测试需求,系统架构简介、体积小、成本低。

1 测试系统架构及工作原理

测试系统结构如图1所示,系统分为存储测试模块和数据回读模块两部分,其中存储测试模块安装在被试验件上,对试验中的冲击信号进行采集并存储到铁电存储器中,待试验完成后通过接插件与数据回读模块连接,由PC机发指令对试验数据进行读取。信号调理电路用于将加速度计输出信号调理为AD转换器可接受的电压范围,CPLD控制AD芯片对冲击信号进行采样,当检测到触发电平上升沿时,开始对信号进行预采样,当检测到加速度计输出超过设定的阈值后,开始对冲击信号进行存储,为了保证对冲击信号的采样率不小于500 kHz,CPLD必须在2 μs内完成多路信号的并行采集和存储。

图1 测试系统结构图

2 硬件设计

2.1 信号调理电路设计

本文选用的AD芯片的电压输入范围为0~3.3 V,因此,信号调理电路需将加速度计输出调理为0~3.3 V。基于AD824运算放大器的信号调理电路如图2所示,调理电路包括电荷放大、滤波、限幅等功能。

图2 信号调理电路原理图

2.2 采集与存储电路设计

根据文献[1],冲击信号持续时间段、频率高,其有效持续时间通常在100 ms以内,有效频率在0~100 kHz范围内。为了能得到较好的采样效果,本文单通道采样频率的设计指标为500 kHz。因此,选用ADC121 12位高速串行AD转换芯片作为数据采集执行器件,该芯片最高采用频率可达1 Msps,满足系统需求。为了实现数据的高速存储,本文选用FM22L16型铁电存储芯片作为存储器,该芯片容量为256 k×16 bit,可以并行写入和读取,读写周期为110 ns。根据所选的器件,数据采集与存储电路可实现4路冲击信号的并行采集与存储,存储的冲击时间可达125 ms,电路原理图如图3所示。

图3 采集与存储电路示意图

FM22L16型铁电存储芯片引脚电平为3.3 V,可直接与CPLD IO 口连接。CPLD的型号为MAXII EPM570T100I5,有丰富的IO资源,考虑到CPLD 的 IO端口的驱动能力,一个IO端口分别驱动两个AD芯片的片选信号和时钟。Triger为外部3.3 V触发电平,P1为与USB的接口。

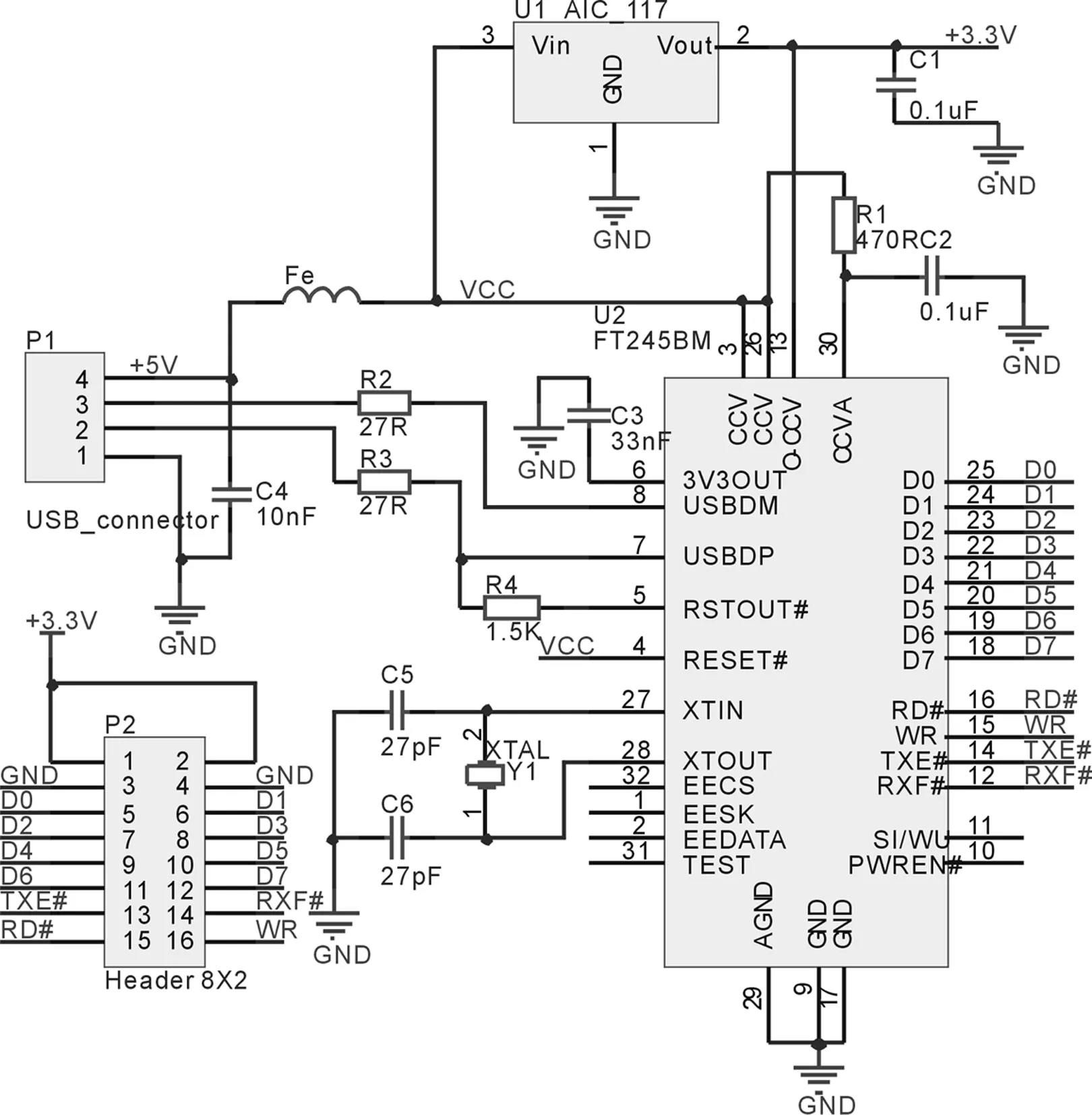

2.3 USB接口模块电路设计

USB接口模块是PC机与采集存储模块之间进行数据交互的桥梁,PC机可通过该模块向下发送指令,数采模块根据指令执行相应的操作或将存储器中的数据上传到PC机。

本文基于FT245BM芯片设计USB接口模块,FT245BM芯片是由FTDI公司推出的第二代USB接口芯片,与其他USB芯片相比,用户无需考虑固件设计以及驱动程序的编写,从而能大大缩短USB外设产品的开发周期。模块的电路原理图如图4所示,其中P2是与存储测试模块的接口。

图4 回读模块电路原理图

3 软件设计

3.1 CPLD 时序逻辑软件设计

时序逻辑软件的主要功能包括:读取PC机指令、触发电平检测、预采样、阈值判断、数据存储、读存储器、擦除存储器等。其中对存储器的读和擦除操作是根据相应的PC机指令完成了,擦除操作是对存储器的所有存储单元写00h,PC机指令定义如下。

01h:擦除存储器;

02h:读存储器的数据并上传到PC机。

时序逻辑软件采用有限状态机的方法设计,状态机流程图如图5所示。

图5 状态机流程图

系统上电后进入ST0 空闲状态,若采集存储模块与USB模块连接时,PC机可通过USB模块向采集存储模块发送指令;同时,采集存储模块也可能被触发信号激活进入数据采集状态。因此,在ST0 状态下同时对USB模块缓冲区中是否有指令和触发信号上升沿进行检测。当检测到USB模块缓冲区中有指令时,对指令进行译码,若为有效指令则执行相应操作,完成后回到ST0状态;当检测到触发信号 Triger上升沿时,系统进入预采样状态,在该状态中 CPLD 开始控制AD对加计输出值进行采样但不存储,当加速度计输出大于设定的阈值后则开始对加计输出采用存储;

在ST5中单通道采样频率为500 kHz,采用16位对数据进行存储,则4个通道采样125 ms所占的存储空间为250 k×16 bit,接近存储器的最大容量,应停止采样,进入并保持ST6 停止状态,待试验结束重新上电后进入ST0状态, PC机可读取试验数据。FT245BM、ADC121、FM22L16的时序可查阅其芯片说明手册,或相关文献[6-8],本文不再论述。

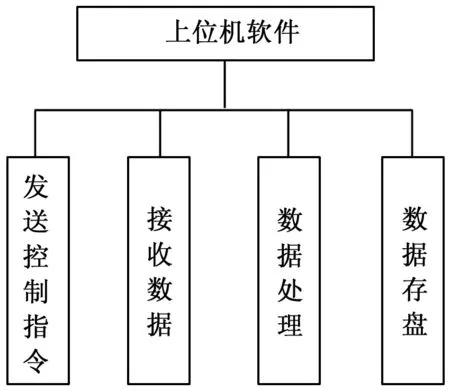

3.2 上位机数据回读软件设计

上位数据回读机软件的功能模块如图6所示。上位机软件包括:发送控制指令、接收数据、数据处理、数据存盘4个功能。发送的控制指令包括读存储器指令和擦除存储器指令,当发送完读存储器指令后,开始接收采集与存储模块中存储的试验数据。

图6 上位机软件功能模块图

数据接收完成后,可对数据显示、滤波等处理,并可将数据以TDMS格式存入计算机硬盘。上位机软件在LABVIEW环境中开发。

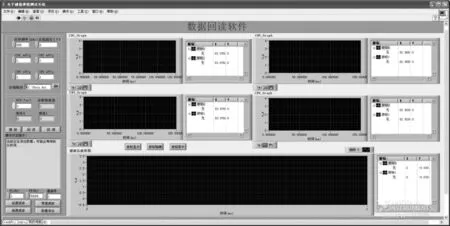

4 试验结果分析

为了验证系统可以实现4路冲击信号的并行采集存储,将一只加速度计的输出同时接入4路AD芯片输入,通过撞击冲击信号,CPLD控制4路AD同时对该信号进行并行采集存储。试验完成后,利用上位机数据回读软件将铁电存储器中的试验数据读出,如图7所示。从图中可以看出,4路AD采集到的数据基本一致,说明系统实现了4路信号的同步并行采集存储,单通道采样率为500 kHz,达到了预期效果验证了系统的正确性。

图7 试验波形(X轴—时间ms,Y轴—加速度×103 g)

5 结论

本文基于CPLD 设计了多路瞬态冲击信号存储测试系统,实现了多路冲击信号的同步高速采集存储。由于采集与存储模块采用了模块设计将该系统进行简单的叠加即可对8路、16路以及64路等多路冲击信号的存储测试。本文还基于USB接口芯片设计了数据回读接口模块,并在LABVIEW环境下设计了数据回读软件,可将测试到的冲击信号回读到PC机进行二次分析与处理。最后,通过试验验证了测试系统的正确性。

[1] 类玉富, 刘 芳, 傅鹏程. 多路瞬态信号测试系统研究[J]. 总参饱兵装备技术研究所学报, 1998, 3: 15-20.

[2] 潘建强, 刘建湖, 杨云川, 等. 水平式强碰撞冲击机冲击动响应分析[A]. 第十届全国冲击动力学学术会议[C].太原, 2011.

[3] 汤 静, 张 宇.仪器仪表运输、运输贮存环境试验中碰撞和跌落试验[J]. 自动化与仪器仪表, 2001, 2: 110-111.

[4] 胡柱龙, 徐 刚, 抑香稚. 基于DSP的瞬态冲击信号采集的研究[J]. 计算机测量与控制, 2006, 14(2): 272-280.

[5] 魏 明, 生刘莹, 警 斌, 等. 基于CPLD高速信号存储测试系统的设计[J]. 微计算机信息, 2008, 24(10): 189-193.

[6] 石波涌, 应文威, 蒋宇中. 基于FT245BM的数据采集系统设计与实现[J]. 舰船电子工程, 2010, 30(12): 125-129.

[7] 蔡江洪, 史小军, 朱 为, 等. 利用FT245BM实现FPGA与PC机的USB通讯[J]. 电子器件, 2005, 28(1): 132-137.

[8] 郑剑翔. 基于FRAM铁电存储器的可移动数据采集器[J].电子技术, 2004, 2: 7-9.

Design of Multiple Transient Impulse Signals Storage Measurement System Based on CPLD

Zhou Jikun,Zhang Rong, Li Sizhong, Huang Haiying

(Institute of Systems Engineering, China Academy of Engineering Physics, Mianyang 621999,China)

In this paper, a storage measurement system based on CPLD is designed to test the multi transient impulse signals in horizontal collision or drop test environment experiment. The system utilizes high-speed serial AD conversion chip as the implementation of the data collection device, which realized synchronization and high-speed data acquisition of multiple impulse signal. The collected signals were stored in an ferroelectric memory online. A USB interface module was design to realize the communication between the PC and test system, and the date recovery software is developed in LabVIEW environment. The experiment verified the correctness and reliability of the test system.

CPLD; impulse signals; storage measurement

2015-12-28;

2016-02-15。

周继昆(1987-),男,重庆人,硕士,主要从事仪器仪表与测控技术方向的研究。

1671-4598(2016)07-0021-03

10.16526/j.cnki.11-4762/tp.2016.07.006

TP3 文献标识码:A