基于UVM和Matlab搭建的DVB-S编码调制系统验证平台

李 皓,苏秀红

(中国工程物理研究院 总体工程研究所,四川 绵阳 621900)

基于UVM和Matlab搭建的DVB-S编码调制系统验证平台

李皓,苏秀红

(中国工程物理研究院 总体工程研究所,四川 绵阳 621900)

提出了一种用于测试一个 DVB-S编码调制系统的功能验证平台。该平台使用高级验证方法学(Universal Verification Methodology,UVM)搭建了验证平台的主要结构,并在验证平台中使用外接Matlab作为复杂数字信号处理的参考模型。介绍了功能验证平台的主要结构和组件的设计,详细介绍了 UVM通过直接编程接口(Direct Programming Interface,DPI)以C++为桥梁与 Matlab连接的设计方法。通过实际仿真验证比较,使用这种方法搭建的联合平台比纯硬件语言Verilog语言搭建的仿真验证平台在验证时间上缩短了近50%,避免了对复杂信号处理验证模型的硬件语言设计,提高了针对复杂信号处理系统验证平台的搭建效率。

UVM;Matlab;C++;DVB-S;功能验证;联合仿真

0 引言

随着信号处理系统日益复杂,数字芯片的功能验证已经成为了影响芯片上市时间和成本的关键。然而信号处理芯片的系统级验证仍面临着诸多挑战。尽管在测试验证领域已经发展出了很多自动验证方法,但是目前在验证复杂信号处理算法时,多数仍需要使用人工添加测试用例的方法进行验证,耗费了大量人力物力。

验证信号处理算法的难点主要集中在如何使用合适的方法搭建高效的参考模型。

信号处理系统中一般包含大量复杂的数学算法,使用硬件语言实现这些算法的验证工作往往需要丰富的经验与技巧。如果使用硬件语言SystemVerilog来对这些算法进行验证,即便不考虑对验证工程师经验与技巧的要求,也应注意到使用硬件语言SystemVerilog来实现这些复杂算法很可能会使用与被测件相近的设计思路,产生类似的错误,从而遗漏一些致命错误。正是考虑到这一点,本文提出了一种使用 Matlab软件与高级验证方法学(Universal Verification Methodology,UVM)联合搭建的功能验证平台。利用UVM提供的直接编程接口(Direct Programming Interface,DPI)在验证平台中通过C++连接Matlab,实现信号处理系统中复杂的算法部分的验证,从而大幅提高了验证平台开发效率以及平台的复用性,加快了仿真验证时间。

1 DVB-S编码调制系统

数字视频广播(Digital Video Broacasting)是欧洲电信标准协会(European Telecommunications Standards Institute,ETIS)制订的关于数字电视卫星业务中帧结构、信道编码和调制的标准[1],被包括我国在内的绝大多数国家和地区所采用。该标准针对卫星数字多节目电视以及高清电视节目在固定卫星业务和广播卫星业务的一次发送和二次转发作出的规定,其调制方式采用四位移相键控(Quaternary Phase Shift Keying,QPSK),并采用基于卷积码和 RS(Reed-Solomon)码的级联纠错编码。根据 ETSI的ETS 300 421的规定,DVB-S的编码调制原理框图如图1所示。

图1 DVB-S的编码调制原理框图

根据DVB-S标准规定并结合实际使用时对参数的配置以及数据实时监测的需求,DVB-S的编码调制系统结构框图如图2所示。

图2 DVB-S的编码调制系统结构框图

2 UVM验证平台

2.1验证平台概述

本平台的验证是系统级的功能验证,主要目的是确保DVB-S编码调制系统电路设计与功能规范定义功能吻合。在DVB-S编码调制系统电路外围搭建UVM验证平台,采用受约束的随机测试方法将激励施加到被测件的输入,最后通过输出进行自动比较,检查是否正确,同时也要查看覆盖率是否达到了目标要求,如果没有达到,应该开发新的有效验证场景,通过迭代完成验证收敛[2]。其代码覆盖率和功能点覆盖率要求均为100%。平台使用的UVM库版本为1.1c,Matlab版本为2008b。

2.2基于UVM的验证平台设计与实现

2.2.1验证平台结构

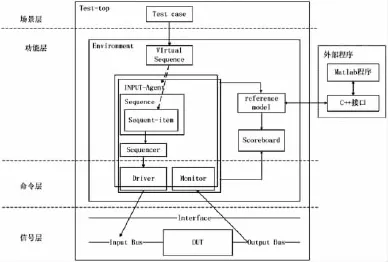

通用验证方法学 UVM是基于 SystemVerilog开发的一套开源类库,起源于OVM验证方法学[3]。UVM类库中定义了一系列的标准类,并结合标准接口、Factory机制、Phase机制、分层结构以及面向对象的设计思想使整个平台具有灵活配置、可重用、可扩展升级等优点[4]。本文提出的验证平台成功地应用于DVB-S编码调制系统的仿真验证,其最主要的特点就是将Matlab与UVM相融合,从而解决了仅用硬件语言难以验证的复杂数字处理算法。该验证平台的结构如图3所示。

图3 UVM验证平台结构

除了在典型UVM验证平台结构之外,本验证平台在参考模型(Reference model)中增加了外部接口连接到Matlab程序,对相应数据进行处理。

2.2.2验证平台顶层组件设计

本验证平台中的顶层主要是连接顶层 Test_top和环境类Environment。在Test_top中主要完成6个主要功能:被测件的例化,测试环境(主要指环境类)的例化,接口的例化,被测件、测试环境和接口之间的相互连接,整个测试环境时钟和复位的产生,验证平台的启动。

在环境类(Environment)中,主要完成 5项工作:例化代理类,例化参考模型,例化记分板,连接以上三个部分,完成验证平台的通用设置。在验证平台中,组件在环境类中的相互链接通过UVM中的fifo链接,这样可以方便地实现各组件间的异步接收。环境类处于验证平台的顶层,因此在环境类中同时也完成了一些与整个验证平台相关的设置工作,如设置平台可接受的最大错误数量,信息输出等级等。

2.2.3测试组件的设计

测试组件是验证平台的最重要也是核心设计,完成了验证平台的主要功能。其主要设计思想是尽可能地将对被测件单一功能项测试的组件进行封装,使组件能够尽可能少地依赖外部控制。主要包括7类关键组件:

(1)代理(agent):测试组件的顶层。由于DVB-S编码调制系统的输入输出关系相对简单,因此在本验证平台中只使用了一个agent对测试组件进行封装。agent主要完成sequencer、驱动器(driver)、监视器(monitor)的例化和连接。

(2)驱动器(driver):主要实现验证平台向被测件间输出的接口协议。在这里事物级的数据流将被转换为比特流,还有一个重要功能是将正在发送数据放到 uvm_analysis_port端口上,供验证平台使用。在本验证平台中主要有两个 driver,分别是向参数寄存器组发送参数的driver_parameter以及发送串行数据的driver_data。

(3)监视器(monitor):主要实现验证平台接收被测件输出的接口协议。这里将输出总线上的比特流转换为数据帧放到uvm_analysis_port,供验证平台使用。在本验证平台中也设置了两个监 视器 monitor_data和 monitor_source,用来分别监视输出的数据流以及对监测数据进行读取。

(4)transaction类:是传入数据的主要载体。在验证平台中,共设置了3个不同的transaction类,用于发送参数和原始数据的transaction_source,用于接收结果的transaction_data以及后面将提到的transaction_case。

(5)sequence类:主要功能是将测试用例传来的测试场景转换为transaction中数据。在本验证平台中sequence类主要将测试用例传来的参数传入 Matlab程序,并由Matlab产生真正的原始数据写入到transaction_source中。

(6)参考模型(reference model):主要是模拟被测件的行为,通过 uvm_blocking_get_port接收驱动器 driver_parameter和 driver_data传来的数据,并将这些数据传入Matlab进行处理,然后将处理结果通过 uvm_analysis_port传给记分板。

(7)记分板(scoreboard):主要功能是比对参考模型和被测件产生的数据,以确定是否存在问题。记分板(scoreboard)通过 uvm_blocking_get_port接收来自监视器monitor_data、monitor_source以及参考模型的数据。

2.3C++、Matlab接口的设计

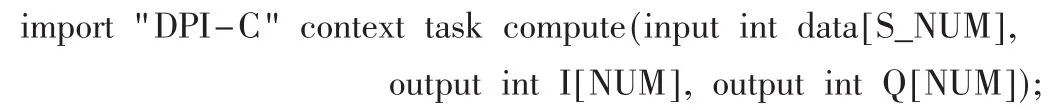

2.3.1UVM验证平台与C++的接口

SystemVerilog提供了方便的 DPI接口来连接 C++代码,只需SV文件中进行简单的声明并在脚本中进行相应的编译链接即可以使用[5]。在本验证平台中首先在参数文件中加入了对计算函数compute的声明如下:

然后在model_data中直接调用函数compute。在验证平台中C++与验证平台的接口主要是用于将验证平台与 Matlab程序相连接,因此没有用到复杂的功能,仅仅是将数据以合适的类型传入。这样设计的目的是有效利用用于原理验证的Matlab仿真程序。尽管Matlab仿真程序的运行效率远低于C++程序,但相对于HDL的仿真来说,这个效率问题往往可以忽略,而且 Matlab仿真程序拥有的多种算法资源加快了验证平台的搭建。

2.3.2C++与Matlab的接口

下面以compute函数为例说明在 C++中调用 Matlab函数的过程。其中函数声明如下。

在函数中,首先使用以下代码启动Matlab,其中头文件engine.h可在Matlab的安装目录下找到。

使用自建函数 input_arry将 UVM传入 C++的数据data进一步变换格式传入Matlab中成为数据x代码如下:input_arry(ep,x,S_NUM,data);

其中自建函数input_arry如下:

从Matlab到C++的转换程序与此过程类似,仅作反向处理即可,这里就不再讨论。最后将C++代码编译为动态链接库(dll)文件 compute.dll,然后在脚本文件加入vsim-sv_lib./TestBench/c/compute即可完成整个连接过程。

3 测试结果与分析

仿真验证用例运行完成后,对代码进行了回归测试并对覆盖率进行统计。回归测试后代码覆盖率的统计结果为,DUT的代码覆盖率为 99.72%,分支覆盖率为98.63%。剩余未覆盖到的情况如 default语句很难覆盖到,并对这种情况进行了人工代码走查。因此达到上述代码覆盖率百分比的情况可以认为满足了目标覆盖率要求。

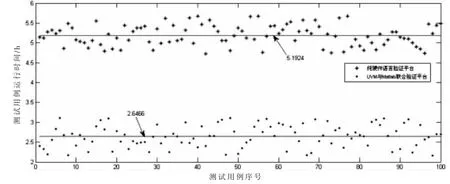

UVM与 Matlab联合仿真验证平台和完全使用硬件语言编写的仿真验证平台的仿真验证时间对比如图4。从图中可以看出使用纯硬件语言验证平台的测试用例平均运行时间为5.192 4小时,而使用UVM与Matlab联合仿真验证平台测试用例平均运行时间为 2.646 6小时,平均节约了近50%的时间。

图4 仿真时间对比

4 总结

本文采用基于UVM和Matlab联合搭建的仿真验证平台对DVB-S编码调制系统进行了功能验证,高效快速地达到了覆盖率要求。该平台与纯硬件语言仿真验证平台相比节约了近50%仿真验证时间,而且可以使用Matlab中成熟的工具箱对各种数字处理算法进行编程,极大地降低了验证平台开发难度,节约了开发时间并且提高了平台的复用性。

文中构建的平台结构移植性强,对其他类似的信号处理系统验证开发具有非常大的借鉴意义。通过对UVM与Matlab联合仿真环境的运用,显著提高了仿真验证效率,为复杂数字处理SoC验证提供了一条有意义的途径。

[1]ETSI.EN 300 421.Digital Video Broacasting(DVB).Framing structure,channel coding and modulation for 11/12GHz satellite services[S].1997.

[2]钟文枫.SystemVerilog与功能验证[M].北京:机械工业出版社,2010:5-7.

[3]Accdlera.Universal verification methodology 1.1 user′s guide[M].Cadence Design Systems Inc.,Mentor Graphics Corp.,Synopsys Inc.,2011,5:2

[4]田劲,王小力.基于 UVM验证方法学的 AES模块级验证[J].微电子学与计算机,2012(8).

[5]Chris Spear.System verilog for verification[M].Synopsys Inc.,2008:329.

A DVB-S coding and modulation systems functional verification platform based on UVM and Matlab

Li Hao,Su Xiuhong

(Institute of Systems Engineering,China Academy of Engineering Physics,Mianyang 621900,China)

In this contribution,we present a function verification platform for DVB-S coding and modulation system.The main structure of the platform is based on the Universal Verification Methodology(UVM),and the Matlab code is used in the complex signal processing reference model.Along with the structure and modules,we describe the method for connecting the UVM platform and the Matlab via Direct Programming Interface(DPI)particularly.The simulation proves that our approach save near 50%simulation time comparing with the pure Verilog platform.In addition,this approach avoids designing complex signal processing reference model with Verilog and improves the designing efficiency for complex signal processing verification platform.

UVM;Matlab;C++;DVB-S;functional verification;co-simulation

TN4

A

10.16157/j.issn.0258-7998.2016.01.002

2015-05-16)

李皓(1987-),男,硕士研究生,助理研究员,主要研究方向:电子信息系统设计与测试。

苏秀红(1988-),女,硕士研究生,工程师,主要研究方向:动态测试技术及信号处理。

中文引用格式:李皓,苏秀红.基于UVM和Matlab搭建的DVB-S编码调制系统验证平台 [J].电子技术应用,2016,42(1):15-18.

英文引用格式:Li Hao,Su Xiuhong.A DVB-S coding and modulation systems functional verification platform based on UVM and Matlab[J].Application of Electronic Technique,2016,42(1):15-18.