基于Altium Designer的信号完整性分析

崔玉美

(上海城市管理学院,上海 200438)

基于Altium Designer的信号完整性分析

崔玉美

(上海城市管理学院,上海 200438)

在当今的电子设计过程中,信号完整性问题的研究和处理已经成为不容忽视的重要环节。在电路的设计初期要利用电路设计软件仿真,充分考虑可能出现的问题,及时发现及时解决,节约成本,缩短产品开发周期。文中给出了在AltiumDesigner中的仿真波形,从仿真结果可以清楚地看到采取不同的解决办法,信号完整性问题改善的效果不同,因此要根据电路设计的实际需求采用合适的最佳解决方案。

AltiumDesigner;反射;串扰;信号完整性

1 引言

随着新工艺、新技术的快速发展,高速器件在电路设计中应用越来越广泛。在这种高速电路系统中,数据的传输速率、时钟的工作频率都越来越高,电路功能越来越复杂,电路板密度也相当大。这时,电路的设计重点就不仅仅是元器件的合理放置和导线的正确连接,更重要的是要对电路中的信号做完整性分析,否则,即使电路工作原理正确,系统也不一定能可靠正常地工作。因此电路设计中能否处正确处理好系统的信号互连,妥善解决好信号完整性问题,成为了一个设计能否成功的关键因素[1]。

2 信号完整性问题

信号完整性(SI,Signal Integrity)就是指信号通过信号线传输后仍能保持完整,保持其正确的功能而未受到损伤的一种特性[2]。主要研究的是信号传输后的质量和时序问题,当电路中的信号能以符合要求的时序和大小进行传送,并能按要求顺利的到达输出端,就说明电路具有较好的信号完整性,否则就出现了信号完整性问题。

信号完整性问题主要包括反射、振荡、地弹、串扰、电源噪声、EMI等等。

2.1 反射现象

反射是信号在传输线上的回波[2],信号功率的一部分经过传输线送达负载,另一部分则向信号源端反射回来。当反射信号到达信号源端时,若信号源端阻抗与传输线阻抗不匹配就将会产生第二次反射。若传输线的源端和负载端都存在阻抗不连续,那么信号将会在驱动线和接收线之间来回进行反射。实际上传输线任意一点上的信号都是由入射信号和反射信号多次叠加而成的。

当信号在传输过程中遇到比当前阻抗值高的时候,发生正方向反射,使信号边沿的幅度递增,出现过冲;当信号在传输过程中遇到比当前阻抗值低的时候,发生负方向反射,使信号边沿的幅度衰减,出现欠冲。这些波动的假时钟信号过大,超过一定的范围时,就可能会导致系统的误操作,产生故障,甚至造成事故。

如果信号在一个时钟周期中,反复地出现过冲和欠冲,称之为振荡或振铃。这就是电路中因为反射而产生的多余能量无法被及时吸收的结果。如果没有采取合适的抑制措施,就会引发传输信号波形的失真,如图1。

图1 反射失真波形

2.2 串扰

在高速数字电路设计中,串扰现象及其常见。信号串扰是在电气上没有连接的信号线之间,因电磁耦合对相邻的传输线产生不期望的电压干扰噪声[4]。由于信号线本身逻辑电

平发生变化,对其他信号产生影响的信号线称为“攻击线”。受到影响而导致自身逻辑电平发生不正常的信号连线称为“牺牲线”。串扰噪声从攻击对象上以耦合电压或耦合电流的形式,交叉耦合到牺牲对象上,表现为在其中一根信号线上有信号通过时,在PCB板上与之相邻的信号线上就会感应出相关的耦合电压或电流信号。

串扰一般可以分为前向串扰和后向串扰。前向串扰是指攻击源对牺牲对象的接收端产生的第一次干扰,也称远端干扰,同样是由于电容和电感的耦合形成的,但是这两个耦合形成的干扰信号是反相的,是可以相互抵消的,因此前向串扰几乎可以忽略。而后向串扰指攻击源对牺牲对象的发送端产生的第一次干扰,也称为近端干扰,两个分量是同相的,不容忽视,因此一般研究都是后向串扰。

设定网络A12为攻击对象,A13为牺牲对象,在没有采取任何抑制措施时的干扰线与被干扰线上的信号波形如图2。可以看出在牺牲信号线A13上存在着很大串扰噪声,最大串扰噪声幅度可达30mv左右。

图2 信号间的干扰噪声

2.3 电源、地弹噪声

电路中各种芯片和电源平面之间存在着一定大小的寄生参数,每当电路中有较大的电流涌动时,如芯片多个输出级同时动作,就将会有较大的瞬态电流在芯片引脚与PCB板的电源平面中流过,从而导致电源线上和地线上的电压波动,这个不期望的波动噪声可能会造成其他元器件的不正常动作。

地平面的分割,也可能引起数字信号传到模拟接地区域时,产生接地平面信号回流反弹。同样,电源平面的分割也可能有类似情况的危害产生。负载容性的增大、阻性的减小、寄生参数的增大、切换速度的加快,以及同步切换数目的增加,都有可能导致接地反弹噪声的增加。

3 改善信号完整性问题的方法

由于上述这些信号完整性问题的存在,就可能会导致本来原理正确的电路,出现了不正常的信号,从而使得高速数字电路中的器件不能正常工作。因此为了保证信号在传输后仍能保持其应有的可靠的功能和稳定的性能,必须在电路设计初期就处理好这些问题。

3.1 抑制反射的方法

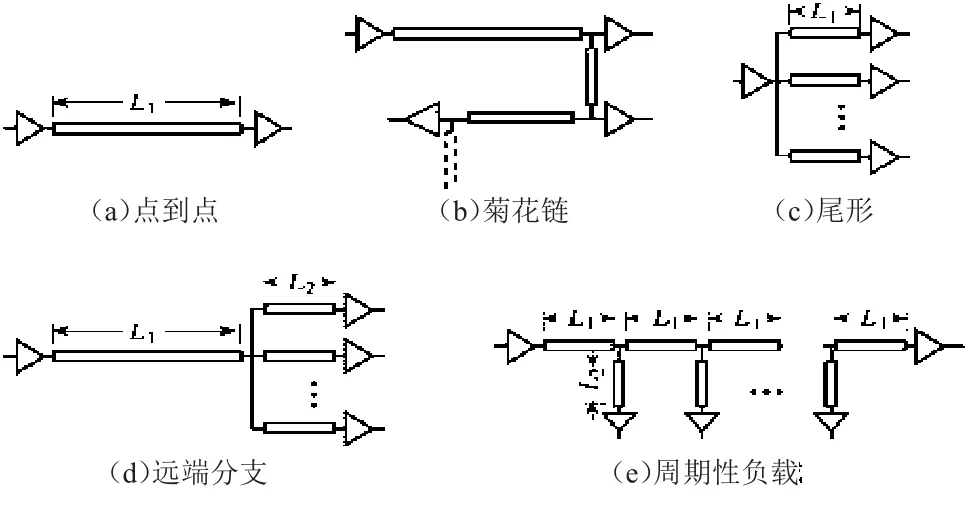

改善反射噪声的一般做法是布线拓扑法,尽量缩短高速传输线的长度,以减小信号线的传输线效应。常用布线时的拓扑结构有:点到点、菊花链、星形、分支和周期性负载等结构,如图3所示。

图3 布线拓扑结构

端接技术是高速数字电路处理信号完整性问题最常用的办法,在信号输入、输出端端接电阻来达到阻抗匹配的目的。端接技术一般分为串联端接技术和并联端接技术。

串联端接是利用使信号源端反射系数为零,来抑制从负载端反射回来的信号再从信号源端反射回负载端。在尽量靠近驱动信号源端的位置串联一个电阻到传输线中来实现,所串联电阻阻值加上驱动源的输出阻抗应大于等于传输线的阻抗,用以匹配信号源的阻抗,如图4。

图4 串联端接

并联端接一般是在尽量靠近负载端的位置接上拉或下拉电阻,以实现电路终端的阻抗匹配问题。并联端接有如图5几种方式,可用于分布负载,并能够全部吸收传输波以消除反射,表1给出了各种端接技术的优缺点。

图5 并联端接

表1 各种端接技术比较

3.2 串扰和噪声的抑制方法

串扰是由于信号线间的电磁耦合引起的,减小串扰最行之有效的方法就是增加信号线间的距离,减小耦合长度。但高速系统设计中,PCB板的密度已经越来越大,靠增加信号线间的距离改善串扰已不可能了。因此可以通过改变PCB板的绝缘介质参数和绝缘介质的厚度来减小电磁耦合,从而来达到减小信号线间的串扰的目的[3]。

目前多层PCB板都包括若干个信号层和电源层,两信号层和电源层的叠放顺序没有特殊规定,通常是通过叠放顺序来构成标准的微带传输线和带状传输线,与之相邻的都有一个电源平面,相应信号层与电源层之间是需要用电介质填充的。电介质层的厚度是影响传输线特性阻抗的重要因素,电介质层变厚时,传输线特性阻抗变大,变薄时,传输线特性阻抗变小。对于同样电介质层厚度,带状传输线的串扰要小于微带传输线的串扰。因此在高速电路布线时,如带状传输线的阻抗控制能够满足要求,那么使用带状传输线可以比使用微带传输线获得更好的串扰抑制效果。

抑制电源和地弹噪声的方法也很多,可以通过降低封装回路电感,在封装内部使用旁路电容,让电源和地共同分担回路电流,从而减小电压波动等等,来降低和改善电源和地弹的噪声。

4 基于Atium Designer的信号完整性分析

Altium Designer是Altium公司的一款最新的EDA设计软件,提供了完整的集成信号完整性分析工具,对电路潜在的信号完整性问题,可以在原理图环境中对选择的节点进行分析,可以找出初步的阻抗、反射等问题;更全面的分析是在PCB环境下完成的,不仅能以清晰的波形形式给出各种分析结果,而且还能为设计者提供一些有效的终端措施,来帮助选择合适的解决方案。

4.1 信号完整性分析前的准备工作

为了在做信号完整性分析时,能不出现一些不必要的麻烦,能够顺利准确地得到分析结果,必须要事先做好以下几项准备:

(1)PCB设计中每个组件的SI模型类型都必须是正确的,如果没有SI模型的器件要自己进行添加设置,对于IC组件来说,一般要从芯片厂商提供的IBIS文件导入模型I/O管脚特性。

(2)软件是以集成项目为核心的,在做SI分析之前,都要确认所有的文件,包括原理图文件和PCB文件,都包含在工程项目文件(*.PRJPCB)下,不能是自由文档,否则软件是不能给出准确的仿真结果的。

(3)要想成功分析电路的所有特性,在对网络进行仿真的时候,必须要有集成电路的输出引脚作为激励源连接到网络上,否则电容、电阻和电感这些被动器件是无法给出正确的仿真结果的。

(4)PCB的层堆栈要必须准确无误,要根据电路板的实际设计情况来设置所有信号层和电源层的厚度,包括绝缘介质层的材质和厚度等相关参数,因为这个是对串扰分析会有很大的影响的[7]。

4.2 信号完整性分析

一切准备工作就绪后,最好先对工程项目进行编译,确认没有任何错误了,就可以在PCB编辑器中执行【tools】/【signal integrity】分析命令,在弹出的分析窗口中,左侧部分可以看到网络是否通过相应的规则,选择网络“A12”,点击右键,在下拉菜单中选择“Details”命令,可以看到针对此网络分析的详细信息。

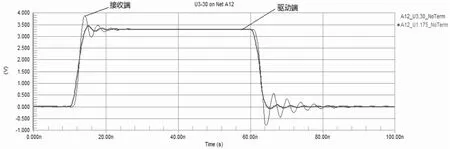

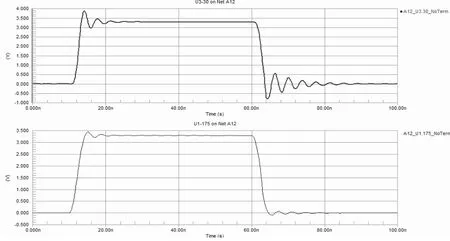

对电路中的关键网络进行信号分析,选中想要重点分析的网络标签,如“A12”,双击导入到窗口右侧待分析列表中,单击窗口右下角的Reflection Waveforms命令,进行反射情况分析。下图6是对网络“A12”进行反射分析波形。

图6 反射分析结果

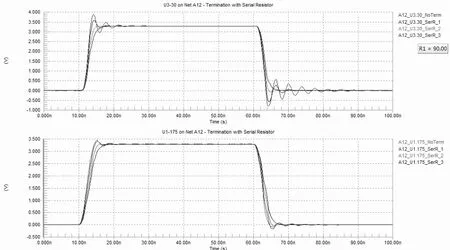

在图6的分析波形中可以看到在信号线上存在着很大的反射噪声,也可以根据需要进行确切的参数测量。在图6信号完整性分析窗口右侧可以选择各种端接策略,如戴维南端接、下拉电阻端接、二极管端接等,每种端接方式可以设置不同的端接阻抗,来减小反射所带来的影响,图7选择的是串联端接方式,电阻值分别为20Ω,55Ω,90Ω,设计者可以根据波形分析结果,根据实际噪声容限的要求[5],选择合适的阻抗值和合理的端接方式。用同样的方式可以对电路中的关键网络进行串扰分析。

图7 反射分析结果

5 结语

高速PCB设计在数字系统设计中占有越来越重要的地位。一个系统是否能具有高性能,能否长期稳定的工作,在很大程度上取决于PCB设计的合理性。要使PCB产品缩短上市时间,降低产品成本,就要在PCB设计的整个过程中,充分考虑高速信号的完整性问题,要综合考虑各方面因素,合理布局布线,设计初期都必须经过仿真验证,在第一时间发现潜在的问题并找到合适的解决方案。

[1]王渊峰,戴旭辉.Altium Designer10电路设计标准教程[M].科学出版社,2013.

[2]Eric Bogatin.信号完整性分析[M].李玉山,李丽平,等译.北京:电子工业出版社,2008.

[3]陈伟,黄秋元.高速电路信号完整性分析与设计[M].北京:电子工业出版社,2009.

[4]高海宾,辛文,胡仁喜,等.Altium Designer10从入门到精通[M].北京:机械工业出版社,2014.

[5]崔玉美.基于Protel2004的信号完整性分析与研究[J].实验室研究与探索,2010,(11):38-40.

Signal IntegrityAnalysis Based onAltium Designer

Cui Yumei

(Shanghai Technical College of Urban Management,Shanghai 200438)

tract】 In today's electronic design process,the research on signal integrity has become an important part that should not be ignored.At the early of the circuit design process,the circuit design simulation software should be used,considering the problems and resolving them to shorten the product development cycle.This paper presents the simulation waveforms in Altium Designer.Results show that different solutions lead to different signal performance.So we should adopt the best solution according to the actual conditions of the circuit design program.

words】 Altium Designer;reflection;crosstalk;signal integrity

TP391

A

1008-6609(2016)09-0092-04

崔玉美,女,黑龙江人,硕士研究生,副教授,研究方向:电子技术的教学与科研。