DDS工业数字移相信号发生器应用设计*

潘泽锴,兰国莉

(广西职业技术学院 计算机与电子信息工程系,广西 南宁 530226)

DDS工业数字移相信号发生器应用设计*

潘泽锴,兰国莉

(广西职业技术学院 计算机与电子信息工程系,广西 南宁 530226)

采用DDS技术设计工业控制现场测试信号源,基于VHDL语言进行系统建模,对DDS进行重新参数设计,实现IP核重构,能够根据需要修改参数以实现器件的通用性;利用QuartusⅡ平台完成具体DDS芯片设计,阐述了基于VHDL编程的DDS设计的方法步骤。经测试,该设计各项设计指标符合要求,具有很好的实用价值。

现场可编程门阵列;信号发生器;DDS;VHDL

0 引言

直接数字频率合成信号发生器(Direct Digital Synthesize,DDS)具有易产生、分辨率高、绝对误差小等优点,在已有电子系统及设备的频率设计中,以及在工业控制现场信号测试中得到越来越广泛的应用[1]。在进行工业现场通信信号的传输测试实验中,在原有信号发生器携带不方便、输出不稳定的情况下,以DDS技术为基础设计新型信号发生器,利用VHD语言实现对DDS功能的重新设计,可以简单地完成在不同方式下的移植,输出参数可以根据现场环境进行适当的修改[2]。在实现过程中使用Alter公司开发的QuartusⅡ软件,该软件不仅提供了VHDL开发编译环境,还集成了DDS设计开发所需要的FPGA器件,这样就可以大大降低开发难度和缩短开发周期[3]。

1 DDS原理及系统分析

DDS是一种全数字、高分辨精度、反应速度在毫微秒量级的频率合成技术,属于开环无反馈环节的控制系统结构。根据它的相位特性可知其相位是连续变化的,而且相位误差极小,可以输出很好的频谱波形,一些在传统的频率合成困难的情况下使用DDS技术可以很好地完成[4]。

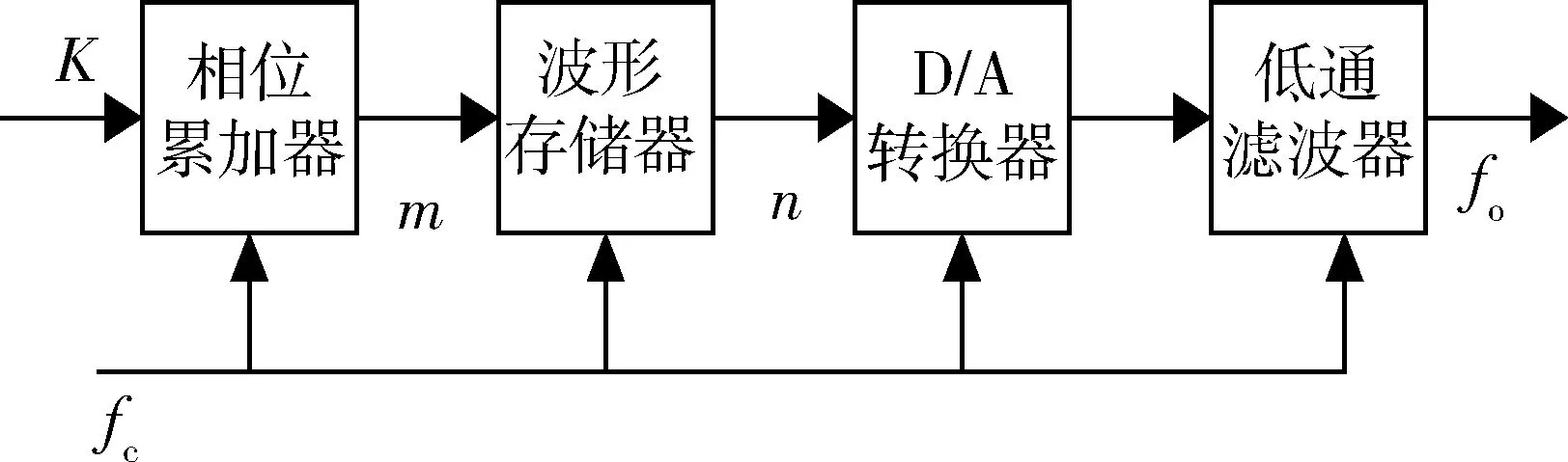

图1 DDS组成模块图

由图1的DDS组成模块图可知DDS信号发生器的工作原理:在每次接收到一个时钟脉冲fc时,频率控制字K和相位累加器两者之间相位数据相互累加,累加结果送累加寄存器保存,相位累加器由N位加法器与N位累加寄存器级联组成,将获得的累加器脉冲再反馈回去与原来累加的新接收到的下一个时钟脉冲相加,以使加法器在下一个时钟脉冲的作用下继续与频率控制字相加,不断对相位进行累加获得输出脉冲。这就相当于,相位累加器在每一个脉冲到来的时候都实现脉冲累加,最后的脉冲输出就是脉冲不断累加的结果。累加输出的频率就是合成以后DDS信号输出的频率,相位累加器输出的数据作为波形存储器ROM的相位取样地址,通过查表的方式可以获得波形信号取样,完成相位到幅值的转换[6]。

累加器通过相位累加的方式实现脉冲输出之后放于波形存储器,波形存储器的输出送到D/A转换器,D/A转换器的主要作用就是把输出波形的数字信号变成模拟信号,完成所需要的信号形式,但是输出的信号可能含有毛刺,可以通过低通滤波器的方式去除毛刺和其他谐波,最后输出一个合成频率为f0的信号波形[7]。输出频率f0与时钟频率fc之间的关系满足下式:

f0=(k×fc)/2N

(1)

由公式(1)可知,输出的频率f0是时钟脉冲fc与频率控制字K合成的结果,同时还与位数N有关,通过改变K值可以改变频率的输出。DDS信号发生器输出的最小频率可以由方程△f=f0/2N确定。频率分辨率在fc固定时,取决于相位累加器的位数N。只要N足够大,理论上就可以获得足够高的频率分辨精度。另外,由采样定理,合成信号的频率不能超过时钟频率的一半,即f0≤fc/2,因此频率控制字的最大值Kmax应满足Kmax≤2N-1。

在FPGA内部比较容易产生信号生成模块,而单纯的DDS芯片不但价格高,而且功耗大,在这方面使用FPGA技术就有很大的优势。鉴于此,本设计采用FPGA技术产生DDS信号发生器来实现任意波形发生器的设计。

2 DDS设计与实现

2.1 DDS波形发生器总体设计

根据DDS的基本原理及系统分析,可以比较具体地设计出整个波形发生器的总体方案,如图2所示。

五是缺乏对培训过程的有效评价。目前,对培训效果评价的基本形式是受训学员的无记名问卷调查,均是主观的终结性评价,以知识和能力掌握程度为主。培训没有有效的评价体系,实际也没有与绩效紧密相关的培训考核,不仅主体是局部的,缺乏真实性,而且过程是片面的,缺乏细节的,所以培训的实际评价和反馈是形同虚设的,更没有建立个体培训档案并进行深度分析和研究。在问卷调查中,79.9%的被试几乎没有培训反馈和评价。

图2 波形发生器总体框图

根据设计的波形发生器的原理图,在设计中需要对重现信号波形进行周期性取样作为参考波形,DDS控制器根据参考波形设定频率参数,和需要选择的输出波形参数存储在波形RAM单元中;根据待设波形进行幅度设定,把频率设定参数和经过幅度变换后的波形进行线性叠加后经D/A转换输出信号波形[4]。

本设计中调用LPM即参数可设置模块库来生成存储器模块。在设计波形信号发生器的过程中,如果要使用FPGA特定的器件,那么在设计VHDL程序中亦要使用与该期间配套的宏模块功能,而这些在软件使用中可以以图形或是硬件语言描述的形式来实现,可大大提高设计的效率和可靠性[5]。

2.2 系统FPGA设计实现

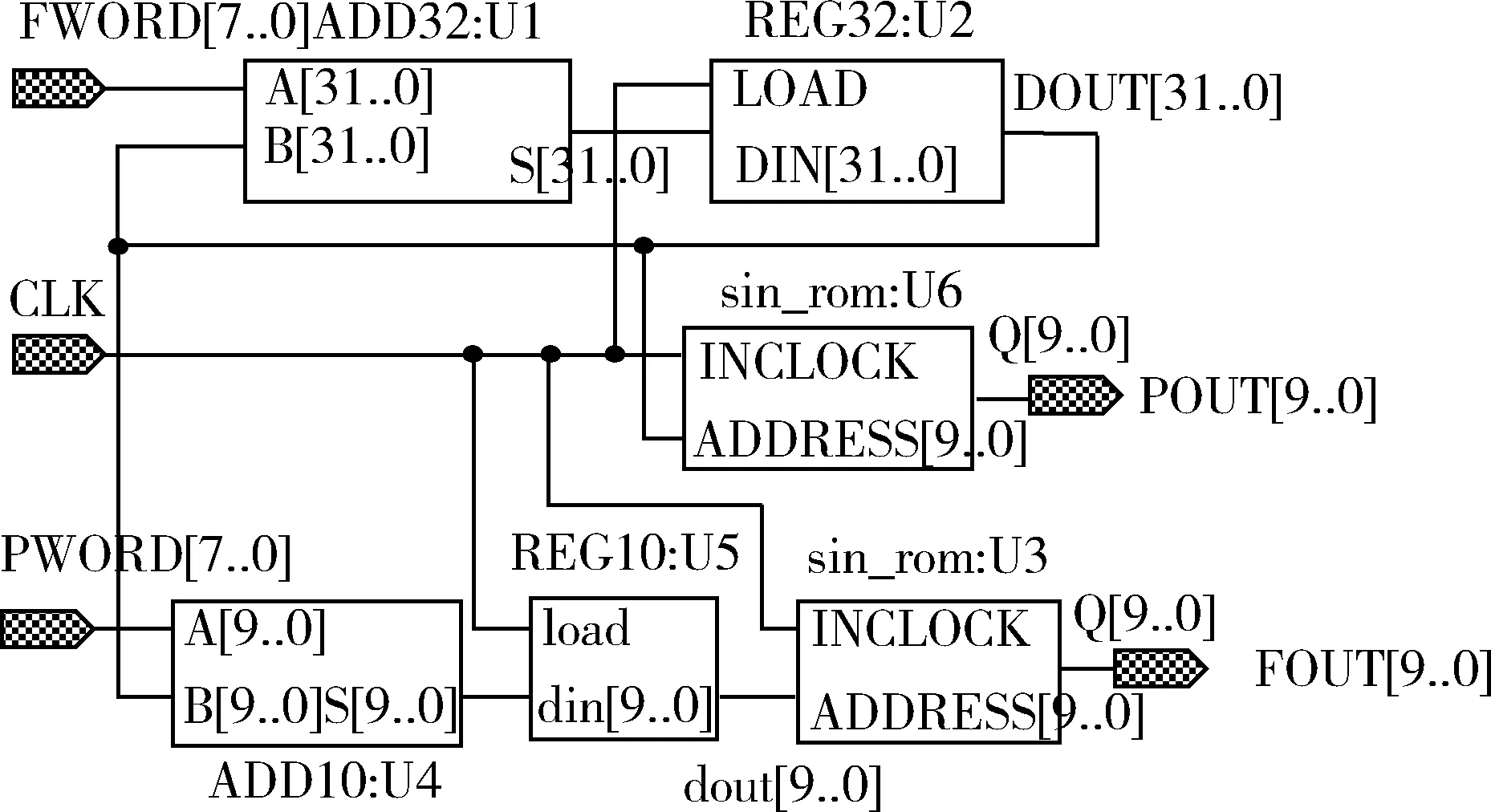

利用FPGA实现双DDS 的相位累加器,通过数字方法实现频率调制,通过查表的方式,DDS利用RAM操作总线与FPGA内部CPU通信,实现各种波形[6]。实现的基本原理如图3所示。

图3 DDS在FPGA内部实现原理图

在实际测试中以正弦波为例,系统采用QuartusII软件进行设计,使用GW48 EDA/SOPC实验开发平台进行调试,系统分为波形数据ROM模块、32位加法器模块、32位寄存器模块、10位加法器模块、10位寄存器模块等几部分[7]。

2.3 用户控制

系统使用实验开发平台的键盘和LED接口实现人机交互,通过键盘设定待输出的波形、波形的频率以及波形的幅度等参数。

待输出波形部分使用了3个按键,每个按键对应一种波形,对应的发光二极管显示有效状态,并且可以多个按键同时起作用,此时即波形的线形叠加,该功能的实现是通过使能对应的波形数据ROM的输出和幅值控制的输出实现的[8]。

频率调节使用了一个双向计数器给DDS控制器赋值来控制输出信号的频率(周期输出点数),其中双向计数器有一个输入端控制计数方向,即加还是减,另一个进行计数。该部分设计受实验台的限制(按减少)不能直接输入数字,因此设定比较慢,而频率设定的具体数值在实验台上可使用两位数码管来显示。

设计的相位累加器对于每来一个时钟脉冲加法器就会与累加寄存器的累加相位相加,在一个时钟作用之后,加法器的输入端又会加入新的相位数据,与上一个时钟周期的相位进行累加。当相位累加器加满之后会溢出,实验中以相邻两次累加器溢出时间间隔为一个周期合成DDS信号,而在每次信号合成的取数环节之前,会在累加器输出的信号加上相位移,以此来对相位进行调节[9]。

因为幅值分别对应3种不同类型的波形,因此需要对其分别设定,该部分共使用了3个按键,其中一个按键用来设定待调节幅值的波形,直接使用一加计数器,通过实验平台上的输出发光二极管来显示所选定的波形。幅值大小的调整同频率调整,使用了双向计数器,调整的输出由乘除器进行变换后输出[10]。设定波形幅度的数值显示在实验台的LED数码管上,每个波形幅值显示使用两位LED数码管,供使用6个。

3 功能测试与结果输出

使用QuartusII任意生成一个1 024单元10 bit宽的mif文件,将其中的信息拷入到sin_rom.mif中,最后将生成的sin_rom.mif加入到LPM_ROM中去[7]。QuartusII提供了强大、直观、便捷和操作灵活的原理图输出设计功能,本实验输出的原理图如图4。

图4 信号输出原理图

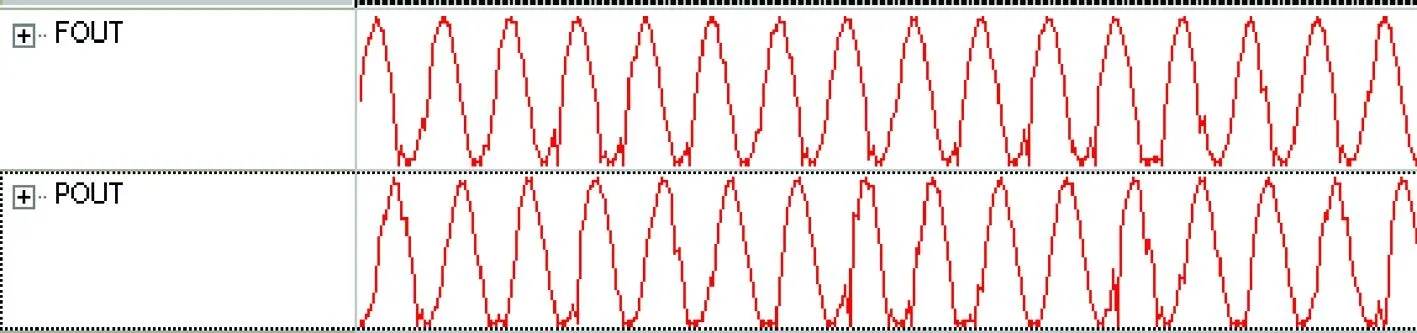

利用FPGA设计DDS信号发生器后使用QuartusII进行时序仿真,设置好相应的仿真参数,得出的仿真波形如图5所示。

图5 仿真波形输出

使用QuartusII自带的Signal tap逻辑分析仪进行硬仿真测试,为了能对此信号进行硬件测试,将芯片固定的端口与输入输出信号绑定,通过软件编译好之后下载到硬件进行测试。

在测试完成之后,重新对配置芯片进行编程,最终完成信号发生器信号的输出。图6、图7是在相同条件下不同频率的正弦波对应的逻辑分析仪采样结果。

图6 输出频率为5 kHz波形采样

通过测试表明,设计的DDS数字移相信号发生器具有连续输出正弦波波形的功能,使用键盘输入具有产生周期性先行组合波形的能力,输出波形的频率范围在100 Hz~200 kHz,且频率步进间隔≤100 Hz,具有显示输出波形的类型、重复频率(周期)和幅度的功能。

图7 输出频率为100 kHz波形采样

4 结论

采用FPGA器件,利用VHDL语言对DDS信号发生器进行重新设计与实现,可以在不同的方式下进行移植和参数修改,信号发生器输出信号稳定,便于携带。通过测试表明各项设计指标符合要求,具有很好的实用价值。

[1] 丁革媛, 李振江,宋扬,等. 工业控制系统中的安全隐患分析[J].微型机与应用,2015,34(1):7-9.

[2] 白丽娜,周渭,赵桀,等. 一种和DDS结合的高分辨率频率计设计[J].西安电子科技大学学报,2012,39(4):126-130.

[3] 邓耀华,吴黎明,张力锴,等.基于FPGA的双DDS任意波形发生器设计与杂散噪声抑制方法[J].仪器仪表学报,2009,30(11):2255-2261.

[4] 潘松,黄继业.EDA 技术与VHDL(第2版)[M].北京:清华大学出版社,2007.

[5] 张萍.基于DDS 的宽带信号发生器的设计[J].江南大学学报,2015,14(6):782-786.

[6] 阎石.数字电子技术基础(第四版)[M].北京:高等教育出版社,2003.

[7] 王丰华,李建清,吴剑锋.多源表面温度信号发生装置的硬件设计[J].仪表技术与传感器,2014(1):83-85.

[8] 李雪梅,张宏财,王学伟.基于DDS技术的信号源设计[J].电测与仪表,2010,47(1):55-57.

[9] 杨萍,兀旦晖,杨良煜.DDS技术在正弦信号发生器中的应用[J].计算机测量与控制,2008,16(11):1738-1740.

[10] 李敏,金励豪.矩形波信号发生电路的设计与分析[J].电子技术,2013(10):34-36.

Application and design of industrial DDS in digital phase shift signal generator

Pan Zekai,Lan Guoli

(Department of Computer and Electronic Information Engineering, Guangxi Vocational and Technical College, Nanning 530226,China)

The DDS technology is used to design industrial control field test signal source. The system is imitated based on VHDL language. Parameter is redesigned for the DDS and the kernel of IP is reconstructed. In the light of demand to revise the parameter, which is achieved the commonality of device. Using the platform of Quartus Ⅱ to complete the definite design of DDS chip. The methods and steps of DDS’s design based on VHDL program are expounded. The design specifications conformed to demand by test. It has a very good practical value.

Field Programmable Gate Arrays(FPGA); signal generator; DDS; VHDL

广西教育厅自然科学基金资助项目(YB2014487,KY2015YB384);广西职业技术学院自然科学基金资助项目(151206)

TN914

A

10.19358/j.issn.1674- 7720.2016.23.023

潘泽锴,兰国莉. DDS工业数字移相信号发生器应用设计[J].微型机与应用,2016,35(23):80-82.

2016-07-13)

潘泽锴(1984-),男,硕士研究生,讲师,主要研究方向:智能控制、工业自动化等。

兰国莉(1979-),女,本科,实验师,主要研究方向:智能实验室管理等。