CMOS电路中外部能耗控制模块的设计与实现

李瑞芳

摘 要: 传统的大规模集成电路的功耗控制方法存在运算量高、精确度有限的问题。因此,基于双阈值低功耗技术设计并实现CMOS电路中外部能耗控制模块,采用双阈值电压技术通过较低阈值的晶体管设计CMOS能耗控制模块。通过高阈值电压的NMOS管控制低阈值模块,降低电路的泄露电流,使用低阈值模块中的NMOS管对CMOS门单元电路进行管理,提高门单元电路的运行效率,降低总体CMOS电路的功耗。采用双阈值技术设计CMOS电路的单边沿脉冲触发器,对触发器的时钟响应电路进行优化,确保时钟翻转通过数字信号进行管理,极大降低时钟翻转频率,减小电路动态功耗。实验结果表明,所设计模块具有较高的控制效率,较低的延迟和功耗,其控制下的CMOS电路节能效果显著。

关键词: CMOS电路; 能耗控制; 双阈值; NMOS

中图分类号: TN108+.7?34; TN432 文献标识码: A 文章编号: 1004?373X(2016)22?0112?0

0 引 言

集成电路工业的发展增强了CMOS电路运行频率和集成度,也导致电路功率逐渐增加。大功耗导致系统稳定性和可靠性降低,提高了系统封装的难度[1?2]。CMOS电路中的大功耗,使得芯片运行情况减弱,大大降低了芯片价值。因此,功耗问题成为CMOS电路快速发展过程中急需解决的问题。而传统的大规模集成电路的功耗控制方法,存在运算量大、精确度有限的问题[3?5]。因此,采用合理的功耗控制方法,保证CMOS电路完成预期的功耗目标,成为相关任务研究的热点方向。

以往研究出的集成电路能耗控制方法都存在一定的问题,如文献[5]基于传统晶体管功耗模块,其依据电路完整的硬件描述实施功耗模拟,但是该模块要求CMOS电路中存在完整的寄存器传输设计,并且其运行时间和内存消耗较高。文献[6]通过PSPLCE模拟采集CMOS电路电源特征和数据,通过动态阈值功耗预测方法,实现CMOS电路功耗的有效控制,但其对电源稳定性要求较高,并且需要采用大量的数据进行模拟分析,运算效率低,存在一定的局限性。文献[7]通过降低CMOS电源电压,控制CMOS电路功耗,设计出电流型CMOS电路,实现CMOS电路能耗的合理控制,但是该方法存在控制精度的缺陷,并且容易产生过电量问题。文献[8]采用基于仿真的CMOS电路平均功耗估计方法,其通过全部可能的输入组合对电路进行仿真,依据仿真功耗运算平均功耗,但是该方法需要用户明确输入模式中的全部信息,局限性较高。文献[9]通过最小平方方法预测CMOS电路的平均能耗,其通过点预测方法,可在高精度下得到较高的收敛效率,但该方法的估计结果容易受到电路内部和外部环境的干扰,无法对电路能耗进行准确控制。

为了解决上述分析方法存在的问题,降低CMOS电路能耗,采用双阈值电压技术通过较低阈值的晶体管设计CMOS能耗控制模块,也就是低阈值模块。通过高阈值电压的NMOS管控制低阈值模块,降低电路的泄露电流;通过低阈值模块中的NMOS管对CMOS门单元电路进行管理,提高门单元电路的运行效率,降低总体CMOS电路的功耗。

1 CMOS电路中外部能耗控制模块设计

1.1 双阈值CMOS电路能耗控制过程

双阈值CMOS电路结构图如图1所示。为了提高CMOS电路逻辑单元的性能,通过较低阈值的晶体管设计CMOS能耗控制模块,也就是低阈值模块。在低阈值模块间设计了高阈值电压的NMOS管TN,如图1(a)所示。通过Sleep_bar管理信号调控低阈值模块,如果管理信号为1,则TN导通,低阈值电路模块可顺利运行,模块同地连接。TN管的漏极可看成虚地,形成微高于0的电压,该电压不会干扰总体电路的运行。受到漏极电压的干扰,低阈值模块的晶体管中的电压增加,使得泄露电流减少;如果管理信号设置为0,则TN管不导通,低阈值模块停止运行,同地断开,虚地点悬空。TN管较高的阈值电压导致自身泄露电流降低,有效控制了低阈值模块电流,大大降低了总体CMOS电路功耗。

图1(b)描述的是采用高阈值电压PMOS管器件管理低阈值模块的结构,该结构的原理与高阈值NMOS管管理相似,通过sleep信号的置复位管理情况,管理低阈值模块电路的运行,实现降低功耗的目标。高阈值NMOS管管理低阈值模块,具有较低的导通电阻,能够更加节省CMOS电路硅片的面积。

双阈值CMOS电路结构能够完成切断电路以及电源回路的设计,过滤额外功耗。通过对CMOS电路结构中NMOS管以及PMOS管的逻辑互补特性,确保总体电路系统的上拉和下拉形成不同通路轮流互相导通,完成CMOS电路外部能耗的合理控制。

双阈值CMOS电路的抑制结构如图2所示。

分析图2能够看出,当双阈值CMOS电路采用图2(a)描述的结构时,其输出端在高阈值NMOS管子停止后会形成悬空问题,会产生负面干扰。而使用图2(b)结构情况下,额外产生的高阈值PMOS管,将在NMOS管终止运行情况下保存输出端的稳定,限制输出节点悬空问题的发生。

实际控制CMOS电路外部能耗过程中,通过冗余检测信号r替代管理信号Sleep调控高阈值NMOS管的通断,主要是因为信号r能够分析CMOS电路的冗余状况,并且其具有同管理信号Sleep的相同作用。如果信号r检测到低阈值模块为冗余状态,则终止NMOS管的运行,确保逻辑块停止运行,避免其泄露电流,降低电路能耗。该结构设计能够避免低阈值模块出现泄露电流现象,并且合理控制CMOS电路的冗余问题,避免出现冗余情况下的电平翻转波动的传递,最大程度降低电路动态功耗。

1.2 双阈值CMOS电路门单元运行控制

通过上述分析的双阈值CMOS电路能耗控制过程可得,采用高阈值NMOS管可设置该低功耗控制装置。因此,在各CMOS门单元电路中融入Sleep管理信号,通过低阈值模块中的NMOS管对不同CMOS门单元电路的运行情况进行有效管理,提高门单元电路的运行效率,降低总体CMOS电路的功耗。通过门单元能够设计出双阈值的反相器、与非门以及或非门等,如图3所示。

采用关联信号Sleep_bar调控高阈值NMOS管的通断,若Sleep为0,Sleep_bar为1,则门单元正常工作;否则,若Sleep为1,终止高阈值管的运行,电路休眠,门单元终止工作,最大程度降低电路能耗。

1.3 双阈值CMOS电路中单边沿脉冲触发器设计

触发器是CMOS电路中的关键电路单元,对其功耗进行优化控制,可降低CMOS电路的功耗。将CMOS电路的总平均功耗当成触发器的功耗参数,主要包括触发器内在功耗、数据驱动功耗以及时钟驱动功耗。触发器中的缓冲反相器驱动数据输入以及时钟信号的过程中,将形成数据驱动功耗和时钟驱动功耗。触发器内部功耗是其内部消耗的功耗。因此,对触发器进行优化设计,降低其功耗,可确保总体CMOS电路能耗的最低化。触发器的时序参数是其塑造时间以及单元本征延时。触发器的塑造时间是数据在时钟信号沿到来前的持续时间,如图4所示。其中,[TD-C]是数据Data到时钟C延时,[TD-Q]是数据D到输出Q的传播时间,其是单元的传播延时,[TC-Q]是时钟到输出的延时,同持续时间具有一定的关联性,其通过式(1)获取。

图5为设计的双阈值CMOS电路中的单边沿脉冲触发器,该触发器能够对CMOS电路能耗进行优化处理。图5中设计的单边沿脉冲触发器包括时钟响应电路和数据响应电路。通过高阈值电压和低阈值电压分别设计数据响应电路和时钟响应电路。该触发器中时钟脉冲时序产生过程为CLK信号通过反相器链,获取一个延时反向信号CLKBD,计算该信号和CLK信号,能够获取高窄脉冲CLKP信号。但是时钟脉冲跳变时,容易形成电平的翻转,导致CMOS电路形成较高的动态功耗。因此,为了降低电路功耗,采用双阈值技术设计单边沿脉冲发生电路,对时钟信号进行调控,降低翻转率,减少时钟电路动态功耗。该触发器采用时钟信号CK在D和Q间的延时差间产生脉冲,并且采用异或电路进行优化设计,得到如图6所示的单边沿脉冲发生电路。

该单边沿脉冲发生电路的脉冲信号波形示意图如图7所示。

传统CMOS电路触发器中的电路,存在时钟通过反相器翻转的跳变,导致动态功能增加。因此,将单边沿触发器电路数据端D信号和Q信号当成时钟响应电路的使能信号,确保时钟翻转出现D信号处于高电平的区间。

该设计能够确保当D信号处于低电平区间时,时钟信号不会出现翻转,降低反相链电路以及数据采样电路中的电平翻转发生率,减少动态功耗,实现CMOS电路的低功耗设计。同时设计的双阈值单边沿脉冲触发器,能够降低时钟在电路中的跳变,降低时钟脉冲的数量以及晶体管跳变数量,最大程度上减少功耗。

2 实验分析

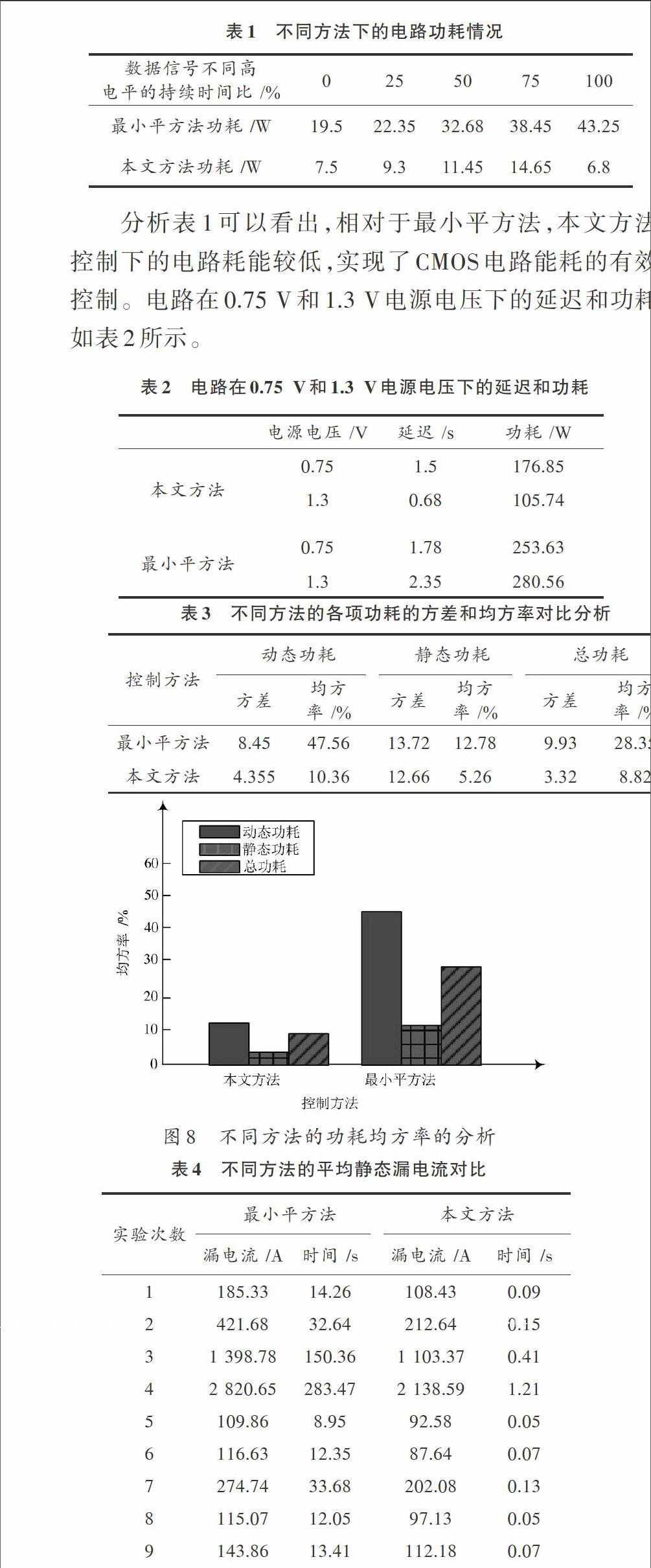

本文采用SMIC 0.11 μm CMOS工艺设计相关电路,通过HSpice软件进行仿真实验中,设置触发器的时钟频率为200 MHz,电源电压是1.0 V。实验在数据信号不同高电平持续时间下,对比分析本文方法和最小平方法的CMOS电路功耗情况如表1所示。

表1 不同方法下的电路功耗情况

分析表1可以看出,相对于最小平方法,本文方法控制下的电路耗能较低,实现了CMOS电路能耗的有效控制。电路在0.75 V和1.3 V电源电压下的延迟和功耗如表2所示。

分析表2可以看出,在相同电源电压下,采用本文方法控制的CMOS电路,其电路延时和功耗低于最小平方法。而在不同电源电压下,随着电源电压值的提高,不同方法下的CMOS电路延迟和功耗都增加,但是本文方法的延迟和功耗始终低于最小平方法。

两种方法下CMOS电路动态功耗、静态功耗和总功耗对比情况如表3所示。

表3 不同方法的各项功耗的方差和均方率对比分析

依据表3中的数据可以获取图8中不同方法的功耗情况对比结果,能够看出,不同方法的静态功耗的均方率低于动态功耗,并且动态功耗的波动幅度较高,而静态功耗的变化较为平稳。而本文方法的静态功耗略低于最小平方法,但动态功耗远远低于最小平方法,并且总功耗远低于最小平方法。说明本文方法控制下的CMOS电路功耗较低,具有较高的优势,能够满足CMOS电路节能控制的需求。

分析表4可得,相对于最小平方方法,本文方法的控制时间较低,能够极大提高控制效率,并且相差若干数量级。在本文方法下的CMOS电路漏电流低于最小平方法,说明本文方法的节能效果较优。

3 结 论

传统的大规模集成电路的功耗控制方法,存在运算量大、精确度有限的问题。因此,基于双阈值低功耗技术设计并实现CMOS电路中外部能耗控制模块,采用双阈值电压技术通过较低阈值的晶体管设计CMOS能耗控制模块,也就是低阈值模块。通过高阈值电压的NMOS管控制低阈值模块,降低电路的泄露电流,通过低阈值模块中的NMOS管对CMOS门单元电路进行管理,提高门单元电路的运行效率,降低总体CMOS电路的功耗。采用双阈值技术设计CMOS电路的单边沿脉冲触发器,对触发器的时钟响应电路进行优化,确保时钟翻转通过数字信号进行管理,极大降低了时钟翻转频率,减小了电路动态功耗。实验结果说明,所设计模块具有较高的控制效率,较低的延迟和功耗,其控制下的CMOS电路节能效果显著。

参考文献

[1] 李志远,曹贝,卜丹,等.互连线对CMOS电路性能的仿真分析[J].黑龙江大学自然科学学报,2014(5):697?700.

[2] 王玥.基于130 nm CMOS工艺UHF RFID系统中频率综合器的研究与设计[D].合肥:中国科学技术大学,2015.

[3] 肖奔,殷蔚.利用Cadence设计CMOS低噪声放大器[J].现代电子技术,2009,32(10):8?10.

[4] 张丽.磁隧道结模型及自旋转移力矩磁随机存储器设计技术研究[D].西安:西安电子科技大学,2014.

[5] 冯海涛,裴志强,刘宝娟.COMS电路的参数提取及模型建立[J].微处理机,2012,33(6):4?5.

[6] 张少强.基于CMV300的CMOS相机光电响应特性研究[D].北京:中国科学院研究生院,2015.

[7] 卢冲赢,徐立新,李建华,等.CMOS兼容高Q值微机电系统悬浮片上螺旋电感[J].兵工学报,2014,35(5):634?639.

[8] 王冠华.一种基于CMOS的I/F转换电路的设计与研究[D].哈尔滨:黑龙江大学,2014.

[9] 刘仲方.CMOS电路低功耗设计与优化研究[D].杭州:浙江大学,2015.