2.4 GHz CMOS低噪声放大器设计

程远垚,宋树祥,蒋品群

(广西师范大学电子工程学院,广西桂林541004)

2.4 GHz CMOS低噪声放大器设计

程远垚,宋树祥,蒋品群

(广西师范大学电子工程学院,广西桂林541004)

本文采用TSMC 0.18 μm CMOS工艺,设计了两款可工作在2.4 GHz频率上的窄带低噪声放大器(LNA)。两款LNA的电路结构分别为Cascode电路结构应用电流复用技术,以及应用正体偏置效应的折叠Cascode结构。所设计的两款窄带LNA的仿真结果表明,在2.4 GHz工作频率上,Cascode结构LNA在1.5 V供电电压下电路功耗为4.9 mW,增益为23.5 dB,输入输出反射系数分别为-16.9 dB与-16.3 dB,噪声系数为0.72 dB且IIP3为3.12 dBm;折叠Cascode结构LNA可在0.5 V供电电压下工作,功耗为1.83 mW,增益为23.8 dB,输入输出反射系数分别为-28.2 dB与-24.8 dB,噪声系数为0.62 dB且IIP3为-7.65 dBm,适用于低电压低功耗应用。

CMOS;窄带;低噪声放大器;Cascode;电流复用;正体偏置

0 引言

现代无线通信技术和通信标准不断进行着更新换代,通信设备性能要求也变得越来越复杂。在2.4 GHz工作频率上有着诸多无线射频应用,如3G通信协议LTE;Wi-Fi协议IEEE 802.11a/b/g/n;蓝牙Blueteeth IEEE 802.15.1等。这些无线射频应用对射频接收机提出了低成本、低功耗、高性能等要求,某些应用领域还要求在低供电电压下工作,因此CMOS工艺的射频电路成了近年的研究热点。而低噪声放大器(LNA)作为射频接收机前端的关键模块,更是一个重要的研究方向。

LNA的主要功能是在满足输入输出匹配与线性度要求基础上,在给出的功耗条件下为信号提供足够的放大增益,同时又能保持优异的噪声性能。输入输出匹配与滤波效果相关,良好的线性度能提高信号抗干扰能力,高增益有助于抑制后端电路噪声但会恶化线性度, LNA的噪声性能对接收机的噪声性能有决定性的作用。各性能的最佳值往往无法同时达到,因而CMOS工艺下的LNA设计需要权衡输入输出匹配、增益、线性度、噪声、功耗等各项性能,在不断折中过程中取最优效果。

本文采用TSMC 0.18 μm CMOS工艺,将带额外电容的源级电感退化Cascode结构为基础,以优化增益与工作电压为研究方向,设计2款可工作在2.4 GHz频率上的窄带LNA,其中LNA2可以在0.5 V电压下工作,达到低电压低功耗应用的性能要求。

1 输入匹配分析

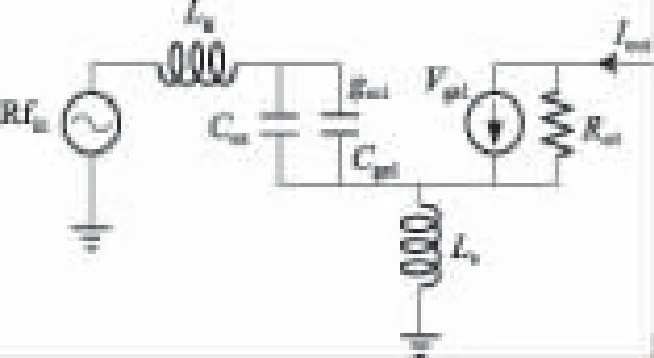

在窄带LNA的设计中,源级电感退化Cascode结构十分常见,因为该结构有着噪声系数较低、输入阻抗匹配性能好等优点,并且Cascode结构能够抑制晶体管寄生栅漏电容引起的米勒效应,从而提高电路的反向隔离性能。但其结构的缺陷在于不能满足噪声与输入阻抗的同步匹配,通常需要在噪声和输入阻抗匹配之间做折中。为了弥补电路缺点,可以在源级电感退化Cascode结构中的共源管栅源两端并联一个额外的电容Cex,因此获得额外的可调参数对电路的输入阻抗匹配进行调整,从而让电路可以在功耗受限条件下达到噪声与输入阻抗的同步匹配[1]。加入额外电容Cex的源级电感退化Cascode结构如图1所示,对应小信号等效电路图如图2所示。

图1 改进的Cascode结构Fig.1 cascode LNA

图2 小信号等效电路Fig.2 small-signal equivalent circuit

图3 Cascode结构应用电流复用技术Fig.3 Cascode with current-reuse technique

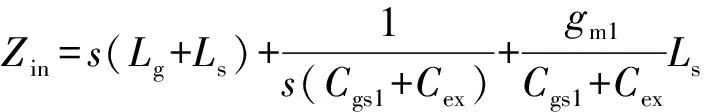

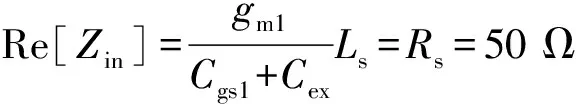

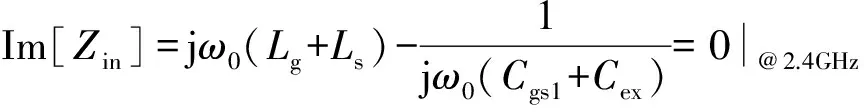

对图2的等效电路图进行简要分析,在忽略电感的寄生电阻和晶体管NM1的栅极电阻后,输入阻抗Zin公式为:

(1)

其中Cgs1是NMOS晶体管NM1栅源之间的寄生电容,gm1是晶体管NM1的跨导。为了在工作频率2.4 GHz上获得最大传输功率,需要输入阻抗Zin在2.4 GHz处的实部与信号源阻抗Rs(50Ω)相等,同时虚部为0。相关公式如下:

(2)

(3)

可以经由调节Ls的值来使Zin的实部Re[Zin]等于50 Ω,而Im[Zin]则可以通过调节Lg与Cex的值使其在2.4 GHz处发生谐振从而消除虚部。

2 技术研究

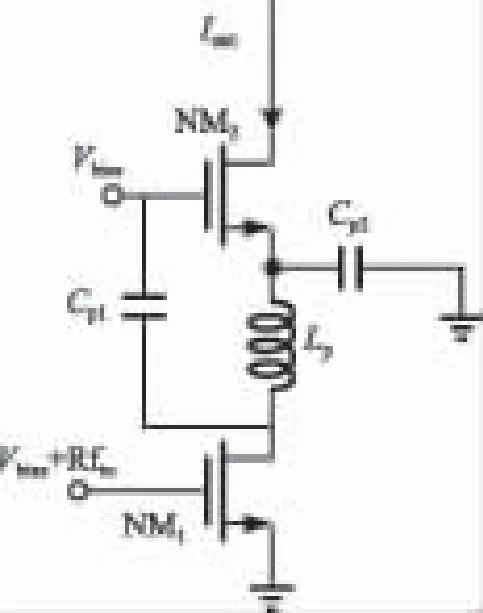

2.1 电流复用技术

电流复用技术旨在不提高电路功耗情况下提高电路的功率增益,此种技术在LNA的设计中有着广泛应用[2-3]。电流复用技术的主要思想是让多个放大级器件共用同一路偏置静态电流,因而能够在保持电路功耗的同时,增加放大级从而获得增益的提高。

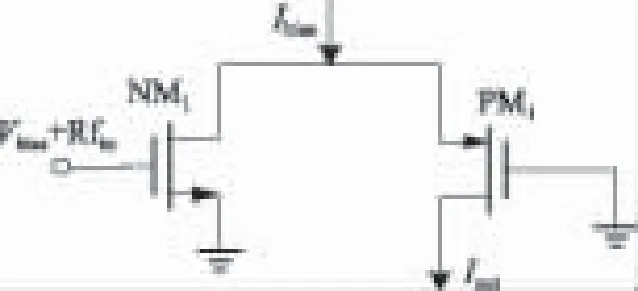

图3为简单Cascode结构应用电流复用技术后的电路结构图。对图3进行简单的电路分析。射频输入信号经过Cascode结构的共源级晶体管NM1进行信号放大后,到达设置在共栅级晶体管NM2前的电流复用结构。工作频率上的电容Cp1因为与Lp谐振而形成一条低阻抗通路,所以有用信号会通过电容Cp1进入共栅级晶体管NM2的栅极,从而使NM2转变成了第二级共源级晶体管,信号因此得到二次放大。电感Lp形成的高阻抗通路会阻隔高频信号进入NM2的源极,但偏置电流可以顺利流通,同时连通GND与NM2源级的电容Cp2也会消除源级的高频信号。基于以上工作原理,电流复用技术实现了同一路偏置电流条件下对信号进行2次有效放大的功能,这与传统的通过牺牲功耗为代价来提高增益的做法完全不同。电流复用技术提高了电路的效能,这在集成电路的设计中具有很大的优势。

2.2 折叠结构与正体偏置效应

近年来,一些新型射频应用(例如手持设备、无线遥感设备等)不仅要求系统正常工作时的供电电压能够降低至1 V以下,还要求电路的功耗非常低。为了满足低电压低功耗应用的要求,可以采用折叠结构与正体偏置效应等设计方法对电路进行低电压优化。

常见的共源共栅结构通常由2个NMOS晶体管层叠组成,因此工作电压往往要达到至少2倍阈值电压(VDD≥2Vth)才能使该电路正常工作。为了让电路能够在低供电电压下正常工作,可以把层叠共源共栅结构改成图4中的折叠共源共栅结构。用PMOS晶体管取代NMOS共栅级晶体管,并且在共源级与共栅级之间加入偏置电压,从而将两层晶体管层叠结构转化为两路单层晶体管结构,此时偏置电压只需要满足单层晶体管阈值电压(VDD≥Vth)即可让电路正常工作,供电电压可以低至1 V以下[4]。

图4 折叠Cascode结构Fig.4 Folded cascade

图5 NMOS管应用正体偏置Fig.5 Forward-body-bias technique in NMOS

虽然折叠共源共栅结构可以将供电电压下限降低至单个Vth,但是由于电路中其他器件的分压等原因,较低的供电电压可能会使MOS管无法保持工作在强反型区,因而造成增益与噪声性能遭受恶化。此时可以利用正体偏置效应,将MOS管的阈值电压降低,从而进一步降低供电电压。

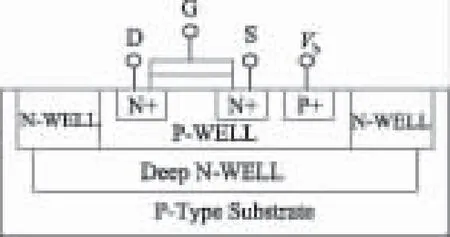

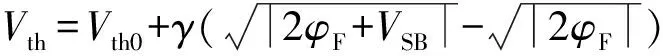

对图5的NMOS晶体管剖面图进行与阈值电压Vth相关的分析。我们知道NMOS晶体管的工作原理如下:对栅端施加正电压Vg,当Vg逐渐增大时,由于G端和衬底会形成一个电容器,此时衬底内部的空穴将远离G端,产生与G端正电荷对应的“耗尽层”负电荷。Vg电压持续升高到一定程度时,S端的电荷载流子就能够通过“耗尽层”流向D端,此时可以认为该NMOS晶体管“导通”,其内部产生了电荷载流子“沟道”,当前NMOS晶体管的G端电压与S端电压差就是“阈值电压”。考虑到体偏置效应,阈值电压Vth的公式可写成[5]:

(5)

其中:Vth0是忽略体偏置效应的晶体管阈值电压;γ是体偏置效应系数;VSB是S端和衬底的电势差;φF是与衬底掺杂浓度成正比的费米系数。式(5)表明,当VSB变大Vth也会随之变大,当VSB变小Vth也会随之变小,因此可以在衬底端施加正偏置电压使得VSB减小,从而减小Vth,最终降低电路对偏置电压VDD的要求。深阱CMOS工艺的射频集成电路设计中,每个晶体管的衬底与整个芯片衬底都是隔绝的,所以对晶体管施加独立的偏置电压并不会影响到其他元器件。

3 LNA电路设计

带额外电容Cex的源级电感退化Cascode结构解决了噪声匹配与输入阻抗匹配无法同时达到的问题,又兼有噪声较低、阻抗匹配性能较好、反向隔离好等优点。基于此种电路结构,本文结合电流复用技术,经过改进和优化,设计了第一款窄带LNA,其完整电路结构图如图6所示。

图6中Cin为隔直电容,通常取值几个pF,用于抑制高频信号对电路工作点的影响。Lg、Cex、Ls与NM1的寄生电容Cgs1组成输入匹配网络,可以通过调节Ls与Cex等器件的值令输入阻抗达到匹配。Cp1、Lp与Cp2组成电流复用级间匹配网络,通过调节适当的值,达到让NM2由共栅级转变为共源级的目的,从而令2个共源级放大管在同一路偏置电流下正常工作。Ld为负载电感,与Cout组成输出匹配网络。晶体管NM3与NM4组成偏置电路,NM3与NM1构成电流镜结构让NM1偏置电压设置在670 mV,Rbias1与Rbias2为偏置电阻,取值通常为几kΩ,是为了避免信号通路受到偏置电路的影响。

图6 LNA1的完整电路结构图Fig.6 Complete schematic of the LNA1

图7 LNA2的完整电路结构图Fig.7 Complete schematic of the LNA2

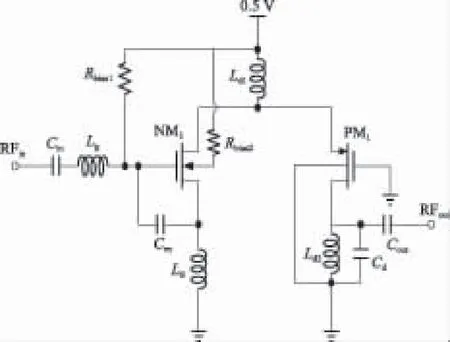

因为常见的Cascode结构LNA无法满足工作电压低于1 V的条件,本文基于低电压低功耗应用的要求,采用折叠Cascode结构与正体偏置技术,设计了第二款窄带LNA,其完整电路结构图如图7所示。图7中NM1与PM1组成折叠Cascode结构,输入匹配网络与LNA1类似,输出匹配网络由Ld2、Cd与Cout构成,调节Ld2与Cd可以达到输出阻抗匹配。为了协调2个放大级,本文采用Ld1作为负载电感,不但为第一级提供负载,并且为电路提供了偏置。VDD经由Rbias2为NM1的衬底提供正电压偏置,而PM1衬底直接接地,2个晶体管由于正体偏置效应使得阈值电压Vth得到了降低。结合折叠结构对工作电压的优化,只需0.5 V的供电电压即可让电路正常工作。

4 电路仿真及实验结果

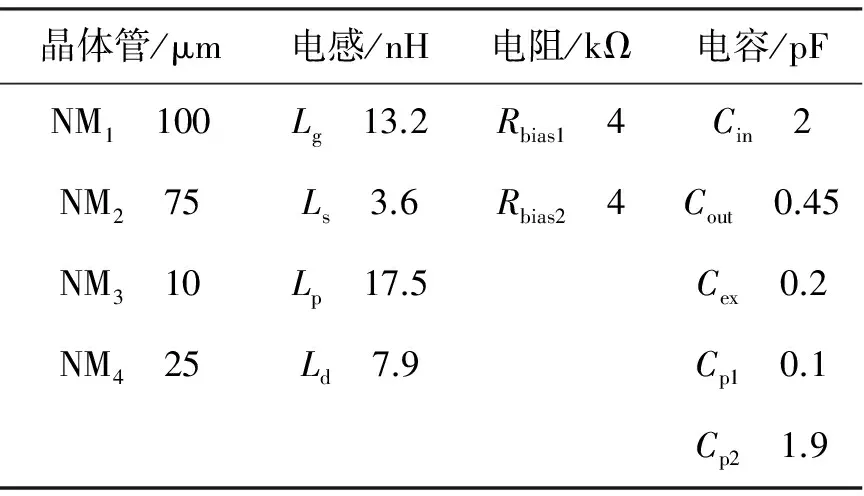

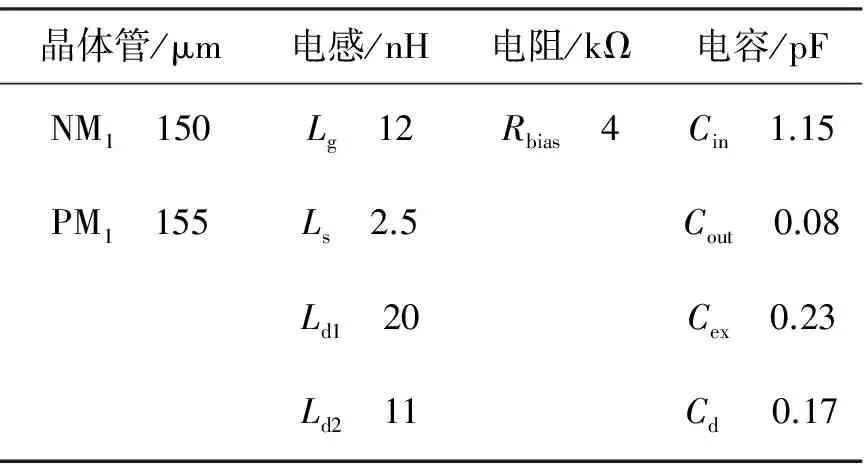

根据图6与图7所示的LNA电路结构原理图,采用cadence公司的 SpectreRF分别对2款LNA进行仿真。LNA1与LNA2的器件参数见表1、表2。

表1 LNA1的设计参数

表2 LNA2的设计参数

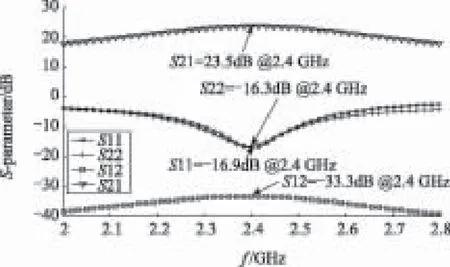

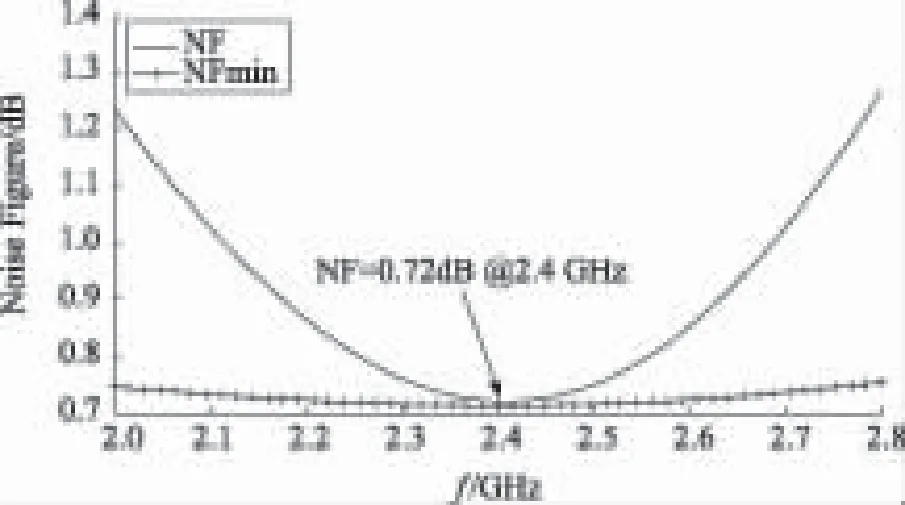

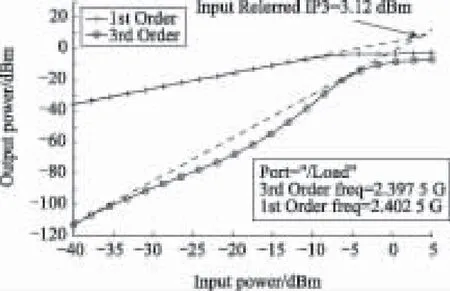

在1.5 V直流电压下对LNA1进行仿真,电路的直流功耗为4.9 mW。图8显示了LNA1的S参数仿真结果:在工作频率2.4 GHz处,LNA1的前向增益S21达到23.5 dB,输入反射系数S11与输出反射系数分别为-16.9 dB和-16.3 dB,反向增益为-33.3 dB,由此看出LNA1的输入输出阻抗匹配均良好,增益性能优良。从图9中可以观察到,在工作频率2.4 GHz上噪声系数曲线达到最低点,此时噪声系数仅为0.72 dB,与最低噪声系数曲线十分接近,说明电路的噪声匹配程度良好。图10显示的是电路的输入三阶交调点,在2.4 GHz上达到3.12 dBm,说明电路有着良好的线性度。

图8 LNA1 S参数仿真Fig.8 Simulated S-parameter of LNA1

图9 LNA1噪声系数仿真Fig.9 Simulated noise figure of LNA1

图10 LNA1 线性度仿真Fig.10 Simulated IIP3 of LNA1

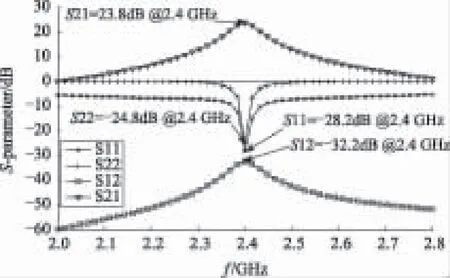

图11 LNA2 S参数仿真Fig.11 Simulated S-parameter of LNA2

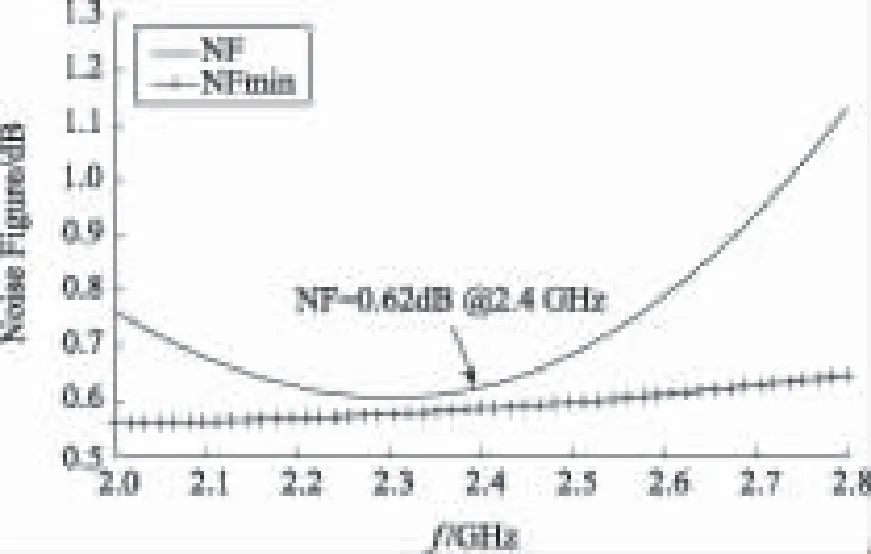

图12 LNA2噪声系数仿真Fig.12 Simulated noise figure of LNA2

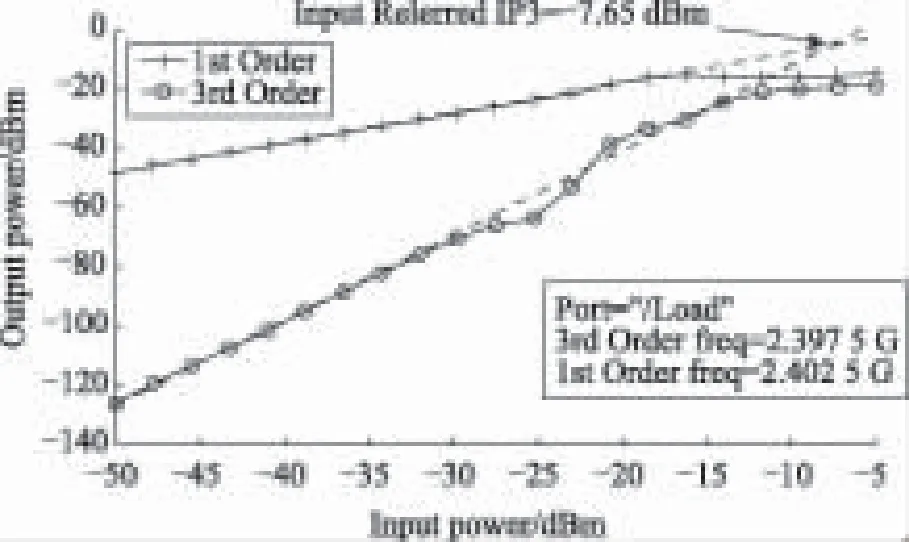

图13 LNA2 线性度仿真Fig.13 Simulated IIP3 of LNA2

得益于折叠结构与正体偏置效应,LNA2的工作电压降低到了0.5 V。在0.5 V直流电压下对LNA2进行仿真,电路的直流功耗为1.8 mW。由图11可观察到,在工作频率2.4 GHz处,LNA2的前向增益S21达到23.8 dB,输入反射系数S11与输出反射系数分别为-28.2 dB和-24.8 dB,反向增益为-32.23 dB, LNA2的输入输出阻抗匹配性能良好,而增益并没有因为工作电压降低而恶化,保持在了高增益水平。从图12中可以观察到,在工作频率2.4 GHz上噪声系数仅为0.62 dB。图13中可看到,电路的输入三阶交调点在2.4 GHz上为-7.65 dBm,说明折叠结构在一定程度上恶化了线性度。

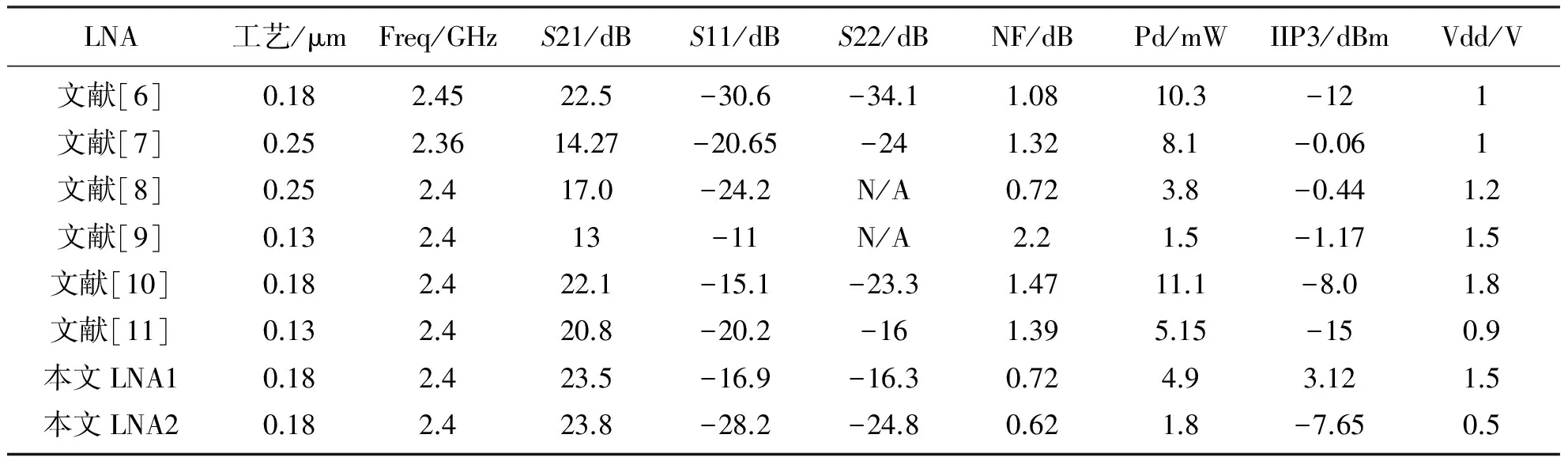

表3是把本文所设计的2款窄带LNA与此前发表的LNA的主要仿真性能作比较。由此表可以看出:在工作频率2.4 GHz上,本文所设计的2款LNA均表现出高增益低噪声的特点,且输入输出阻抗匹配良好,此外LNA1的线性度性能优良,LNA2则能在低至0.5 V电压下工作,满足低电压低功耗应用的要求。

表3 本文提出的LNA与此前发表的LNA性能比较

5 结论

本文采用TSMC 0.18 μm CMOS工艺设计了2款工作频率为2.4 GHz的窄带LNA,并进行了电路仿真。其中LNA1采用Cascode结构作为主要结构,并使用电流复用技术对增益进行优化,仿真结果显示在2.4 GHz上,增益达到23.5 dB,输入输出匹配良好,噪声系数为0.72 dB,1.5 V供电电压下功耗为4.9 mW,IIP3值为3.12 dBm。LNA2采用折叠Cascode结构与正体偏置效应降低工作电压需求,仿真结果显示LNA2能在0.5 V电压下正常工作,功耗仅为1.8 mW,增益为23.8 dB,噪声系数0.62 dB,输入输出匹配优良。本文所设计的2款窄带LNA在2.4 GHz工作频率上各性能指标均有很好的兼顾,具备了较高增益、较低噪声、良好输入输出匹配的特性,LNA2适用于低电压低功耗射频应用。

[1] NGUYEN T K,OH N J,CHOI H C,et al. CMOS low noise amplifier design optimization technique[C]// The 2004 47th Midwest Symposium on Circuits and Systems:Volume 1.Piscataway NJ:IEEE Press,2004: 185-188.DOI: 10.1109/MWSCAS.2004.1353928.

[2] LIN Yijing,HSU S S H,JIN Junde,et al.A 3.1-10.6 GHz ultra-wideband CMOS low noise amplifier with current-reused technique[J]. IEEE Microwave and Wireless Components Letters,2007,17(3):232-234. DOI:10.1109/LMWC.2006.890503.

[3] HAM J H,LEE J Y,YUN T Y.21-dB gain ultra-wideband complementary metal-oxide semiconductor low-noise amplifier with current-reuse technique[J].IET Microwaves Antennas & Propagation,2011,5(12):1495-1501.DOI:10.1049/iet-map.2010.0438.

[4] HSIEH H H,WANG J H,LU L H.Gain-enhancement techniques for CMOS folded cascode LNAs at low-voltage operations[J].IEEE Transactions on Microwave Theory and Techniques,2008,56(8):1807-1816.DOI:10.1109/TMTT.2008.927304.

[6] 陈冠,陈向东,石念. 2.4G CMOS低噪声放大器设计[J].微电子学与计算机,2009,26(5):235-238.

[7] 徐跃,杨英强. 1V高线性度2.4GHz CMOS低噪声放大器[J].电路与系统学报,2009,14(4):97-100.

[8] HAGHIGHITALAB D,VASILEVSKI M,ABOUSHADY H.LNA automatic synthesis and characterization for accurate RF system-level simulation[C]//2010 53rd IEEE International Midwest Symposium on Circuits and Systems.Piscataway,NJ:IEEE Press,2010:938-941.DOI:10.1109/MWSCAS.2010.5548785.

[9] MANJULA S,SELVATHI D.Design of low power 2.4GHz CMOS cascode LNA with reduced noise figure for WSN applications[J].Wireless Personal Communications,2013,70(4):1965-1976.DOI:10.1007/s11277-012-0790-4.

[10] YANG Laichun,YAN Yuexing,ZHAO Yiqiang,et al.A high gain fully integrated CMOS LNA for WLAN and Bluetooth application[C]//2013 IEEE International Conference of Electron Devices and Solid-State Circuits.Piscataway,NJ:IEEE Press,2013:1-2.DOI:10.1109/EDSSC.2013.6628229.

[11] TAIBI A, SLIMANE A,TEDJINI S A,et al.A 0.9V low power reconfigurable CMOS folded cascode LNA for multi-standard wireless applications[C]//2014 9th International Design and Test Symposium. Piscataway,NJ:IEEE Press,2014:185-188.DOI:10.1109/IDT.2014.7038610.

(责任编辑 黄 勇)

Design of 2.4 GHz CMOS Low-noise Amplifier

CHENG Yuanyao,SONG Shuxiang,JIANG Pinqun

(College of Electronic Engineering,Guangxi Normal University,Guilin Guangxi 541004,China)

In this paper, two narrowband low-noise amplifiers (LNAs) are designed, which can operate in the 2.4 GHz frequency with TSMC 0.18 μm CMOS technology. One of the circuit structures is Cascode structure with current-reuse technique,and the other is folded Cascode structure with forward-body-bias technique. The simulation results of the designed narrowband LNAs show that,in the 2.4 GHz frequency,Cascode LNA consumes 4.9 mW from a 1.5 V DC supply,gain is 23.5 dB,input and output reflection coefficients are -16.9 dB and -16.3 dB,noise figure is 0.72 dB and IIP3 is 3.12 dBm; and the folded Cascode LNA can operate under 0.5 V DC supply,power consumption is 1.83 mW,gain is 23.8 dB,input and output reflection coefficients are -28.2 dB and -24.8 dB,noise figure is 0.62 dB and IIP3 is -7.65 dBm, which is suitable for low voltage and low power applications.

CMOS;narrowband;low-noise amplifier;Cascode;current-reuse;forward-body-bias

10.16088/j.issn.1001-6600.2016.03.002

2016-01-15

国家自然科学基金资助项目(61361011);广西自然科学基金资助项目(2014jjAA70058);广西高等学校优秀中青年骨干教师培养工程资助(GXQG022014002)

宋树祥(1970—),男,湖南双峰人,广西师范大学教授,博士。E-mail:songshuxiang@mailbox.gxnu.edu.cn

TN432

A

1001-6600(2016)03-0007-07