高速LVDS信号接收及基于FPGA的串并转换的设计

蒋红阳

摘 要

主要介绍高速LVDS差分信号转单端信号接收模块的设计,通过TI 公司的SN65LVDS386芯片,接收差分信号并转换为单端信号,并基于FPGA实现串行数据转换为并行数据。

【关键词】LVDS信号接收 FPGA 串并转换

1 引言

随着信息技术的发展,数据量越来越大。低压差分信号传输技术(Low Voltage Differential Signaling,LVDS)是一种满足当今高速数据传输应用的新型技术,它使得信号能在差分PCB线对或平衡电缆上以几百兆bps的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗。在后端需要CMOS数字信号或者其他单端信号时,需要將差分信号转换为单端信号,LVDS差分信号接收模块的设计非常重要,信号质量的接收直接影响整个系统的稳定性,因此需要设计可靠的信号接收电路将LVDS差分信号转换为单端信号。

FPGA(Field-Programmable Gate Array),即现场可编程阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。以VHDL等硬件描述语言所完成的电路设计,可以经过综合和布局,快速的烧写至FPGA上进行测试,是现代IC设计验证的技术主流。系统设计师可以根据需要通过可编程的连接把FPGA内部的逻辑块连接起来,一个出厂后的成品FPGA逻辑块和连接可以按照设计者的意图而改变,所以FPGA可以完成所需要的逻辑功能。在本文中通过FPGA编程,可以实现高速信号的串并转换。

2 工作原理

2.1 LVDS接口简介

LVDS接口又称RS-644总线接口,是20世纪90年代出现的一种数据传输和接口技术。LVDS即低电压差分信号,该技术的核心是采用较低的电压摆幅高速差动传输数据,可实现点对点或一点对多点的连接,具有低功耗、低误码率、低串扰和低辐射等特点,在对信号完整性、低抖动及共模特性要求较高的系统中得到了广泛应用。LVDS具有许多优点:

(1)终端适配容易;

(2)功耗低;

(3)具有fail-safe特性确保可靠性;

(4)成本低;

(5)传送速度高。

2.2 芯片简介

LVDS信号有更低的共模噪声和共模抑制。若直接在LVDS信号中取单端信号,则取得的单端信号中可能仍然包含一定的共模噪声。此单端信号在经过系统后续放大电路的放大处理后,噪声更为明显。因为直接在LVDS信号中取的单端信号的幅值不高,需要后端放大电路更高的增益,增加了系统设计的难度。

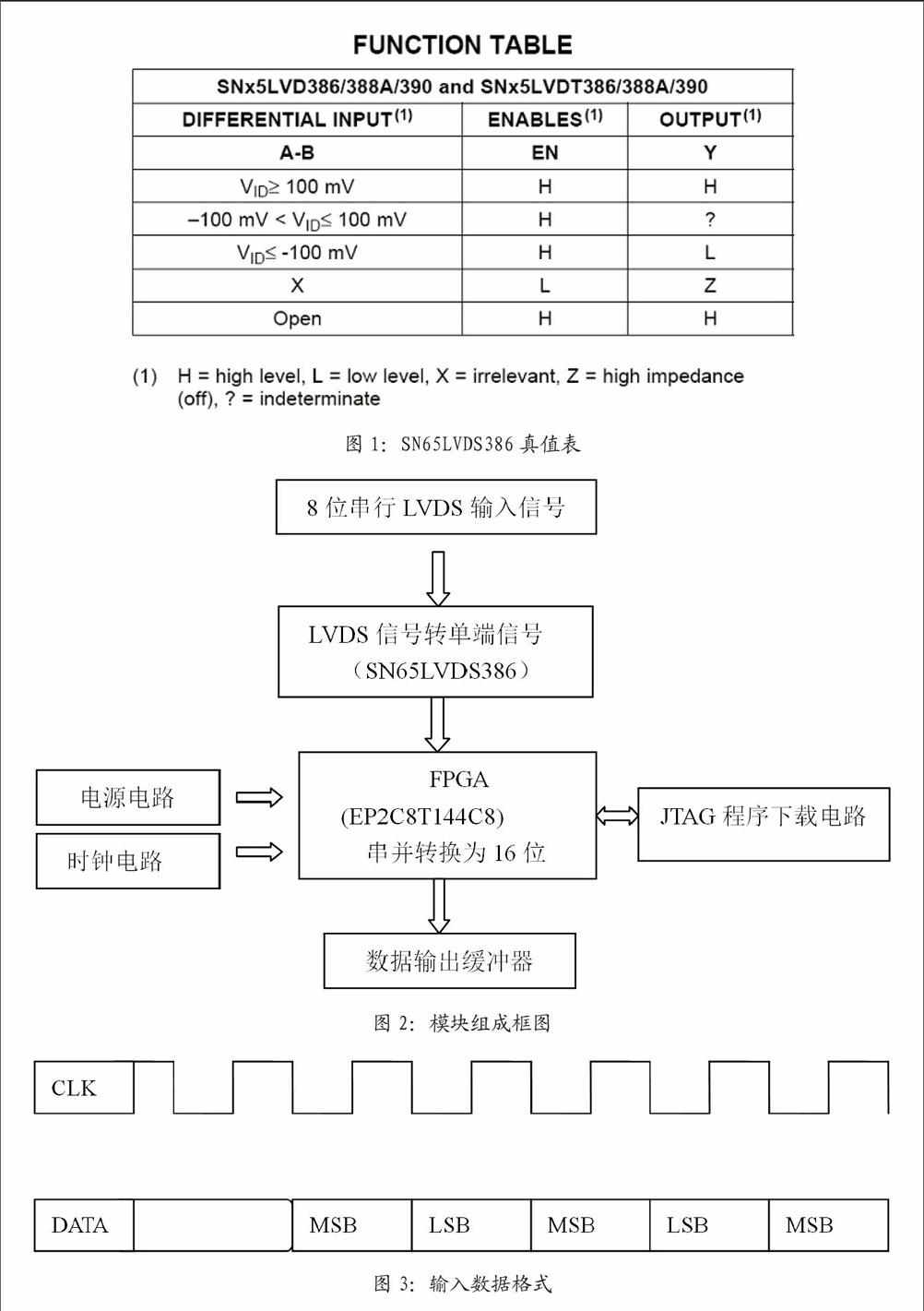

SN65LVDS386是德州仪器公司一款16通道LVDS接收器。此款LVDS接收器芯片的性能达到甚至超出了ANSI TIA/EIA-644标准的要求,芯片设计的信号速度可达630Mbps,此芯片使用3.3V单电源供电,典型的传输延迟为2.6ns。具有fail-safe功能,即当芯片引脚对上没有差分信号输入出现或者输入很小时,这种往往出现在输入为高阻态或者输入线缆没有连接好的状态时,当这种情况发生时,LVDS信号接收器将输入信号对的每个引脚都通过300k欧姆的电阻拉高到Vcc电平附近。fail-safe特点是:使用一个与门将输入信号保持到门限2.3V上,不管输入差分电压是多少,都使得输出保持为高电平。其真值表如图1所示。

2.3 Altera公司的FPGA芯片介绍

Altera公司的FPGA设计开发技术在业内首屈一指,相对于其他公司来说有一定的优势,其产品应用也十分广泛。Altera公司的FPGA分为两大类,一种是cyclone系列的FPGA,侧重于高性价比应用,容量中等,性能满足一般的逻辑设计要求。还有一种是侧重于高性能应用,容量大,性能满足各类高端应用,如Stratix系列。根据我们实际的应用情况,结合性价比考虑,决定采用CycloneII系列的FPGA。

CycloneII FPGA器件扩展了低成本FPGA的密度,最多达68416个逻辑单元(LE)和1.1M比特的嵌入式存储器,其内部的逻辑资源可以用来实现复杂的应用。本设计选择的EP2C8T144C8是该系列的一款典型产品,接口支持差分I/O,LVDS标准支持接收端最高805Mbps数据速率,发送端最高622Mbps;支持各种单端I/O标准,如当前系统中常用的LVTTL、LVCOMS、SSTL、HSTL、PCI和PCI-X标准。

3 硬件设计

3.1 电路组成

LVDS差分接收串并转换模块框图如图2所示。

3.2 工作原理

本设计中前端输入的数据信号为16位串行LVDS信号,在时钟CLK的控制下,高8位数据MSB和低8位数据LSB连续串行输。其输入信号的数据格式如图3所示。

LVDS串行信号通过传输接插件进入芯片SN65LVDS386,此芯片将LVDS差分信号转换为单端信号,转换为单端信号后,送入FPGA芯片(EP2C8T144C8)。FPGA通过时序控制将连续两次输入的8位信号转换为16位并行信号,并送入数据输出缓冲器芯片。模块的FPGA程序下载电路配置为JTAG下载电路。因为输入信号时钟不超过10MHz,故FPGA时钟电路选择20M晶振。根据电路时钟速率和器件功耗估算,设计选择电源芯片为凌特LT1764A系列。

3.3 软件设计

串并转换是指将一个连续信号元序列变换成为表示相同信号的一组相应的并行出现的信号元过程。本模块设计的串并转换方法为,在第一个时钟下降沿将高8位数锁存为FPGA内16位寄存器的高8位,在下一个时钟时锁存低位,同步将16位数据送出FPGA。FPGA送出的数据通过数据缓冲器74LVC16244A进入后端电路。

串并转换模块软件在Quartus II 7.2 (32-Bit)开发环境下,使用verilog HDL语言实现。

4 结论

本文介绍了高速LVDS信号转单端信号的接收和使用FPGA实现信号的串并转换。TI公司的SN65LVDS386作为数据接收器,特点是接收速度快、信号传输稳定、误码率低。使用FPGA实现串并转换原理及实现简单可靠,系统工作可靠。

参考文献

[1]卿启新.基于FPGA的LVDS视频信号转换系统设计实现[D].广州:华南理工大学,2011.

[2]HIGH-SPEED DIFFERENTIAL LINE RECEIVERS.Texas Instruments. September ,1999.

[3]CycloneII Device Handbook.Altera Corporation. August,2012.

作者单位

华中光电技术研究所—武汉光电国家实验室 湖北省武汉市 430073