高速数字电路中的信号传输性

宁宏新

摘 要

目前,高速数字电路的应用越来越广泛,所以高速数字电路在前期设计和生产时,对于高速数字电路中的信号传输性问题应该给予重视,因为高速数字电路信号传输性是否完整会对相关的电子设备和元器件正产工作产生重要的影响。本文在查阅大量相关资料的前提下,首先论述了高速数字电路的基本概况,其次探讨了影响高速数字电路信号传输性的原因,并且提出相应的解决措施。

【关键词】高速数字电路 传输性 解决措施

通常情况下,绝大多数人以为电路运行时的效率高于50MHz时,线路就能够被称作高速电路。但是,真正的定义是依据信号沿变化的真实速度,因为信号沿变化的速度与高频传输效应的产生有一定的关系,速度越快,发生的概率就会越高。当线路在实际建设中时,影响高速数字电路信号传输性的因素有很多,例如信号的反射现象、地弹以及线路之间的串扰都会对其产生影响。

1 高速数字电路的概况

高速数字电路在前期设计时不仅要准确的考虑逻辑上的准确性,其他的因素也要考虑在内,比如电路中的电器容量、电磁感应以及电阻等,相对于低速电路,高速电路在前期设计时不仅要注重提高导线的感抗和导线间的感性耦合,对于容抗和容性耦合也要重视。每一根导线都有自身体积方面的特征,随之也会有相对应的电感电容,所以会给完整的电路带来相应的感抗与容抗(X1)。针对两者数值之间的计算公式一般有如下两个:

Xc=1/(2πFkneeC)=Tr/(πC) (1)

X1=Lπ/Tr (2)

公式中的 表示电路导线的临界频率,电容就是公式中的字母C,公式中L表示为电感,通过上述的公式可知,Fknee代表的数值较大时,或者说当信号的变化速度快时,感抗和容抗的数值是不易忽略。

当有两个导体时,前提条件是两个导体不能进行连接,在其中一个导体上施加一定电压时,在这个导体的周围会形成一个电场,而且形成的电场会对导体上电荷的流动产生一些反应,因此会出现容性耦合的现象。当导体内存在流动的电荷时,在导体周围便会产生一定的磁场,与此同时,产生的磁场也会对流动的电荷发生一定的反应,从而出现感性耦合现象,虽然感性耦合和容性耦合一般会不作考虑,可是在导体中电流变化比较快的情况下,就要考虑对信号传输产生的影响。通过以上论述的特点,高速电路在设计的时候应该考虑信号反射和信号之间的串扰给电路信号传输性带来的不良影响。

2 影响高速数字电路传输性的问题与措施

2.1 信号反射问题与解决措施

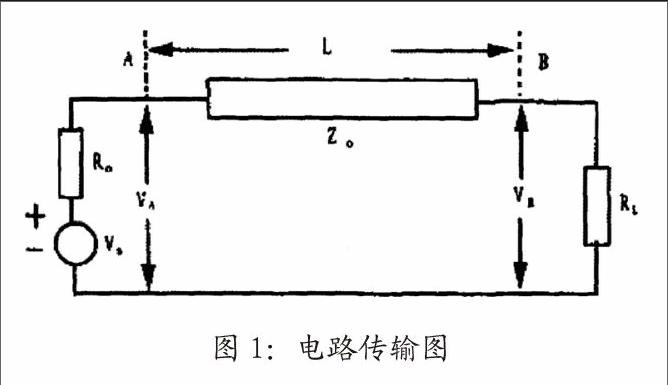

通常情况下,当传输线内的阻抗没有连续时,便会出现信号反射的现象。例如图1,图1显示的是电路传输图,图中的R0表示为信号的驱动源内阻,Z0表示为传输线L内的特性阻抗,负载阻抗便是途中显示的RL。

在现实性况下,一般会用R0=Z0=RL来表示,在这种情况下,传输阻抗表现出来的状态是连续性的,反射的现象不会发生。假如RL>R0,负的一端变回产生过剩的能量,过剩的能量便会反射到源端,一般称这种现象为欠阻尼,如果兩端之间的关系发生相反时,负载便会消耗更多的能量,当反射给前端后,前端就会继续输送更多的能量,一般称这种情况为过阻尼。这两种情况的出现都会发生反向传播形式的波形,进而对信号的传输性产生干扰。

但对于电路和电路板来说,他们的非理想特性会产生传输性损耗、非无穷大阻抗以及非零输入阻抗,这些情况的发生会使得信号震荡的状态表现为一阻尼震荡。因此,电路信号反射在现实中出现时,观察的重点应该放在第一次发射和第二次反射是否正常,观察后在具体分析发生的原因,然后在对症下药。

2.2 地弹问题和解决措施

当数字电路在运行状态下时,一般只存在高电平电压和低电平电压。如果数字逻辑输出的电压由高变低时,这个电子器件的接地管脚便会发生放电反应,进一步发展便会产生开关电流。当数字电路的传输速度越快,所要求的开关时间便会越短,当绝大多数的开关电路一起由高电压转变到低电压时,这些开关电路便会造成逻辑地电压出现波动,一般称这种现象为地弹。地弹对电路传输的影响主要表现在双时钟反应,这种反应会对寄存的输入的数据产生错误,进而造成逻辑上的错误判断。通常情况下要从地弹造成的影响来分析,一般会降低负载器件的数量,或者使用驱动隔离器或者串接10Ω到30Ω电阻的方式来降低地弹所带来的干扰。

2.3 串扰问题及解决措施

串扰自身就是比较复杂的电路现象,造成这种现象的原因有很多,当两个导体电路内的电路方向不一样时,串扰会比电流方向一样时大很多,而且会增加干扰信号的频率,带来的串扰辐值也会因此而提升。解决措施要从三方面入手,

(1)将两线的距离尽可能的加大。

(2)将底层和信号线之间的垂直距离尽可能的缩短。

(3)将两线的平行长度能可能的缩小。

要注意的是,最好的办法就是增加两线之间的距离。其他方法的效果一般不太明显。

3 结语

综上所述,影响高速数字电路信号传输性因素较多,要想保证信号传输的完整性就要从电路设施在设计和建设过程中的每个细节进行分析,例如电源地的稳定、材料的导电性、信号层的次序以及连线的长度等。所以,在电路建设过程中,相关的工作人员要认真仔细的建设电路设施,让人们能够享受到高效和稳定的电网和电压,为人们的生活保驾护航。

参考文献

[1]张靖.高速数字电路信号完整性方针设计与验证[D].西安电子科技大学,2013.

[2]邓集杰,刘铁根,褚备等.高速视频处理系统的信号完整性分析[J].电子测量与仪器学报,2009,23(06):34.

[3]董刚,李跃民,杨银堂.两相邻耦合ELC互联的串扰估计[J].电路与系统学报,2006,11(02):150.

[4]曹燕丽,孟利民.高速电路中传输耦合的反射和串扰仿真[J].杭州电子科技大学学报,2009,23(6):34.

作者单位

广西师范学院师园学院 广西壮族自治区南宁市 530000