基于FPGA的FLASH控制器的设计

摘 要

为了解决雷达数字波束形成系统中数据的存储问题,本文设计了基于FPGA的FLASH控制器。通过有限状态机实现对FLASH的读写控制,在modelsim中对设计进行了仿真验证,并通过硬件测试证明了设计的正确性和可靠性。该方法充分利用了FPGA设计灵活、FLASH存储读写速度快的优势,具有成本低廉,兼容性强,易于工程实现的特点。

【关键词】FPGA FLASH 控制器

随着数字阵列雷达的高速发展,对数字波束形成的要求越来越高,在实时处理过程中有大量数据需要存储。由于FPGA本身存储容量非常小,无法满足数字波束形成处理过程中的存储需求。为解决这一问题,采用FPGA+FLASH的硬件架构,以FPGA实现对FLASH的存储控制,极大的扩展系统存储容量。

本文以Altera公司FPGA芯片EP4SGX230和AMD公司AM29LV065D为例,详细说明了基于FPGA的FLASH控制器的设计,利用Verilog HDL语言编写同步有限状态机实现了FPGA与FLASH存储的接口操作。

1 FLASH控制器硬件设计

FLASH芯片选用AMD公司AMD29LV065D型号,该型号芯片的主要特点有:3.3v单电源供电,内部进行编程和擦除操作;64Mbit存储容量,内部分为128个扇区,可读每个扇区单独进行读写和擦除操作,而不影响其他扇区的数据;超低能耗,典型读操作只需消耗9mA,典型擦除/编程操作只需消耗26mA,典型静态模式只需消耗200nA;操作简单,只需按规定的时序向FLASH内部命令寄存器写入指令序列即可。

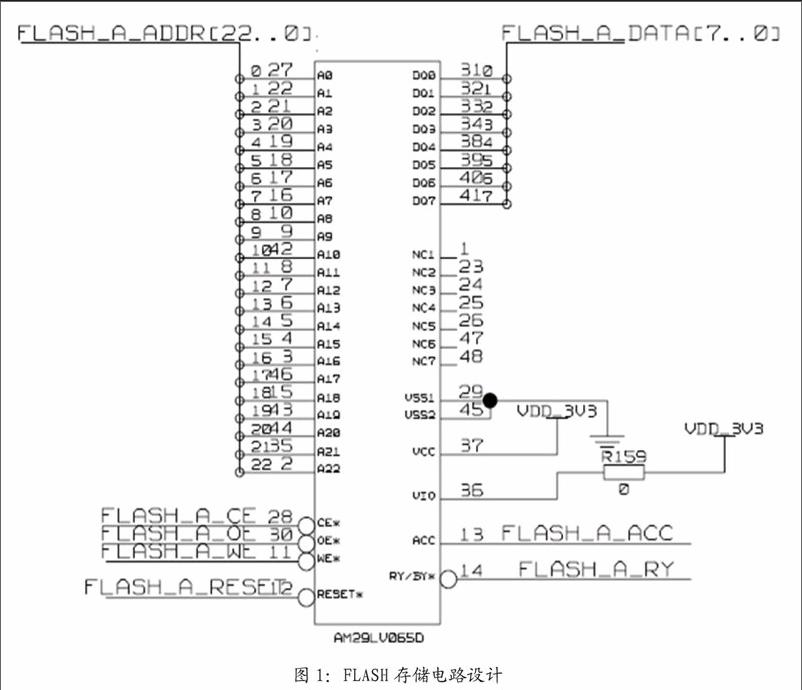

AMD29LV065D芯片的A[22:0]为地址总线,DQ[7:0]为三态数据总线,其它信号为芯片读写控制和操作标志信号。FPGA的引脚除电源、时钟和复位以及几个配置时钟引脚外,其余引脚均可作为通用I/O使用。因此,与FLASH连接时,只需将FPGA的普通I/O引脚与FLASH引脚相连即可。FLASH电路图如图1所示。

2 FLASH读写模块设计

AMD公司AM29LV065D芯片有90ns,100ns和120ns等3个速度等级,可充分满足FPGA的工作时序要求。根据芯片的数据手册采用Verilog HDL语言设计有限同步状态机实现FLASH控制指令序列的时序状态转换,以完成对FLASH的擦除、读、写等操作。

2.1 FLASH擦除操作

擦除操作分为扇区擦除和整个芯片擦除,整片擦除的过程为:第一个时钟周期在地址XXXH写入AAH数据,接着第二个时钟周期在地址XXXH写入55H数据,第三个时钟周期在地址XXXH写入80H数据,第四个时钟周期在地址XXXH写入AAH,第五个时钟周期在地址XXXH写入55H,第六个时钟周期在地址XXXH写入10H。扇区擦除的过程与整片擦除的过程一致,只是第六个时钟周期在地址处写入相应扇区地址,数据处写入30H。然后等待芯片内部完成擦除工作即可。FLASH扇区擦除或整个芯片擦除完成后,相应扇区或整个芯片内部所有数据位全部置成‘1。

2.2 FLASH写操作

FLASH芯片的写操作包括擦除操作和编程操作。在对相应扇区进行写操作之前,必须先将该扇区的数据进行擦除处理。在擦除操作后整个扇区的数据均被置为FFH,即所有數据位均处于‘1的状态。在写数据时仅能使对应单元的数据位由‘1变为‘0。

擦除操作如2.1节所述。编程操作过程为:第一个时钟周期在地址XXXH写入AAH数据,接着第二个时钟周期在地址XXXH写入55H数据,第三个时钟周期在地址XXXH写入A0H数据,第四个时钟周期在地址相应的地址写入相应的数据。即可完成对单个数据的写操作,循环多次可实现对整个扇区的写操作。

2.3 FLASH读操作

FLASH读操作相对较简单,其过程为:输入地址XXXH,读取输出数据XXH即可。

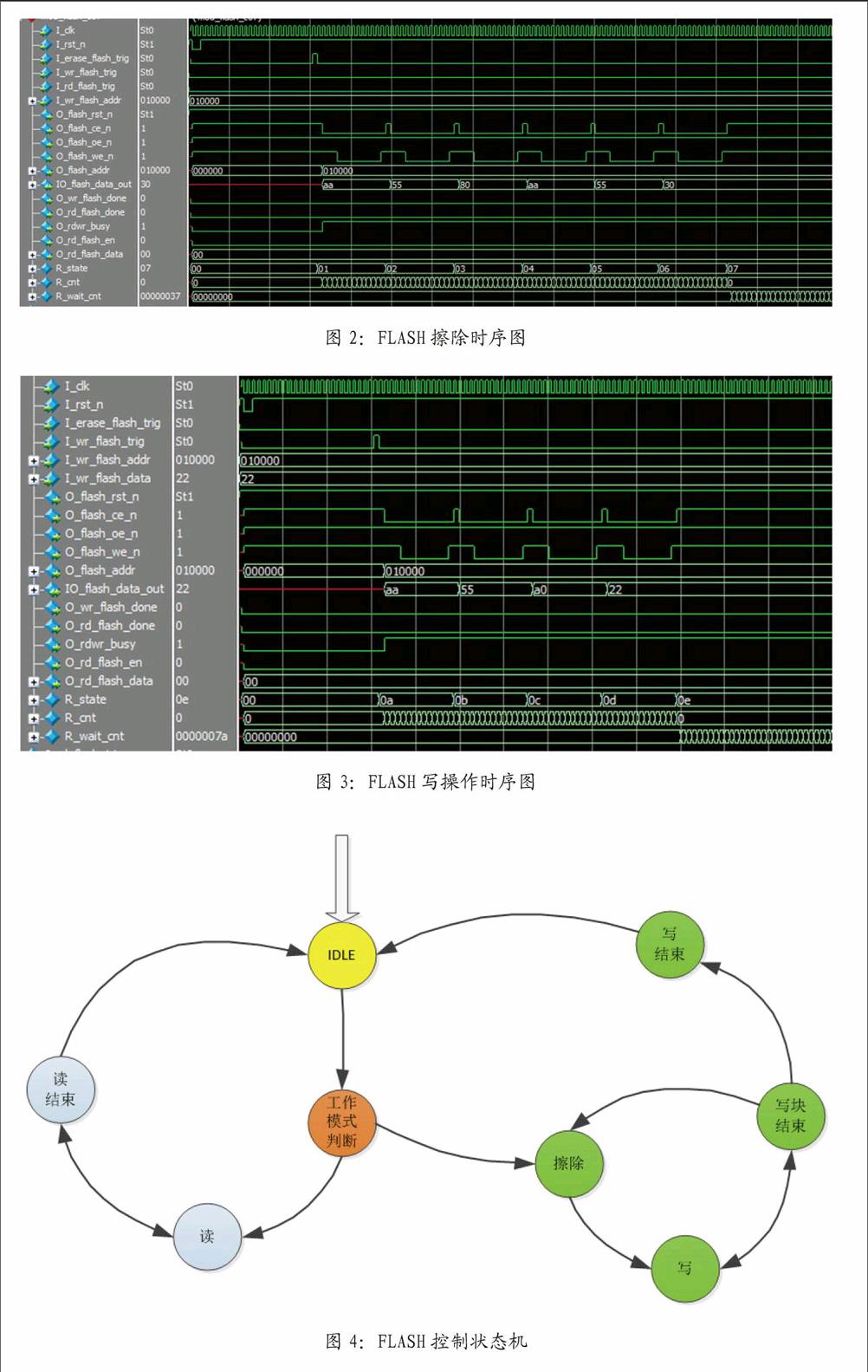

2.4 FLASH控制状态设计

利用有限状态机来实现对FLASH擦除、读、写等状态的跳转。本文共设计有17个状态。其中,状态0为IDLE状态,状态1为工作模式判断状态,状态2-7完成块擦除操作,状态8-12为写状态,状态13为写块结束判断状态,状态14为写结束状态,状态15为读状态,状态16为读结束状态。

系统工作时,首先判断工作方式。当工作方式为写时,先对写操作对象扇区进行擦除处理,然后依次写入数据,每写一个数据后进行写块结束判断,如当前块已写完毕,状态跳转至下一待写扇区擦除状态,直至所有待写块均写完毕,状态跳转至IDLE状态。当工作方式为读时,直接对待读地址依次进行读取,每读一个数据后进行读结束判断,直至所有待读地址均读完毕,状态跳转至IDLE状态。

FLASH芯片在复位和命令操作出错后均返回读模式,只要输出使能信号OE#,片选信号CE#处于低电平,即可将地址总线上对应地址存储单元的数据送出。当按照规定的命令序列向FLASH存储器发出命令时,状态机自动地完成相应的操作。FLASH的状态位为RY/BY#引脚,在对FLASH操作过程中,如该引脚输出低电平表示FLASH处于忙状态,操作完成后变成高电平,表示FLASH回到空闲状态。

3 结束语

本文设计了基于FPGA的FLASH控制器,详细说明了利用同步有限状态机实现对FLASH存储器的读写控制方法,并通过modelsim时序仿真验证了该方法的正确性。该方法已成功应用于数字波束形成系统设计中,实践证明了该方法的正确性和可靠性。本文所介绍的设计方法普遍适用于FPGA对NOR FLASH存储器的读写控制。

参考文献

[1]夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2003.

[2]魏家明.Verilog编程艺术[M].北京:电子工业出版社,2014.

[3]Altera Corporation.Stratix IV Device Handbook[Z].Alteracrop Corporation,2006.

[4]Semiconductor.AM29LV065D Data Sheet [Z].AMD,2005.

[5]吴豫,孟宪元.FLASH编程器的FPGA实现[J].半导体技术,2003(05):48-51,69.

作者简介

刘俊(1985- )男,湖北省石首市人。硕士学位。现为南京电子技术研究所工程师。主要研究方向为雷达信号处理。

作者单位

南京电子技术研究所 江苏省南京市 210013