基于FPGA的64B/66B编解码设计与实现

摘 要

64B/66B编码是万兆以太网物理编码子层的重要组成部分,是IEEE推荐的10G通信的编码方式。文章主要研究64B/66B编码的编码准则以及一种基于查找表法的改进的编解码方法。该方法使用FPGA实现,实验结果与数据分析显示,该方案满足设计意图与协议的规定。

【关键词】64B/66B 万兆以太网 查找表 编解码 FPGA

与以往的传统以太网的介质独立接口类似,万兆以太网(XGMII)接口为l0GbE的MAC层和物理层之间提供了一种简单、低成本并易于实现的互联接口。XGMII接口由发送通道和接收通道组成,每个方向的数据传输是相互独立的,接口信号由数据、控制和时钟信号构成。XGMII接口具有支持l0Gbps的双向传输速率,成本低、容易实现的特点。64B/66B编码为XGMMII接口传输数据编码,编码准则来源于IEEE803.2ae,它并不是真正的编码,而是一种基于扰码机制的编解码方式,是IEEE推荐的10G通信标准编码方式。该编码具有系统开销较小,码字长,安全性高,传输快等优点。本文根据IEEE803.2ae中的编码准则,使用查找表法,运用Verilog语言完成了数字电路设计,使用Qurtus II软件完成模拟和数据分析。

如今使用硬件描述语言(Verilog 或 VHDL)所完成的电路设计,经过简单的综合与布局,快速的烧录至合适的FPGA 上进行测试,是现代 IC 设计验证的主流方法。开发人员可以根据自身的设计要求对FPGA编程,将编码烧录到 FPGA 芯片中即可实现数字系统的设计。得到所需要的数字电路。一个出厂后的成品 FPGA 的逻辑块和连接可以按照设计者而改变,所以 FPGA可以完成所需要的逻辑功能。

1 编解码的基本原理

1.1 概述

64b/66b编解码与万兆以太网的媒体独立接口XGMII(10 Gigabit Media Independent Interface)连接。其主要功能是:根据给出的不同的8个XGMII控制信号(XGMII_TXC[7:0]),把输入的64B的XGMII数据块或控制块XGMII_TXD[63:0]编码成66B码进行通信。其中,控制信号的每一位与64B码每8位对应,比如:XGMII_TXC[0]=0,则XGMII_TXD[7:0]为数据代码;XGMII_TXC[0]=1,则XGMII_TXD[7:0]为控制代码。64B/66B解码则是将66B码按照相反的规律解码成原先的64B XGMII数据块或控制块,并将原先的8个控制信号传送到XGMII接口。

1.2 IEEE802.3ae准则解读

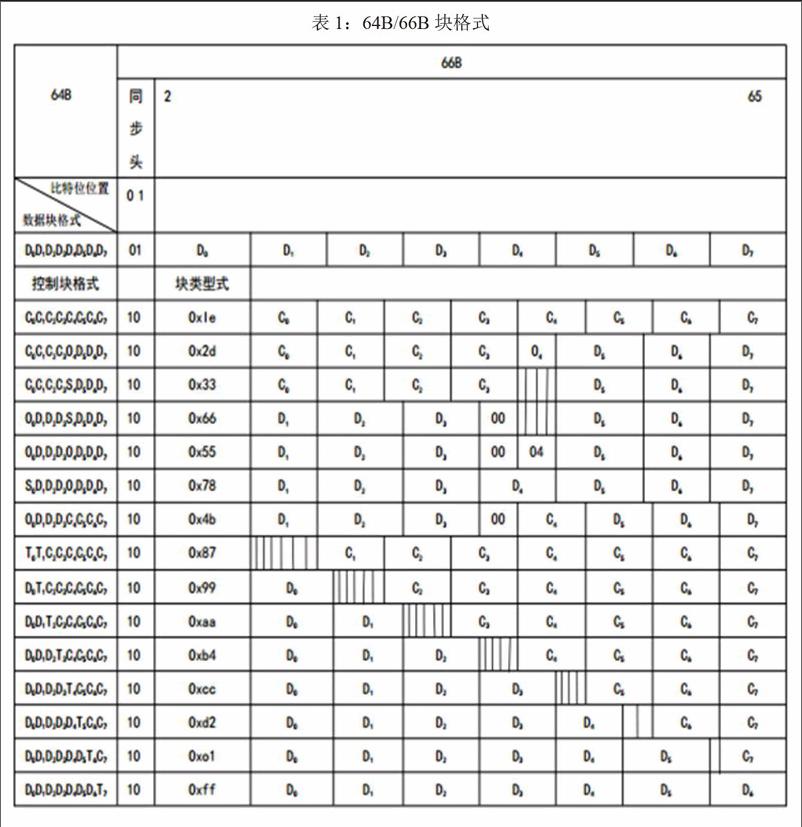

万兆以太网协议 IEEE 802.3ae 中规定了 64B/66B的编解码规则。具体规则如下:64B/66B码组的映射关系如表1所示。从中我们可以知道,64B码可以分为包含纯粹数据(8个8位的数据)的数据块(Data Block Format)和数据与控制代码按照一定顺序排列的控制块(Control Block Format)。根据不同的64B码格式,也有不同的编码规则,在生成66B码时就会有不同的同步头(sync)和块有效荷(Block Payload)。比如:输入的八位控制信号全部为0时,则表示输入的64B码为数据块格式,则同步头为01,块有效荷即输出相应数据。反之,当输入的八位控制信号不全为0,则表示输入的64B码为控制块格式,则同步头为10,块有效荷按如表1中规定格式生成。

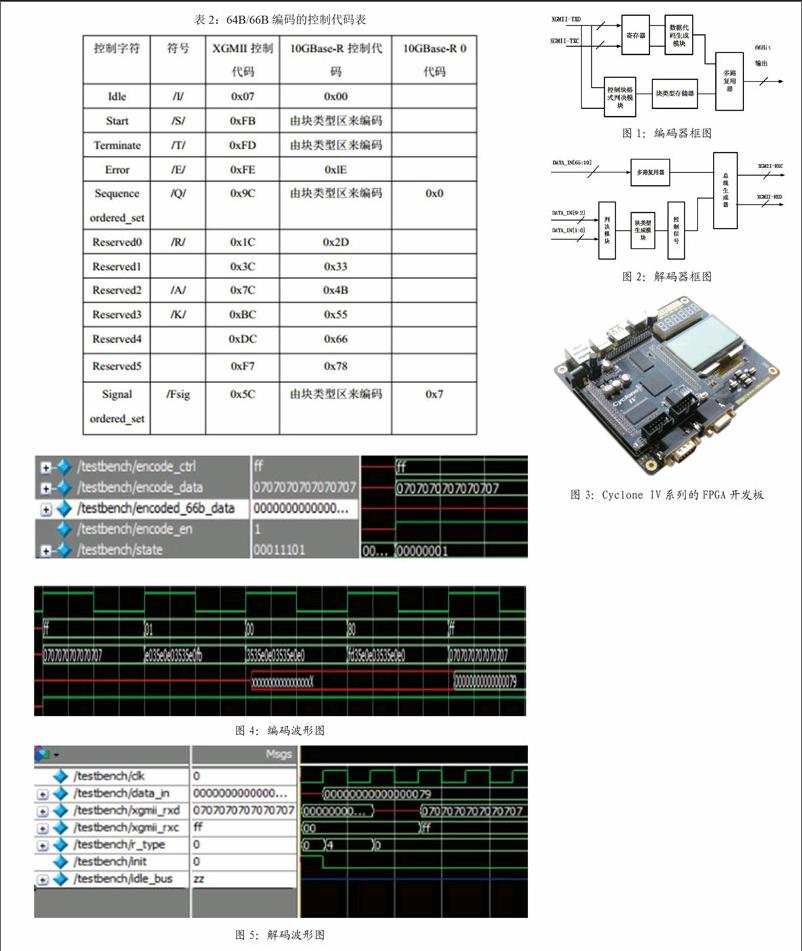

根据IEEE803.2ae的编码准则,控制块代码也具有相应的类型,这些控制块代码的类型如表2所示。表2将控制代码分为对应的几种形式:

(1)Idle表示空字符。(64B码中为16进制ox07,生成66B码时变为16进制ox00)

(2)start表示开始字符。

(3)Terminate表示结束字符。

(4)Error 表示错误,一般表示收到错误的数据。

(5)Sequence ordered_set系列号有序集。

(6)Reserved(0~5)保留字符0到5。

(7)Signal Order_set表示信号有序集。

所有的有效字符必须符合表2的要求,否则为无效或者非法字符。

1.3 编解码

64B/66B 编码过程:将输入的64B码分成8个1字节的码组,根据输入XGMII_TXC的每比特值判断这个码组是数据代码还是控制代码。如果XGMII_TXC 每个比特值都为0,则64B码为纯数据代码,直接在64B码组前加上同步头01就组成66B码组输出。如果XGMII_TXC 中有一个比特为1,则表示64B码组为控制块格式,先根据表2判断控制块中的每个控制代码是否有效,如果符合要求,则继续根据表1中的控制块格式来判断是否符合其中一种格式,如果格式符合则根据相应的控制块格式生成66B码组。在编码过程中,只要不符合表1或表2中的任何形式就认为是无效不符合要求,则不需进行编码。

解码则相对容易,与编码过程相反,首先根据66B码的同步头判断当前的数据是数据块还是控制块,如果是数据块则将除块头的64B数据赋予XGMII_TXD[63:0],再将XGMII_TXC[7:0]全部赋值0;如果是控制块,则根据块类型区的值确定控制块的格式,可以得到64B码每8位数据是数据代码还是控制代码,一方面得出XGMII_TXC[7:0],另一方面,运用查找表法,根据表1和表2相应的转换得出XGMII_TXD[63:0]。(表1中的空格表示一比特0,在64B控制块格式中C0—C7是8比特,在66B块效荷中为7 比特)。

2 編解码器设计

2.1 改进的编码器设计

根据对编码原理的研究,目前最常用的64b/66b编码方法是查找表法,这种方法虽然实现起来非常方便,但是使用过程中占用资源相对巨大,对于工程来说,单纯为了编解码占用较多的FPGA资源是不合理的,这在很大程度上限制了该方法的使用。鉴于此,本文采用了一种基于查找表法的新的编码方法。其基本思路是:先判断输入的XGMII_TXC是否符合控制块格式的要求并判断出同步头,如果不符合则直接输出Error并不需要对XGMII_TXD进行处理。再根据控制块将输入的XGMII_TXD分为8个通道,分别对每个8位数据进行处理,最后将数据输入多路复用器进行整合,输出符合要求的66Bit数据。其基本原理电路图如图1所示。编码器的组成为:输入数据寄存器,控制块格式判断模块,数据代码生成模块,块类型寄存器和多路复用器模块。

2.2 解码器设计

先分析66B码的同步头和块类型数据,得出接受的是数据块还是控制块,并可以确定是何种类型的控制块,生成判决信号输送到下一个模块(块类型生成模块),然后块类型生成模块根据表1和表2得出相应的64B控制块格式并根据判决信号得出XGMII_RXC的值。码子反转换模块根据XGMII_RXC判断XGMII_RXD每8个比特是控制代码还是数据代码并根据表2进行相应转换。最后利用数据生成器将这些数据或控制信号组成总线的形式输出。

3 仿真结果和数据分析

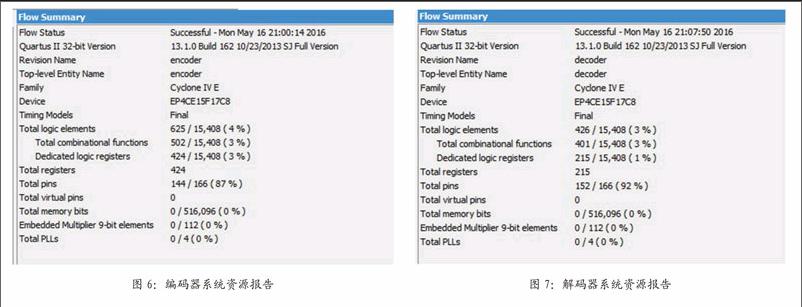

3.1 实验用FPGA开发板介绍

本文所使用的开发板如图3所示,该开发板的FPGA芯片是选用Cyclone IV系列的FPGA器件EP4CE15F17C8N,属于逻辑单元相对较少的FPGA芯片。CycloneIV系列器件集成了一个可选择的低成本收发器,在不影响性能的情况下,节省了功耗及成本。针对无线、有线、广播、工业,用户以及通信等行业中的低成本的小型應用,CycloneIV器件应该是最理想的选择。

3.2 实验结果

根据本文提出的新的64B/66B编解码方法,在Altera公司的Quartus II 软件平台上进行相关程序代码的编写,并选用Cyclone IV系列的FPGA器件EP4CE15F17C8N实现了编解码的功能验证,电路综合和波形仿真。编码器的仿真结果如图4所示, 从图中的仿真波形可以看出,DATA_OUT输出前先延时4个时钟周期,当输入xgmii_txc=0xff,xgmiix_txd=0x0707070707070707时,表示输入的控制块格式,参考表1,同步头为10,则可以得出data_out= 00000000000000079 。从图4可以得出结果是正确的。相反,解码器仿真结果如图5所示,解码器输出延时2个时钟周期,当输入数据data_in=00000000000000079时,解码得出结果xgmii_txc=0xff;xgmii_txd=0x0707070707070707,也与解码码准则相符合。

以上的仿真结果表明本文设计的编解码器可以正确的对输入的数据进行编解码,符合本文的设计意图。

本文所设计的编码器的FPGA资源占有率如图6所示,解码器的FPGA资源占有率如图7所示,从图中看出,资源的总体占有率很小,使用较少的逻辑单元(其中编码器:625/15408约占4%;解码器:426/15408 约占3%)便能完成工程设计,符合工程设计要求。

4 结论

64B/66B编码作为一种应用于以太网技术的编码方式,具有很多优点,其也为之后用于PCI-E,USB的128B/132B编码提供参考。本文的数字电路设计方法是基于查找表法的改进方法,在运用FPGA实现时,具有占用资源少,编码速度块等优点。此外,此方法使用的Verilog代码具有很好的可移植性,可以作为IP核植入到64B/66B编码的光纤电路中,特别适合FPGA设计,有很实用的工程价值。

参考文献

[1]温宇辰.嵌入式光纤万兆以太网系统设计[D].大连:大连理工大学通信与信息系统,2014.

[2]齐剑,胡春晖.高端路由器8口万兆子卡的硬件设计[J].电子设计工程,2015(07):178-181.

[3]朱云鹏.10G EPON协议分析仪中物理层的设计与实现[D].西安:电子科技大学光学工程,2015.

[4]周晴伦,王勇.万兆以太网中64B/66B编解码的硬件实现方法[J]:光通信技术,2006(02):21-23.

[5]王新.高速率传送网平台的物理层编码研究与实现[D].西安:电子科技大学通信与信息系统,2015.

[6]IEEE Std 802.3ae-2002[S/OL].New Jersey:IEEE,2002[2002-8-30].http://standards.ieee.org.

[7] The Automotive-Grade Device Handbook [EB/OL].2016-5-3.San Jose:http://www.altera.com.

[8]程博锋.基于FPGA及以太网技术的100G接口板设计[D].南京:南京理工大学电子与通信工程,2014.

作者简介

王向阳(1991-),男,安徽省庐江市人。合肥工业大学硕士生。主攻方向为数字集成电路设计。

作者单位

合肥工业大学电子科学与应用物理学院 安徽省合肥市 230009