基于SoC FPGA的MIPS处理器验证平台设计

张伟+梁蓓

摘 要 随着集成电路制程工艺的迅猛发展,数字集成电路复杂度越来越高,这对集成电路的验证带来了严峻挑战。相比软件仿真,数字芯片采用FPGA进行逻辑验证,可以大大提高验证的速度。近年来,SoCFPGA的出现对于验证平台的设计提供了一种新的启发。本文提出一种基于SoCFPGA的MIPS处理器验证平台的设计。采用ZYNQ芯片中的ARM主处理器实时控制监测MIPS从处理器的运行状态,来达到验证MIPS处理器的目的。同时ARM主处理器运行Linux操作系统,在不需要断电重新配置的情况下,通过执行不同的C程序实现不同功能的验证,大大提高了MIPS处理器的验证效率。

【关键词】验证 SoCFPGA MIPS ARM

1 引言

随着集成电路制程工艺水平的不断提高,在现代集成电路设计中,ASIC芯片的复杂程度与集成规模与日俱增,这为ASIC芯片的验证过程带来了严峻的挑战。芯片验证的目的是为了保证电路的逻辑功能与性能满足设计要求,其贯穿了整个芯片的设计过程。保证一次性流片成功,是芯片验证的最高目标,如果流片失败,不但会造成昂贵的流片费用损失,还会造成产品的推迟上市。整个芯片设计周期中,芯片验证已经占70%以上。这些因素都证明了芯片验证的极其重要性,实现高效且低成本的验证显得尤为重要。目前大多数模块的逻辑仿真主要采用加入工艺库的软件仿真,而系统级的芯片逻辑验证由于电路规模较大,软件仿真的速度与覆盖率已经不能满足设计周期要求。FPGA(Field-Programmable Gate Array),在ASIC芯片逻辑验证过程中是一种很有效的补充。由于FPGA的可重配置性,降低了流片失败可能带来的损失,加快了验证速度。

近年来,Xilinx推出了新一代嵌入ARM硬核的SoC FPGA—ZYNQ系列,相比传统FPGA中使用软核通用处理器性能提高很多,且不占用FPGA有限的逻辑资源和布局布线资源。本文利用ZYNQ芯片中嵌入ARM硬核的优势,提出了一种基于SoC FPGA的验证平台,通过使用ARM处理器做为主处理器,MIPS处理器作为从处理器,从而来对MIPS处理器设计过程进行验证。

2 ZYNQ简介

ZYNQ-7000是Xilinx推出的新一代全可编程片上系统(All Programmable SoC),其中我们采用的ZC706开发套件的ZYNQ芯片包含一颗可配置的双核ARM Cortex A9处理器(Processing System,PS部分),和基于28nm工艺的Xilinx FPGA(Programmable Logic,PL部分),我们将其称为SoC FPGA。其中PS部分可以用于通用型流水线计算,由于其已经集成在芯片上,不需要占用FPGA的逻辑资源和布局布线资源,而且性能很高。PL部分可以用于实现某些特殊算法的硬件加速与硬件扩展,PL部分可以实现并行计算,能够比通用处理器快6-8个数量级以上,而且PL部分的可重构性,能够灵活实现各种特殊算法的硬件加速。PS部分与PL部分通过芯片内AMBA总线实现连接,带宽很高,满足了某些苛刻环境下的带宽要求。

3 MIPS处理器验证平台设计

本文提出一种基于SoC FPGA(Xilinx ZYNQ)的MIPS处理器验证平台的设计。将PS部分的ARM处理器作为主处理器,MIPS处理器在PL部分实现,其中ARM處理器上移植Linux操作系统,配置交叉编译环境,在运行过程中ARM处理器实时监控MIPS处理器的工作状态,以此达到验证MIPS处理器功能的目的。

3.1 基于SoC FPGA的原型系统验证架构

基于SoC FPGA的原型系统验证架构如图1,整体架构的设计思想如下:

(1)首先上电后MIPS处理器处于复位状态。ARM主处理器通过AXI-Lite接口,将MIPS处理器运行过程中所需要的指令和初始化数据,从系统内存写入到Distributed RAM中。

(2)写入完成后,ARM主处理器通过AXI-Lite接口,写入MIPS处理器启动命令,结束MIPS 处理器的复位状态。MIPS处理器开始从Distributed RAM中读取指令和数据。

(3)MIPS处理器执行指令过程中,ARM主处理器将轮询MIPS处理器的结束标志。MIPS处理器完成所有指令执行后,将设置结束标志(Distributed RAM的固定地址)。

(4)ARM处理器将计算结果从Distributed RAM中读回到系统内存,并打印到串口终端,从而能够在屏幕上实时监测MIPS处理器运行状态。

3.2 AXI-Lite总线接口模块设计

ARM主处理器发出的指令能够在AXI-Lite Slave接口完成译码,根据ARM发出的读写请求对Distributed RAM进行操作。要求其能够支持以下地址空间的寻址:AXI-Lite接口可寻址的范围为0x00000000 – 0x00003FFF (16KB),其中包括8KB Distributed RAM空间,地址范围为:0x00000000 – 0x00001FFF,并且在AXI-Lite接口模块中加入一个1-bit寄存器,来实现启动MIPS处理器的功能,地址为0x00002000。该寄存器将作为AXI-Lite接口的输出信号,在正常复位后,该寄存器置为1。当AXI-Lite接口收到对这个寄存器的写命令时,就将写入值(32-bit)的第0位取反后写到这个1-bit寄存器中,来实现对MIPS处理器的复位操作。

AXI-Lite Slave接口可寻址范围为16KB,所以其地址宽度为14位,与ARM通过AXI总线连接,与Distributed RAM通过5个通道连接,分别是Address、Write_data、Read_data、MemWrite、MemRead。另外一位寄存器mips_reset输出口与MIPS处理器的复位端相连。Distributed RAM空间大小为8KB,即2^13Byte,单个寄存器为32位(4Byte),需要2^11个寄存器,所以Distributed RAM地址为11位。Distributed RAM采用同步写入异步读取。

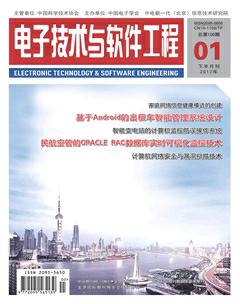

为了对AXI-Lite Slave模块与Distributed RAM模块进行仿真验证,需要设计一个AXI-Lite Master模块模拟ARM处理器对其进行收发数据,以对其逻辑功能进行验证,对这两个模块进行仿真的结构如图2所示。

AXI-Lite Master模块代替ARM处理器进行收发数据,加入时钟复位激励,得到如图3的仿真结果。

3.3 MIPS处理器顶层设计

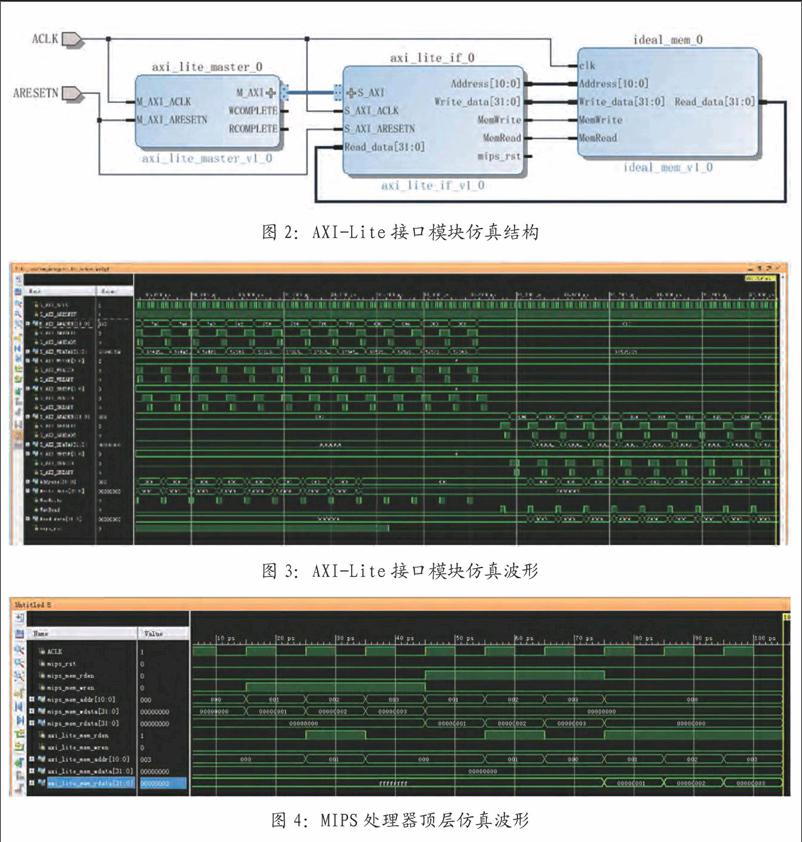

mips_cpu_top需要将MIPS处理器模块、AXI-Lite Slave模块、Distributed RAM模块包含进来,另外需要添加一段组合逻辑,实现当MIPS处理器对Distributed RAM进行读写操作时,如果此时ARM通过AXI-Lite Slave模块对Distributed RAM有读请求,将数据32hFFFF_FFFF返回到ARM读取的数据,表示ARM读取的数据错误。只有当MIPS处理器停止对Distributed RAM进行读写操作时,ARM处理器才能读取到正确的数据。如图4是对顶层的仿真结果。

根据仿真波形可以看到,当MIPS处理器对Distributed RAM进行写操作时,同时ARM主处理器对Distributed RAM进行读操作,读到的数据为32hFFFF_FFFF。当MIPS处理器进行读操作时,ARM主处理器同样读到错误的数据。只有当MIPS主处理器对Distributed RAM没有任何操作时,ARM主处理器才会读取到正确的数据。顶层逻辑功能得到验证。

4 基于SoC FPGA的MIPS处理器验证平台实现

4.1 比特流文件的生成

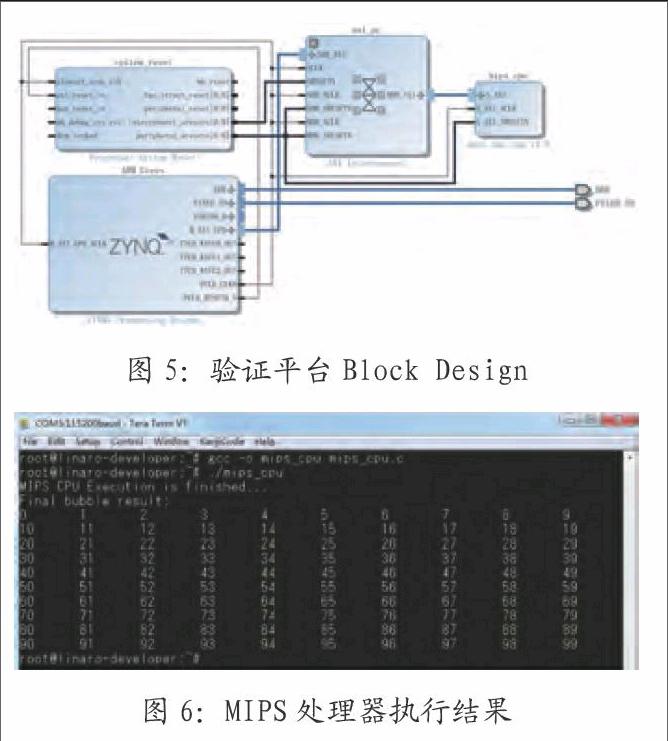

验证平台具体的Block Design如图5,MIPS处理器顶层包含了AXI接口模块,Distributed RAM模块以及MIPS处理器,对外只预留AXI总线结构,系统会自动为工程加入AXI Interconnect模块与Processer System Reset模块,经过DRC检查,添加时钟约束,Vivado软件生成可以配置SoC FPGA的比特流文件。

4.2 ARM硬核上运行Linux操作系统

在ARM硬核上运行Linux操作系统需要用到以下几个文件:

(1)BOOT.bin是引导程序,其组成包含3个文件:fsbl.elf、system.bit、u-boot.elf。主要用于初始化PL(FPGA部分)和PS(ARM部分)及引导内核。fsbl.elf需要在SDK软件中生成,system.bit为Vivado工程的比特流文件,u-boot.elf需要在Linux系统下编译生成。使用SDK软件可以将这3个文件生成BOOT.bin。

(2)uImage是Linux内核文件,需要在Linux操作系统下安装交叉编译环境后,编译生成。

(3)devicetree.dtb是设备树文件,包含硬件配置信息的数据结构,包括CPU、内存、总线及相关外设,内核启动时,可以解析这些信息,以此来配置内核及加载相关驱动。

(4)Linaro文件系统。需要在Linux系统下解压到SD卡的ext3分区。ramdisk文件系统,需要存放于SD卡的fat32分区。

有了以上文件后,我们就可以在ARM硬核上移植Linux操作系统。

4.3 编译运行C程序

将比特流文件烧写到SoC FPGA中,启动操作系统,C程序在Linux操作系统下编译并且执行,ARM执行该C程序的主要功能是将MIPS处理器所需的指令和数据写入Distributed RAM中,并启动MIPS处理器,MIPS处理器将从Distributed RAM中读取指令及数据,其执行后的结果存放于Distributed RAM中,将由ARM在Distributed RAM中读回到系统内存中,并在串口调试工具界面中打印输出。

由图6打印输出的结果可以判断,在SoC FPGA上實现了多周期MIPS处理器的验证,ARM处理器将MIPS处理器执行冒泡排序结果打印。后期可以编写不同的C程序,让MIPS处理器执行其他更加复杂的功能,对MIPS处理器进行更充分的验证。

5 结语

本文提出了一种基于SoC FPGA的MIPS处理器验证平台的设计,对MIPS处理器的验证提供了硬件仿真,提高了仿真速度。同时采用ARM主处理器实时控制监测MIPS从处理器的方式,可以更加直观的监测MIPS处理器的运行状态,并且ARM主处理器运行Linux操作系统,能够在不断电的前提下,通过执行不同的程序,来对MIPS处理器进行验证,同时在验证过程中采用C程序,极大的提高了验证效率。

参考文献

[1]Qinsheng M,Yang C,Jun Y,et al. Random testing for system-level functional verification of system-on-chip[J].系统工程与电子技术(英文版),2009,20(06):1378-1383.

[2]Murphy P,Frantz J P,Welsh E,et al.VALID:Custom ASIC Verification and FPGA Education Platform[C]// International Conference on Microelectronics Systems Education. IEEE Computer Society,2003:64-65.

[3]Devins R J.Processor-independent system-on-chip verification for embedded processor systems[J].South BurlingtonvtUssouthBurlingtonvtUsessexJunctionvt Us,2003.

[4]Hutton M,Yuan R,Schleicher J,et al.A Methodology for FPGA to Structured-ASIC Synthesis and Verification[C]// Design,Automation and Test in Europe.IEEE,2006:64-69.

[5]Crockett L H.The Zynqbook:embedded processing with the ARM Cortex-A9 on the Xilinx Zynq-7000 all programmable SoC[M].Strathclyde Academic Media,2014.

[6]Wu Y,Song J,Ren K,et al.Research on LogGP Based Parallel Computing Model for CPU/GPU Cluster[J].2017.

作者简介

张伟(1991-),男,在读研究生,主要研究方向为继承电路设计。

梁蓓(1963-),女,贵州大学教授,硕士生导师,主要研究方向为集成电路设计。

作者单位

贵州大学大数据与信息工程学院 贵州省贵阳市 550025