CIC抽取滤波器的MATLAB设计及FPGA实现

杨翠娥

(太原工业学院,山西 太原 030008)

CIC抽取滤波器的MATLAB设计及FPGA实现

杨翠娥

(太原工业学院,山西 太原 030008)

CIC抽取滤波器是无线通信中的常用模块,一般用于数字下变频(DDC)系统中。它可以在降低采样速率的同时,完成低通滤波的作用。本论文介绍了CIC抽取滤波器的工作原理,并给出了CIC滤波器的MATLAB程序及仿真结果。最后,利用FPGA高速、高稳定性的特点,在QUARTUS设计环境下进行了CIC滤波器的HDL模块设计。

CIC;抽取;MATLAB;FPGA

随着数字通信技术的发展,信号传输的速度越来越快。这就对数字信号处理提出了更高的要求。多速率信号处理技术可以在一个数字信号处理系统中采用多个不同的采样率,同时可以实现不同采样率之间的相互转换。这种技术在降低高速数字系统的复杂度,减少存储量及提高灵活性等方面具有较好的性能。数字信号的速率可以通过内插和抽取来改变,其中,内插用于上变频系统中,抽取用于下变频系统中。无论抽取还是内插,都需要设计一个满足抽取或内插(抗混叠)要求的数字滤波器。该滤波器性能的好坏将影响取样速率变换的效果以及实时处理的能力。为此,积分级联梳状(CIC)滤波器得到了广泛的应用。本文将以单级CIC抽取滤波器的设计为例进行CIC抽取滤波器的MATLAB分析设计及FPGA的实现。

1 CIC抽取滤波器的工作原理

积分级联梳状(CIC)抽取滤波器即实现对输入信号采样率的抽取和低通滤波,以完成信号的降速处理。在数字下变频系统中得到了广泛应用。CIC抽取滤波器包括积分和梳状两个基本组成部分。如图1所示。

图1 CIC抽取滤波器

以单级CIC抽取系统为例,取级数N=1。积分器实际上是单极点的FIR滤波器,反馈系数为1时的状态方程如下:

y(n)=y(n-1)+x(n) .

(1)

根据z变换,积分器的传输函数可以表示为:

(2)

梳状器也是一个对称FIR滤波器,其状态方程可以表示为:

y(n)=x(n)+x(n-DM) .

(3)

式中,D为设计参数,称为微分延迟,其传输函数为:

HC(z)=1-z-DM.

(4)

则单级CIC滤波器的传递函数为:

(5)

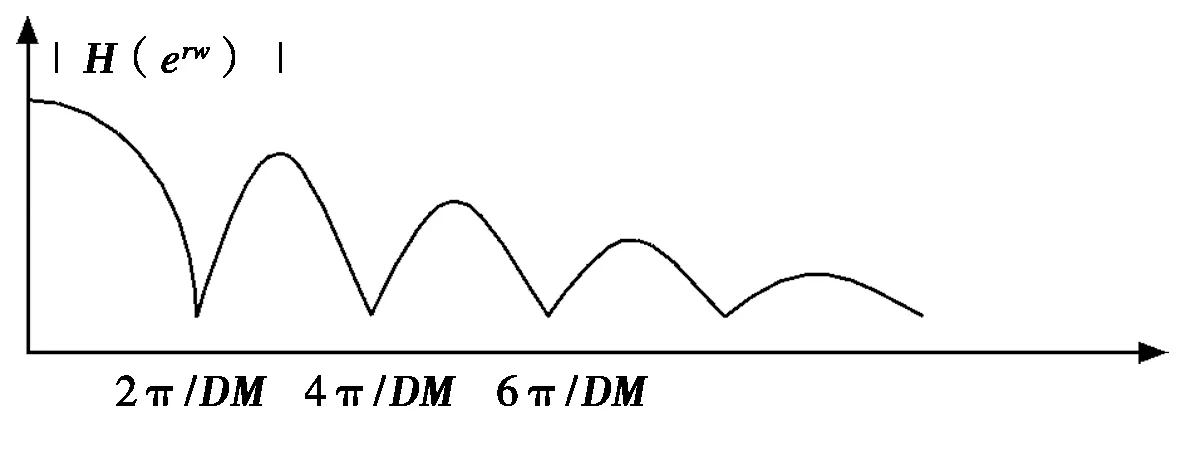

其传递函数的幅频特性为:

(6)

如图2所示为单级CIC滤波器的幅频特性。由图可见,频率越高,旁瓣电平越小。可以证明,当DM足够大时,第1旁瓣的电平与主瓣电平的差值约为13 dB左右。单级CIC滤波器旁瓣电平较大,阻带衰减较差。为此,可以采用多级CIC滤波器级联的办法来降低旁瓣电平,提高阻带衰减的速度,在此不再论述。

图2 CIC滤波器的幅频特性

2 CIC抽取滤波器的MATLAB设计

MATLAB工具中包含了许多不同功能的函数包,其中包括CIC滤波器的函数包,通过调用可以方便地完成CIC滤波器的设计。下面给出的是抽取率为2的CIC抽取滤波器的MATLAB程序:

r=2;

hm=mfilt.cicdecim(r);

fs=44.1e3;

n=0∶10239;

x=sin(2*pi*1e3/fs*n);

y_fi=filter(hm,x);

x=double(x);

y=double(y_fi);

y=y/max(abs(y));

stem(n(1∶44)/fs,x(2∶45)); hold on;

stem(n(1∶22)/(fs/r),y(3∶24),′r′,′filled′);

xlabel(′时间(sec)′); ylabel(′信号值′)

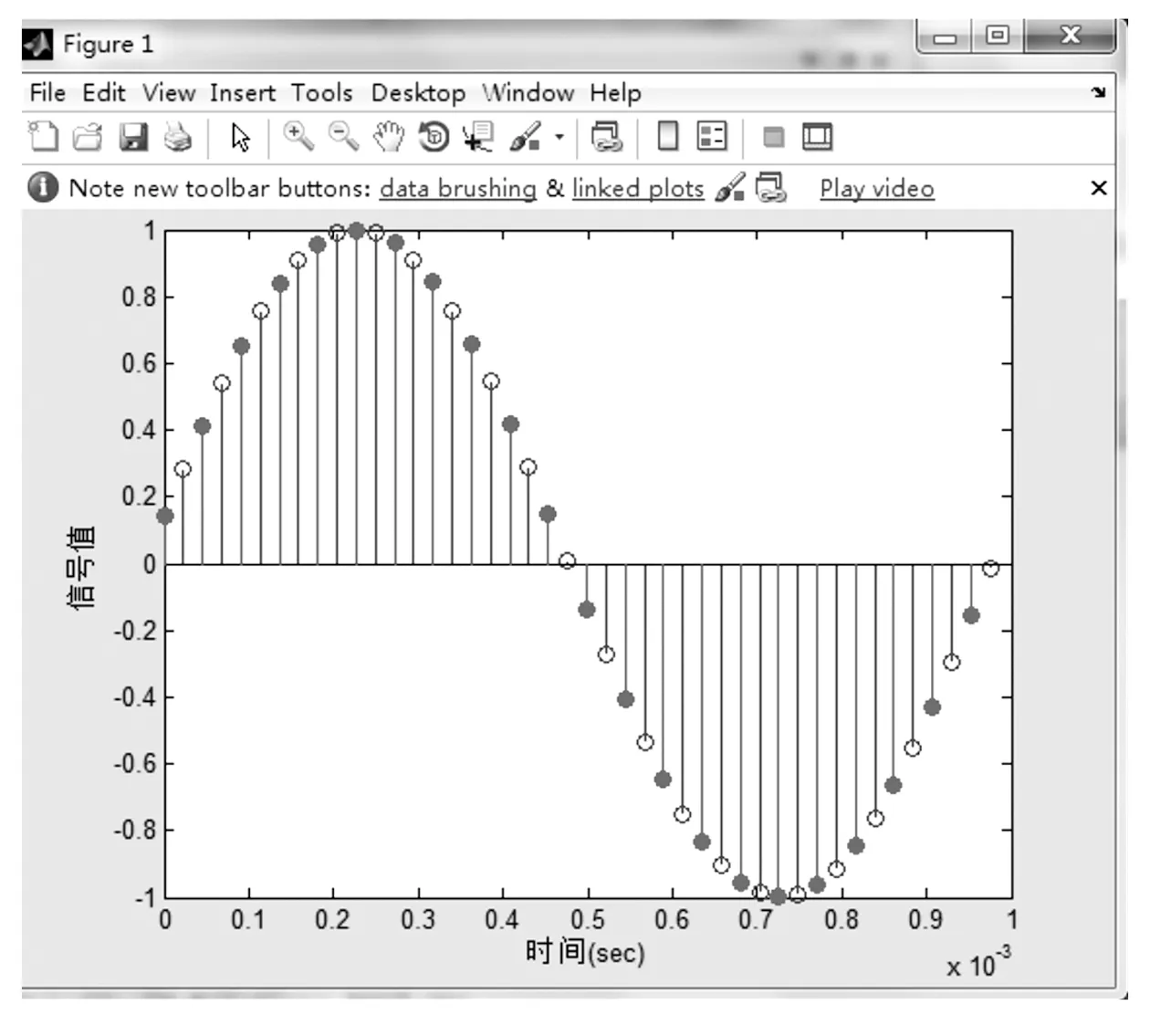

上述程序经过运行得到如图3所示的MATLAB仿真结果。结果表明,信号经过CIC抽取滤波器后,其输出信号和输入信号的奇数位完全对应上,完成了抽取滤波的功能。

图3 CIC抽取滤波器的MATLAB仿真结果

3 CIC抽取滤波器的FPGA实现

FPGA芯片具有高速、高稳定性及可编程的特点,非常适合用于高速数字通信系统的设计。在Quartus II设计环境下,用Verilog语言实现一个单级、抽取率为2的8位CIC抽取滤波器,系统工作时钟的频率和数据速率相等。关键程序如下:

always@(posedge clk1) begin

if (!reset) begin

x_t <= 0; int_out <= 0;

end

else begin

x_t <= {x_t[7∶0], x};

int_out <= x_t[7∶0] + x_t[15∶8];

end

end

always@(posedge clk) begin

if(!reset) begin

y_t <= 0;

temp <= 0;

end

else begin

if (clk1 == 1)

temp <= 0;

else

temp <= int_out;

y_t <= {y_t[7∶0], temp};

end

end

assign y = y_t[7∶0] - y_t[15∶8];

endmodule

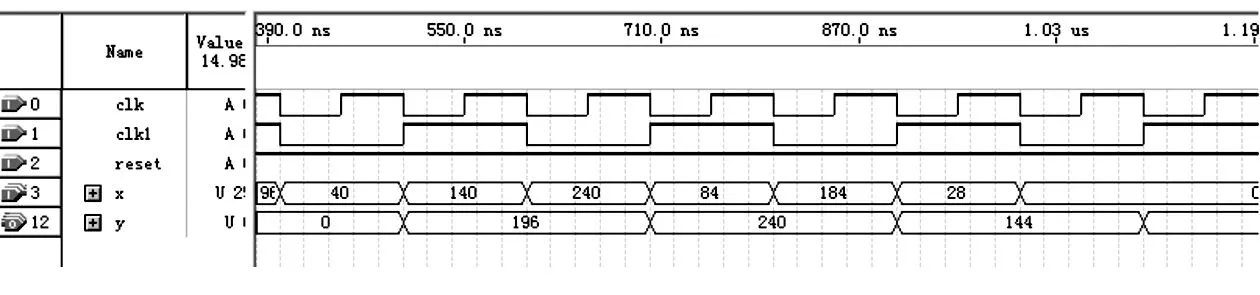

在Quartus II设计环境下,对程序进行编译和仿真,得到了如图4所示仿真结果,可以看出,经过CIC抽取滤波器后,输出信号速率减半且实现了低通滤波的功能。

图4 单级CIC抽取滤波器的局部仿真示意图

[1] 刘福奇,刘波.Verilog HDL应用程序设计实例精讲[M].北京:电子工业出版社,2009:189-205.

[2] Harris FJ.Multirate Signal Processing for Communication Systems[M].NJ:Prentice Hall 2005.

[3] SanjitKMitra.数字信号处理:基于计算机的方法[M].第2版.北京:电子工业出版社,2005.

CIC Extraction Filter Design Based on MATLAB and the FPGA Implementation

Yang Cuie

(TaiyuanInstituteofTechnology,TaiyuanShanxi030008,China)

CIC extraction filter is commonly used as wireless communication module, generally used in digital down converter (DDC) system. It can finish the function of low pass filter when reducing the lower sampling rate at the same time. This paper introduces the working principle of CIC extraction filter, and gives the CIC filter MATLAB and the simulation results. Finally, the characteristics of FPGA high speed, high stability is used to make the HDL module design of CIC filter under the environment of QUARTUS.

CIC; extraction; MATLAB;FPGA

2016-12-06

杨翠娥(1964- ),女,山西太原人,副教授,研究方向:射频电路设计及FPGA开发与应用。

1674- 4578(2017)01- 0046- 03

TN911.4

A