航天高可靠FPGA测试技术研究

周 珊,杨雅雯,王金波

(中国科学院 空间应用工程与技术中心,北京 100094)

航天高可靠FPGA测试技术研究

周 珊,杨雅雯,王金波

(中国科学院 空间应用工程与技术中心,北京 100094)

FPGA由于强实时性,在航天等高可靠系统中应用非常广泛,从最初的接口时序控制到现在代替大部分CPU足以证明它的影响力。它的测试方法既独立于传统CPU测试,又有别于芯片的测试。基于航天高可靠FPGA系统的重要性,对FPGA系统测试的需求尤为迫切。结合软件测试方法和FPGA产品自身特点,研究了FPGA测试需求抽取方法及特有的测试要求,分析了静态测试(跨时钟域分析、代码规则检查,静态时序分析)、动态仿真测试(前仿真,布局布线后仿真,三模冗余仿真验证)、物理测试(芯片级物理测试、目标板级物理测试、最小系统板级物理测试)三大类测试方法的测试机理及适用范围,形成了一套实用的FPGA测试技术。目前该FPGA测试技术已成功应用于多个航天高可靠FPGA产品的测试中,发现了很多引起功能失效的重大问题,并对其中常见的问题给予归类总结。

FPGA测试技术;测试需求分析;静态测试;动态仿真测试;物理测试

0 引 言

FPGA是在可编程器件的基础上进一步发展的产物。作为专用集成电路领域中的一种半定制电路,既克服了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点,使用非常灵活。由于灵活性高,涉及周期短,成本低,风险小,功耗低等优势,FPGA成为电子设计领域中最具活力和发展前途的一项技术,在通信、数据处理、网络、仪器、工业控制、军事和航空航天等领域得到了广泛应用。

随着FPGA的广泛应用,其可靠性变得越来越突出,尤其在航空航天领域,越来越多的基于FPGA的应用系统在运行过程中发生一些异常状况,导致下行到地面的数据出错或者单次任务失败。如果在地面测试过程中,针对各种正常异常的测试场景以及功能路径时序路径进行全面覆盖,则会大大减少错误或风险的发生。目前对于FPGA的验证技术在业界还没有统一标准,所以有必要研究一套切实可行且经过大量工程检验的测试方法。

1 现 状

FPGA产品与其他嵌入式软件产品相比具备以下特点:

(1)需要从代码编码风格,时钟与复位设计的方法,代码可综合性规则等方面检查编码的规范性。

(2)需要分析异步信号是否有合理的同步处理方式以及跨时钟域信号如果出现亚稳态现象后是否有合理的保护机制。

(3)需要从三种工况下分析所有时序路径的建立保持时间是否满足要求,输入输出接口的时序是否满足上级接口以及下级接口的要求。

(4)FPGA的并行运算和高响应速度的特性,使其在对高速时序逻辑的处理中得到广泛应用。因此对FPGA系统功能、性能的测试中,不能仅仅局限于对稳态输入输出的验证,还需要验证系统对时序信号的响应及输出量随时间变化正确性的判断。因此在测试用例的设计中,需要对系统输入、输出的时间变化趋势进行规定,并提供动态输出信号的判断准则,同时需要开发时序测试环境支持测试用例的执行。

现有的FPGA系统测试方法主要是FPGA系统的验证者在开发完成代码后,对其进行功能仿真后保证行为级无误后,就下载到选定的FPGA器件利用黑盒的测试方法来直接验证设计功能的正确性。该方法是将测试对象看成一个黑盒子,无需了解系统内部的工作原理,利用周边测试环境产生测试激励,施加于实际被测件上,根据采集到的被测件响应判读其是否正常工作[1-2]。这种测试方法的特点是简单、快捷且对测试人员要求不高。缺点是测试的完备依赖于测试集的完备,由于FPGA系统的复杂性,单靠黑盒分析的方法很难覆盖全所有的功能路径和时序路径,从而导致问题漏测,无法防范风险。该方法主要依托如下两种测试系统:

(1)基于自主研制的测试系统。

自主研制的测试系统一般由上位机软件、通信线缆、控制电路以及待测FPGA组成。上位机软件完成配置数据和测试向量的生成,配置数据和测试向量通过通信线缆发送给控制电路。控制电路接收配置数据和测试向量完成FPGA的测试,并将测试响应通过通信线缆返回给上位机软件,最后由上位机软件完成测试结果的对比分析。这种测试系统控制灵活且有针对性,但往往研发投入大、测试时间长、测试精度难以保证。而且由于只针对特定的测试需要,可移植性差,不具通用性,因此目前主要用于研究及验证。

(2)基于自动测试设备(Automatic Test Equipment,ATE)的测试系统。

使用ATE平台研发的测试系统则由ATE来完成自主研制测试系统中上位机软件和控制电路的功能。这种测试系统只需要ATE和待测FPGA即可完成。ATE可以一次完成待测FPGA的多次“配置+测试”,从而减少人工操作,提高了FPGA的测试效率,便于实现FPGA的制造测试。但是,利用ATE完成待测FPGA的配置时,需要反复修改FPGA配置数据,以生成ATE可识别并执行的测试向量格式的数据[3]。当配置数据较多时,需要占用ATE内部大量的存储资源。而使用设备商提供的子卡来扩展ATE的存储深度将是一笔巨大的开销。

以上两种测试系统都有较大缺陷,文中根据多年的FPGA测试验证经验,研究了一套高可靠FPGA测试技术,每种测试技术都针对FPGA的某种特性,并将这一技术应用于多个型号任务的FPGA测试中,发现了很多能引起功能失效的重大问题。

2 高可靠FPGA测试技术

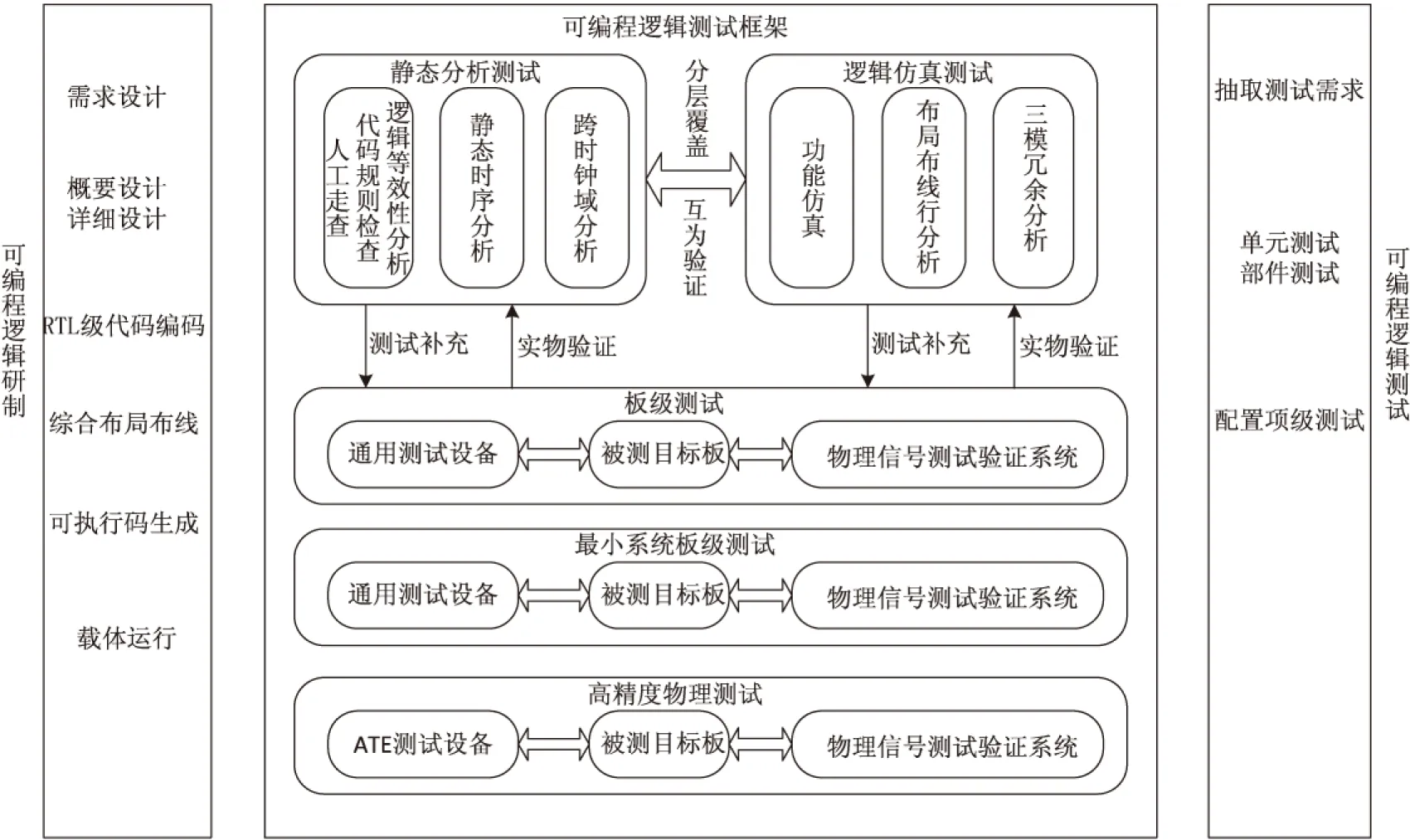

FPGA设计是一种“硬”的软件设计,与目标载体为CPU的软件研制和测试一样,具有自顶到下的研制流程和测试流程。FPGA的研制流程自顶向下分为需求描述、概要设计、详细设计、HDL语言编码、综合布局布线、目标码生成,相应的自顶向下的测试流程分为测试需求提取、单元和部件测试、配置项级测试,如图1所示。

测试方法分为静态测试和动态测试。静态测试主要包括静态时序分析、跨时钟域分析、形式化验证等,它是对代码或者网表的静态分析,不涉及功能层面的测试。动态测试是对代码具体功能的测试,主要包括动态仿真、目标板级测试、最小系统板级测试、芯片级测试等,它是在测试需求分析,测试用例设计的基础上对整个代码进行各种正常异常的场景测试和时序测试[4]。以下针对重点部分做详细说明。

2.1 测试需求的抽取

测试需求是基于原始需求、概要设计以及详细设计抽取,对于FPGA的测试需求提取主要考虑从业务层面、协议层面、信号层面抽取。

业务层:基于功能路径关注于功能处理的IPO(输入、处理过程、输出),在功能路径覆盖的各个条件分支中按照等价类、边界值、判定表等分析方法抽取了功能需求、接口需求、边界需求、性能需求、余量需求、安全性需求等。

协议层:主要是针对具体传输协议(如SPI协议、422协议等),可以考虑从协议的有效无效方面进行测试需求的抽取。如422传输协议可以从起始位、停止位、校验位的有效无效,波特率在范围内和范围外以及某位传输时波特率异常正常等方面考虑设计测试用例。

图1 FPGA配置项级测试流程

信号层:信号层是FPGA测试独有的测试层面,硬件描述语言在芯片载体上实际映射为带有延迟信息的各种基本单元的组合,所以信号层上时序的偏差会使时序路径出错,从而引起功能路径上需求的不满足。在信号层面抽取测试需求时要关注如下方面:

(1)输入接口的时序在协议范围内偏斜时是否满足建立保持时间要求;

(2)输出接口的时序是否满足下级单元时序要求的范围;

(3)主时钟,输入接口时序,输出接口时序是否满足20%余量要求;

(4)三种工况下,同步时序路径是否满足建立保持时间要求。

2.2 静态分析测试

静态分析是一种静态的扫描,不涉及具体功能路径的分析。在FPGA测试中,静态分析能对代码和网表的分析覆盖达到100%,是全路径的一种分析扫描,在测试具体功能之前需先做静态分析来发现代码架构是否会引起严重的时序问题,以及代码与需求、概要设计、详细设计是否存在严重的不一致等需要做大规模修改的问题。静态分析主要包括以下四种:

(1)代码规则检查。

对代码的编码规范性、时钟与复位设计规则、代码风格及可综合性等内容进行审查,从设计规则上保证了代码在综合和布局布线后不会由于编码规范的问题引起不可预期的错误风险。

(2)静态时序分析。

静态时序分析是对布局布线后的网表做全时序路径的分析,旨在分析同步路径的建立保持时间,恢复移除时间以及输入接口和输出接口的时序是否满足要求。如果出现简单的时序问题可通过增加延时单元,在长的组合路径中间加寄存器的方式来调整;如果出现严重的时序问题则需对代码的架构做重新设计[5-6]。

(3)跨时钟域分析。

跨时钟域分析是对时序路径中的异步时序路径做分析,分析异步路径是否使用了合理的同步机制作处理,从而降低亚稳态出现的概率。如果不及时处理这类问题,就会使得系统在实际运行过程中由于单粒子翻转或其他空间环境影响时出现错误,严重时可引起单次任务失败。

(4)等效性检查。

等效性检查是采用逻辑锥的思想,测试源码和布局布线后的网表是否一致,如果出现不一致则可能出现后仿真或者物理测试时功能不满足要求,而前仿真时功能满足要求的情况。等效性检查出现不一致的地方一般是由于代码的编码方式不规范,导致编译器在对其综合时优化了一些信号的组合方式。针对不一致的地方要做详细分析,进而判断是否会引起功能错误。

2.3 逻辑仿真测试

仿真测试是对代码和网表的动态功能和时序路径的覆盖,通过在代码或网表的输入接口模拟各种正常异常的测试激励来测试被测件的功能表现是否正常。仿真主要分为行为级仿真和网表级仿真两种,每种仿真使用的场景如下:

行为级仿真[7-8]:

(1)单元级测试、部件级测试以及配置项级测试等功能行为级别测试。

(2)对于功能故障定位,内部信号分析时使用。

(3)收集代码的语句、分支、表达式、条件、状态机等覆盖率时使用。

(4)跨时钟域分析时用做动态激发亚稳态信号后查看是否引起功能错误时的分析。

网表级仿真:

(1)网表级的仿真主要针对三种工况下(低压、高温;正常电压、常温;高压、低温),验证带时序信息的网表功能表现是否正常。

(2)后仿真和静态时序分析是一种相互补充的测试方式,静态时序分析是分析所有时序路径是否存在建立保持时间等时序不满足的情况,而后仿真是分析经过综合布局布线优化后带时序信息的网表是否满足功能要求[9]。

2.4 物理测试

目前FPGA器件行为测试的主要方法是通过寄存器传输级仿真进行功能测试,通过布局布线后仿真完成时序测试。仿真测试并不能真实反映FPGA器件在实际物理工况下的某些运行特性,比如器件电压特性、电平转换特性、交联器件实际延迟信息、板级连线延迟信息等,所以仿真测试覆盖的测试环境相对比较理想。其次仿真结果很大程度上依赖于FPGA厂商提供的器件模型,由于国外FPGA器件厂商对国内有诸多限制,特别是应用与航空航天领域的器件,目前已经发现厂商提供的器件模型在某些工况下已不能正确反映器件工作特性的情况,所以必须使用物理测试的方法对FPGA进行进一步测试[10-11]。

物理测试方法主要分为最小系统板级测试、芯片级测试和目标板级测试三种,以下将详细说明。

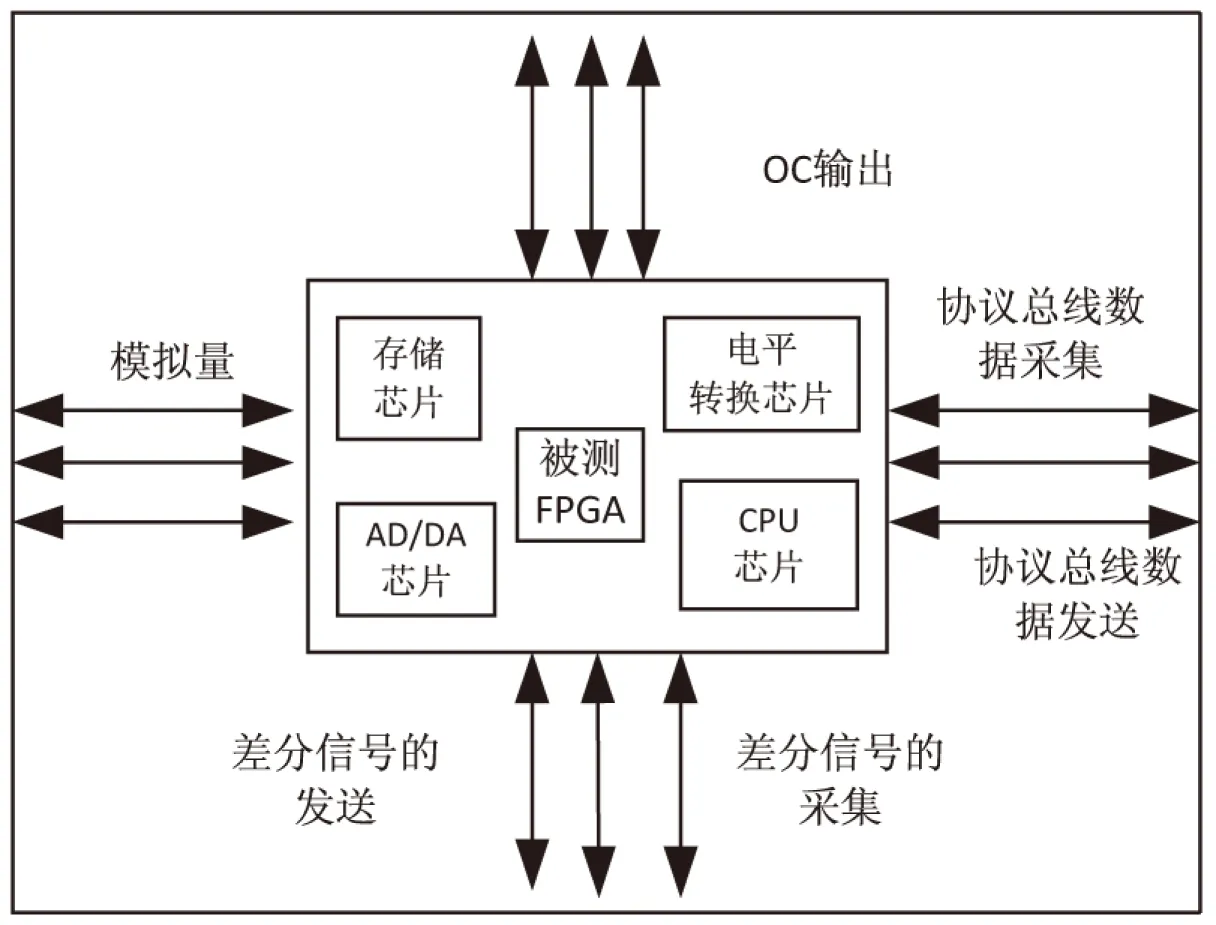

2.4.1 最小系统板

最小系统板级的测试方式适用于被测目标与胶连设备耦合程度高,无法解耦的情况,如被测目标板上有嵌入式CPU芯片和FPGA芯片共存的情况。测试时如果直接对目标板进行测试,则会出现发生问题时,无法对具有强耦合关系的两种器件进行故障诊断,从而引入误判的风险,所以需采取最小系统板的方式,原理如图2所示。

图2 最小系统板的测试原理图

最小系统板设计时考虑使被测FPGA正常工作的最小子集,用户管脚需直接延伸至最小系统板的接插件,与板外的测试系统直接相连,最小系统板的测试方式具有下述优点:

(1)测试激励可以直接施加到芯片管脚,被测件故障诊断时可以直接定位到输入输出接口,归避了目标板非被测芯片功能错误引起的故障。

(2)对所有输入输出接口做到了全接口的直接覆盖测试,接口路径的覆盖率达到百分之百。

(3)可以模拟板级芯片如E2PROM、NANDFLASH等存储芯片的各种正常异常状态,如某一存储区域数据错误或出现坏块的现象,从而对被测件的健壮性、可靠性得到进一步验证。

2.4.2 芯片级测试

芯片级测试采用了基于ATE的测试技术,精度可达到500 ps,可以应用在对被测FPGA接口信号的物理特性进行测试以及精确地对被测件接口做时序测试的情况,具体说明如下:

第一方面模拟真实运行环境下被测FPGA管脚的电压、电流等发生变化时其功能是否正确,包括以下测试[12-13]:

(1)测试电源管脚上电顺序的变化是否影响其功能,如芯片所需的3.3 V,1.8 V,2.5 V电源信号加电顺序的变化;

(2)测试电源管脚上电时间间隔的变化是否影响其功能;

(3)测试电源管脚上电时间的变化是否影响其功能,如3.3 V电压缓慢加电、快速加电等;

(4)测试输入管脚信号电压幅度的变化是否影响其功能,如LVTTL的高电平在加减20%的幅度变化;

(5)测试输入管脚信号电压变化时间的快慢是否影响其功能,如LVTTL高电平在变为低电平时时间快慢的调节等。

第二方面克服普通测试设备精度不高以及仿真测试方式得到的时序指标不够真实的弊端,利用ATE设备高精度特性,从信号层面模拟接口时序,对被测FPGA进行接口测试,并给出了被测件接口余量和强度具体指标(精度达到500 ps)。

测试原理如图3所示。

测试设备分为母板、子板和控制显示设备。子板上承载被测FPGA芯片,母板负责把FPGA芯片的接口信号引线和控制端采用等长屏蔽双绞线的方式相连,控制端负责发送测试激励,采集输出响应并做比对。

具体测试方法为:首先通过仿真工具模拟典型工作模式下的测试激励,并把此激励输出到门级网表上得到期望输出波形;将输入输出波形文件转换成ATE可以识别的文件形式,加载到测试控制端;母板把测试控制端的控制信号转换成测试激励电信号通过屏蔽双绞线传递到子板上的被测FPGA管脚;被测FPGA产生的响应信号通过母板传递到监显端,监显端把收到的数据与期望的数据进行对比,最终输出判读结果。

2.4.3 目标板级的物理测试

目标板级的物理测试是对FPGA器件实际运行目标板的测试,器件运行在实际的载体板上可以真实地反映周交联器件的电气特性,适用于功能测试、性能测试、强度测试、安全性测试等,尤其适用于仿真耗时较长的测试用例。具有下述特点:

(1)可以覆盖大部分的测试用例,执行周期较仿真时间大大缩短;

(2)被测件存在于实际的目标板载体,周边的信号特性和实际状态最接近。

原理如图4所示。

3 应用实例

基于上述总结的四大类FPGA测试技术,应用于航天高可靠型号任务FPGA测试中,共测试了16个项目,发现了如下几类常见问题:

图4 目标板级物理测试原理图

(1)静态时序分析方法发现了内部时序路径或接口时序路径不满足要求的问题引发的功能错误;

(2)跨时钟测试方法发现了跨时钟域信号未做同步或者同步机制不正确引发的功能偶发错误;

(3)代码规则检查和等效性检查发现一些重要信号由于编码方式不合理从而在后续综合布局布线时被优化,引发功能错误;

(4)目标板测试的方法发现了大部分功能、边界、性能、安全性等错误,并用前仿真的方法分析定位出了错误的机理;

(5)芯片级的测试方法测试出了芯片接口物理特性发生变化时引发的功能错误,并给出了输入输出接口的时序指标;

(6)最小系统板的测试方法测试出了板级芯片正常异常模拟式下引发功能失效的问题。

4 结束语

针对航天高可靠FPGA的测试技术进行深入剖析,提炼出了一套切实可行的测试方法,阐明了FPGA的测试分析对象,从静态分析、动态仿真、物理测试三个角度提炼了三大类九小类测试方法,并给出了每种方法的测试机理,适用场景,以及每种方法测出的典型问题。将这套测试技术成功应用于多个航天高可靠软件的测试中,对其中常见的时序问题给予归类总结,这套技术可以作为高可靠FPGA测试技术的一个参考标准。

[1] 刘子宜,刘 畅,郑 军.基于软件测试技术的FPGA测试研究[J].电子技术应用,2011,37(5):28-30.

[2] 丰玉田,付宇卓,赵 峰.大规模SOC设计中的高效FPGA验证技术的研究与实现[J].电子技术应用,2006,32(2):110-114.

[3] 龙祖利,王子云.FPGA测试技术及ATE实现[J].计算机工程与应用,2011,47(6):65-67.

[4] Rajsuman R.System-on-a-chip:design and test[M].Beijing:Beihang University Press,2003.

[5] 鲍 瑞.芯片测试平台中的FPGA时序分析及芯片接口测试方法研究[D].广州:华南理工大学,2013.

[6] 周海斌.静态时序分析在高速FPGA设计中的应用[J].电子工程师,2005,31(11):41-44.

[7] Bertolino A.Software testing research:achievements,challenges,dreams[C]//Future of software engineering.Minneapolis:[s.n.],2007:85-103.

[8] 李相雨.基于LUT的FPGA时序分析及后仿真实现[D].西安:西安电子科技大学,2009.

[9] 吕欣欣,刘淑芬.基于SynopsysVMM方法的FPGA验证技术[J].计算机应用,2009,29(9):2527-2529.

[10] 赵 娟,王月玲,刘明峰,等.基于SRAM配置技术的FPGA测试方法研究[J].半导体技术,2007,32(9):804-808.

[11] 孟令军,李 娜.基于FPGA的内部逻辑在线测试技术研究[J].电测与仪表,2008,45(11):34-37.

[12] 薛 宏,赵 欣.FPGA测试技术研究[J].微处理机,2008,29(2):11-14.

[13] Amendola A M,Benso A,Corno F,et al.Fault behavior observation of a microprocessor system through a VHDL simulation-based fault injection experiment[C]//Proceedings of the conference on European design automation.Geneva:[s.n.],1996:536-541.

Research on High Reliable FPGA Test Technology on Spaceflight

ZHOU Shan,YANG Ya-wen,WANG Jin-bo

(Technology and Engineering Center for Space Utilization,Chinese Academy of Sciences,Beijing 100094,China)

Due to characteristic of the strong real-time,FPGA is widely applied in the high-reliability region.It is used from the control or the interface timing to substituting most of CPU which proves its importance.The testing method of FPGA is different from the AISC’s testing and the conventional CPU’s testing.As the significance of high reliable FPGA on spaceflight,the demand for testing an FPGA system is particularly urgent.Combined with the software testing methods and FPGA’s characteristics,the FPGA testing request abstract method and specific test requirements are researched,analysis of the test principle and application range of three main types of static testing (the analysis of crossing-clock region,code rule checking,static timing analysis),dynamic simulation testing (front simulation,back-end simulation,three-mode verbose verification) and physical testing (chip’s physical testing,goal-board’s physical testing,the smallest system’s physical testing),providing a set of practical FPGA testing technology.At present,the set of testing technology is applied successfully on the test of several high reliable FPGAs on spaceflight,and many significant functional disabled problems have been found,where the common ones are classified and summarized.

FPGA test technology;test requirement analysis;static test;dynamic simulation test;physical test

2015-07-21

2015-11-11

时间:2017-02-17

国家重大专项(Y214010RN)

周 珊(1983-),女,硕士,工程师,研究方向为高可靠软件、嵌入式软件测试;王金波,博士,副研究员,研究方向为高可靠软件。

http://www.cnki.net/kcms/detail/61.1450.TP.20170217.1623.002.html

TP391.9

A

1673-629X(2017)03-0001-05

10.3969/j.issn.1673-629X.2017.03.001