三值光学处理器的MSD数据正/负值判断器设计与实现

张宏烈 周 健 张素兰 刘艳菊 王先超

1(齐齐哈尔大学计算机与控制工程学院 黑龙江齐齐哈尔 161006) 2(上海大学计算机工程与科学学院 上海 200072)3(阜阳师范学院数学与统计学院 安徽阜阳 236041)

三值光学处理器的MSD数据正/负值判断器设计与实现

张宏烈1周 健1张素兰2刘艳菊1王先超3

1(齐齐哈尔大学计算机与控制工程学院 黑龙江齐齐哈尔 161006)2(上海大学计算机工程与科学学院 上海 200072)3(阜阳师范学院数学与统计学院 安徽阜阳 236041)

(15845673377@163.com)

数值正/负或零判断器是计算机比较数据大小的必备器件,随着三值光学处理器中采用三态光信号表示信息的MSD(modified signed-digit)数并行加法器的出现,研究三态光信号所表达数值的正/负或零值判断器成为完善三值光学处理器的重要一环.根据MSD数的特点,通过对三态光信号的变化规律与MSD数据的对应关系的研究,提出了从一组三态光信号来判断其表达的多位MSD数据正/负特性或零值的方法.将这一方法用于2个不定长MSD数据的差运算结果,实现了判别2个MSD数据的大小或相等.依据上述理论,建立了以偏振片、液晶和半反半透镜为主要器件构造的MSD数据判断器结构,加以FPGA作为控制电路,实现了光电混合模式的3位MSD数据判断器.通过实验证明了该判断器的有效性,进而证明了其基本理论的正确性和结构设计的可行性.

三值光学处理器;MSD数据正/负值判断方法;判断器结构设计;判断器硬件设计

计算机应用需求的多元化和电子计算机硬件优化接近极限促进了人们对新型计算机研究的兴趣.在这个背景下,量子计算机、生物计算机、超导计算机和光学计算机都有了长足的进步.借助于液晶器件的成熟性,三值光学计算机后来居上,仅仅16年就从一个思想火花发展成最有特色的一种可用的新型计算机之一.它以数据位数众多、数据总线可以任意分组使用和各个数据位的计算功能可以根据用户的需要而重构,为我们提供了计算能力强大的新工具[1].然而,这种计算机目前还没有控制程序转移的能力,这严重阻碍了它在智能计算方面的应用,造成这一缺陷的根本原因在于三值光学计算机还没有零值判断器和正/负值判断器,进而不能判断2个数值的大小或2个逻辑量是否相同.近年来,作者对这一紧迫问题进行了研究,在理论和技术2方面取得了成功,其成果将赋予三值光学计算机进行智能计算的基本硬件,将其巨大的数据并行计算能力引入智能计算领域,形成功能强大的新型智能计算工具.

1 研究背景与相关工作

三值光学计算机的原理和结构最早由上海大学金翊教授于2002年在其博士论文研究期间首先提出[2],其基本原理是:采用光的3个稳定的状态(水平偏振光、垂直偏振光和无光)来表示三值信息,且利用液晶的旋光性和偏振片的滤光性完成这3个稳定光状态的转换,进而实现二维并行光学运算.

三值光学计算机的研究历经16年,已经相继提出三值光学计算机数据位管理理论和技术[3]、可重构性理论[4]、降值设计理论和技术[5]、多处理器共享双空间存储器技术[6]、内存空间推移技术[7]等学术成果,并且构建了相应的硬件结构和编写了软件系统.在2014年,上海大学三值光学计算机团队建成了面向应用研究的整机实验系统——上大11(SD11);2016年又推出第1台稳定运行的三值光学计算机——上大16(SD16),该系统以众多数据位可重构的三值光学处理器为核心硬件,包含三值光学解码器和编码器[8-10]、MSD(modified signed-digit)加法器[11-13]、MSD数乘法器和除法器[14-15]等功能组件.2017年3月18日该团队又取得了决定性成果,完成三值光学计算机——SD16的36位并行加法器运算,标志着三值光学可重构处理器理论和技术已经成熟,从此有了一种比电子计算机更优秀的、工作原理不相同的计算机核心部件.

为了在数据位很多的加法运算中克服进位过程带来的延时问题,三值光学计算机采用了无进位操作的MSD数二进制并行加法器.这种加法器的所有数据位并行计算,因此加法计算的时间与数据位数无关,突破了电子计算机加法器随位数增加而无法并行完成加法的瓶颈,特别适合三值光学处理器利用众多的数据位来计算大值数据.MSD加法器也决定了三值光学计算机内部的数值计算过程都必须采用MSD二进制数,而不是电子计算机采用的常规二进制数.因此,本文给出的数值判断器件也都采用MSD二进制数和三值逻辑量.

本文给出的0值和正负数判断器也采用光的3个稳定的状态(偏振方向正交的2个偏振光态和无光)来表示三值信息、采用液晶阵列和偏振片构造光状态变换器、采用MSD数进行数值计算,因此,在信息表达与基本元器件方面都与三值光学处理器相同,保证了它们可以作为支撑智能计算的核心硬件,直接并入三值光学计算机的硬件系统.

2 MSD计数制

常规计数法则中,N进制有n个计数符号,分别表示值0到n-1,且逢n进一,如果规定n进制的每一位有n+r个计数符号(n,r为正整数),且仍然逢n进一,则每一位可以表示n+r-1个值,称为冗余计数.显然,在冗余计数中一个数值可能有几个表示形式,这对人类使用很不方便,但在多值计算机中,却有它的方便之处.在三值光学计算机中,采用n=2,r=1的冗余计数法,在这一类冗余计数法中,使用上最便利的一种计数法当属MSD计数法.

MSD数字系统是一种带符号位的三值二进制数,早在1961年由Avizienis首次提出[16],并在1986年由Draker等人首次将其应用到光学计算机中[17].对于任意的实数N,其MSD表示形式如下:

(1)

(2)

而数值-9的表示形式为

(3)

对比上面2个数可以发现MSD数具有3个特点:

1) MSD数不需要符号位.在MSD数表示中,对一个数的表示式按位取反就得到其相反数,这个特点具有一般性.

2) MSD数无需补码和反码.正数和负数用同一表达式.

3) MSD数具有冗余性.在进行加减运算时可以不进行进位或借位.

所以MSD数值的正负性取决于最高位非零值的正负,最高位为1,该数为正数;最高位为-1,该数为负数;只有所有位均为零,该数才为零.

3 MSD数据正/负特性判断原理

三值光学计算机处理数据的过程中,经常会关心运算结果的正/负性,例如2个MSD数据做减法运算后,运算结果的正/负性就很重要,因为可以根据运算结果的符号,能够进一步确定这2个数孰大孰小,完成2个数大小的比较.又例如在除法操作之前,对除数必须进行零值判断,只有非零的除数才能进行除法操作.理论和实验已经证明,MSD数据在进行加减乘除运算后结果还是一个MSD数据,所以需要从MSD数据表示形式分析入手[7-9].

三值光学计算机是将光强和光的偏振性结合起来表示三值信息的光电混合结构.三值光学计算机采用的MSD数计数体系中,用u(即-1)代表水平偏振光h,用1代表垂直偏振光v,用0代表无光态w.MSD数的符号u可以表达负数,故MSD数不需要增设符号位,相应地也就没有补码和反码,其数值的正/负性取决于最高非零值位的正负,最高非零位为1则该数为正数,最高非零位为-1则该数为负数,只有所有位均为零则该数才为零.根据MSD数的特点,可以得出任意一个MSD数的正/负值判断的逻辑表,进而推导正/负值判断方法.

例如,有3位MSD数X=A3A2A1,其中A3,A2和A1分别表示从高到低X各个位上的数值,用Y表示数X的正负性,且X为正数时Y=1,X为负数时Y=u,X为零值时Y=0,可以得到3位MSD数正负性判断的逻辑表,如表1所示:

Table 1 The Logic Table of the Positive/Negative to Determine for 3-bit MSD Data

MSD数在三值光学计算机中有明确的光信号表达方式,若用光的3种状态对表1内容进行替换,就会得到3位并行三态光数据的所有可能组合状态,以及每个组合对应的最高位光状态,如表2所示.显然,N位三态光信号的最高位的光状态表达着该数据的正/负性,因此,表2列出了3位MSD数据的正/负或零值与3位光信号的组合之间的对应关系.如果将MSD数据正/负或零值作为判断结果,将三态光状态组合作为判断依据,根据表2反映出的判断结果与输入光状态之间存在的关系,可以很容易地找出MSD数据的正/负值或零值判断的规律,这就是MSD数据判断器设计的理论依据.

Table 2 The Logic Table of the Positive/Negative to Determine for 3-bit Tri-State Optical Data

4 判断器设计方案

本文所要设计的判断器,其功能是判断具有三值多位并行的MSD数据为正数还是负数或者为零值.从判断器的任务出发,实际上可以分别设计零值判断器、正值判断器和负值判断器来完成判断器的每项功能.

4.1 零值判断器

分析表2中的数据可以发现,MSD数据取值为零,只有一种情况.因此若进行零值判断,只需要选择一个处理基元,其基元表如表3所示:

Table 3 Zero Value Judgment Processing Unit 1表3 零值判断处理基元之一

按照降值设计理论,可定义输入为无光态时,输出为垂直偏振光态V,否则输出为无光状态,则其基元表变为表4的形式.

Table 4 Zero Value Judgment Processing Unit 2表4 零值判断处理基元之二

从表4所列出的逻辑关系,可以提出一个合适的硬件设计方案来判断MSD数据是否为零值,其光路结构原理如图1所示:

Fig. 1 The principle diagram of optical path structure of zero value discriminator图1 零值判断器光路结构原理图

图1为3个数据位的零值判断光路结构,当需要判断的数据位数达到n位时,其光路结构如图2所示,其原理与图1所示结构的原理相同.

Fig. 2 The principle diagram of optical path structure of n -bit zero value discriminator图2 n位零值判断器光路结构原理图

图2的结构虽然也可以实现零值判断,但是考虑到目前的三值光学处理器的数据位数已达上千位,当判断的数据位数增加时,对应的偏振片和液晶的叠加数量也会相应增加.例如,当待判定的数据位数达到300位时,则需要同样数量的液晶和同样数量的垂直偏振片同时叠放在一条直线上,其厚度可能已达到30 cm甚至更多.由于其尺寸已明显占用了太多的空间,不便于实现,需要进行拆分,如对n位零值判断器结构经过2拆分后,得到了如图3所示的光路结构.

Fig. 3 The principle diagram of optical path structure of 2-way split图3 2拆分后光路结构原理图

图3中的m1和m2为迭合器,由半反半透镜和全反射镜组成.经过n/2次细分后,就得到了类似于运算器的排列,其相应的处理基元的光学结构如图4所示:

Fig. 4 The principle diagram of the structure of n -bit zero value discriminator图4 n位零值判断器结构原理图

上述零值判断器的结构均为有光源结构.如果提供光源困难,还可对该结构进行简化去掉光源,设计一种无光源结构.由于三值光学运算器输出的每个数据位共有4个液晶像素位,且2个像素位为水平偏振光路,2个像素位为垂直偏振光路,将每个数据位的水平偏振光的光路合并为一路,垂直偏振光的光路合并为一路,如图5所示:

Fig. 5 The principle diagram of the structure of 3-bit zero value discriminator for no light source图5 3位零值判断器无光源结构原理图

4.2 正值判断器

分析表2的数据可以发现,在3位MSD数据的所有组合中,数据最高位为垂直偏振光V,即数据为正数的情况,共有13种组合,如表5所示.从表5列出的正值判断的逻辑关系,可以提出一个硬件设计方案以实现对MSD数据是否为正数的判断,其光路结构原理如图6所示.

Table 5 The Logic Table of the Positive Value to Determine for 3-bit MSD Data

Fig. 6 The principle diagram of the structure of the positive value discriminator图6 正值判断器结构原理图

Table 6 The Table of Working Principle for the Positive Value Discriminator

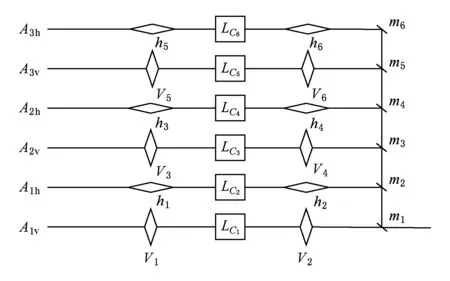

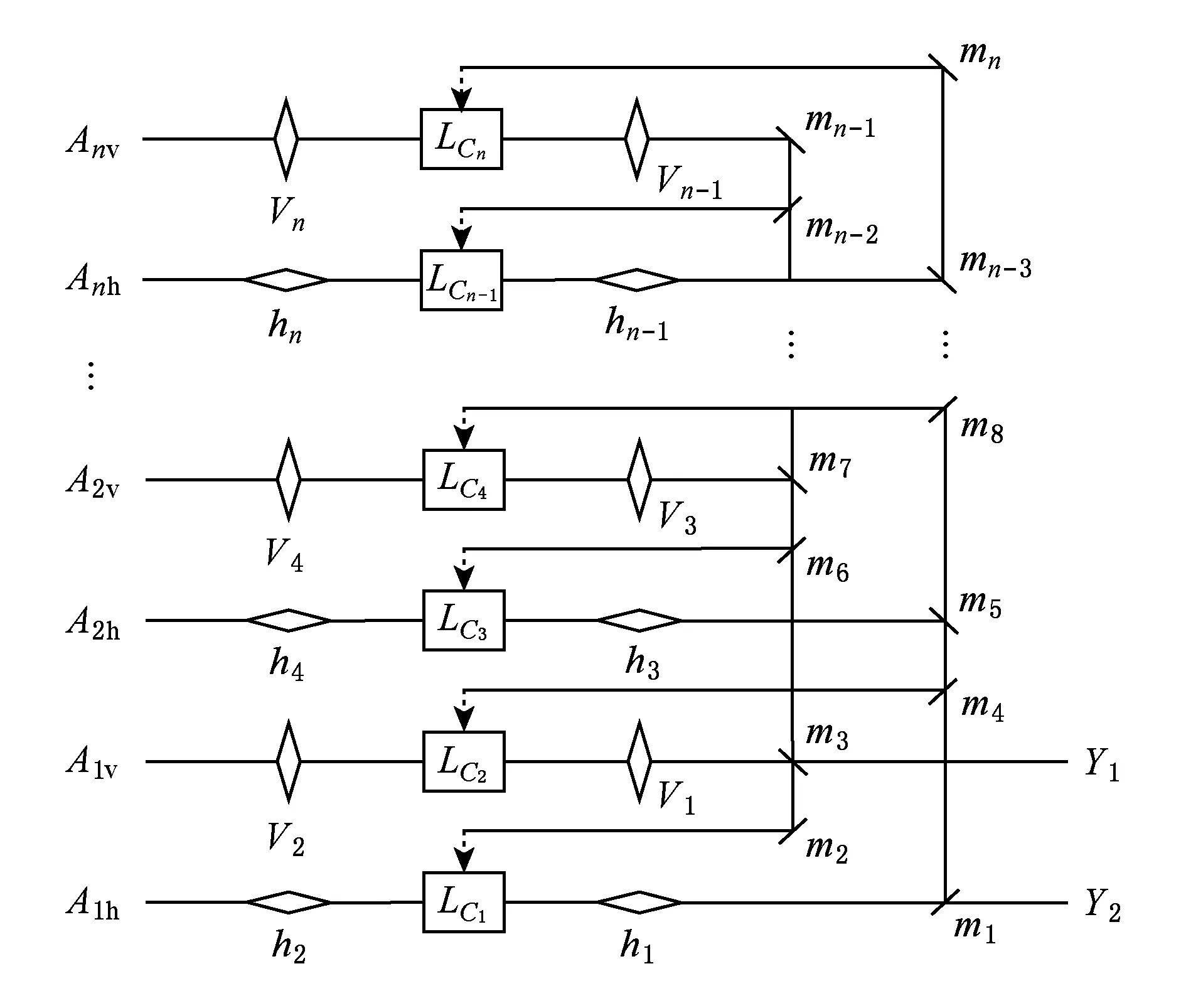

图6所示的3位MSD数据正值判断器结构也易于扩展到n位MSD数据的情形,只要将输入端和输出端均扩展到n位即可.其原理图如图7所示:

Fig. 7 The structure of the positive value discriminator for n -bit MSD data图7 n位MSD数据的正值判断器结构

4.3 负值判断器

分析表2的数据可以发现,在3位MSD数据的所有组合中,数据最高位为水平偏振光h,即MSD数据为负数的情况,同样共有13种组合,如表7所示.

从表7列出的负值判断的逻辑关系,可以提出一个硬件设计方案以实现对MSD数据是否为负数的判断,其光路结构原理如图8所示.

Table 7 The Logic Table of the Negative Value to Determine for 3-bit MSD Data

Fig. 8 The principle diagram of the structure of the negative value discriminator图8 负值判断器结构原理图

Fig. 9 The principle diagram of the structure of the n -bit negative value discriminator图9 n位负值判断器结构原理图

可见,负值判断器结构与正值判断器结构非常相似,只是将水平偏振片和垂直偏振片的位置互换了一下.在负值判断器结构中,当较高位有垂直偏振光输入时,将使更低位的所有液晶旋光,低位的输出均为无光态.此时,若更高位有水平偏振光输入时,能使Y2输出亦为水平偏振光,那么输入的数值X为负值.若更高位没有光信号输入,则Y2输出为无光态,那么输入的数值X为非负数.该结构能够实现对数据是否为负数作出判断,称为负值判断器.图8所示的3位负值判断器结构也易于扩展到n位数的情形,其n位负值判断器的结构如图9所示.

4.4 MSD数据判断器

事实上,在应用中为了判断MSD数据的正/负性或零值,而分别设计3个判断器是很不经济的办法,只有设计一个判断器解决所有问题才是有效可行的.为此对于4.1~4.3节提出的3个判断器的设计方案进行综合,设计具有判断MSD数据正/负性或零值等全部功能的判断器,称之为MSD数据判断器.

4.1~4.3节设计的判断器中,正值判断器只能判断输入端的MSD数据最高位是否为正数(垂直偏振光),但不能确定某一非正数究竟是零值/负数(无光态/水平偏振光);负值判断器只能判断输入端的MSD数据最高位是否为负数(水平偏振光),但不能确定某一非负数究竟是零值/正数(无光态/垂直偏振光).考察图7所示的正值判断器结构和图9所示的负值判断器结构,它们均只能判断一种确定的光状态的特点,若将水平偏振光和垂直偏振光通路都连接到相应的输出端,同时保持相应数据位之间的控制关系,那么改进后的判断器结构就可以根据输入情况,输出对应的水平偏振光或垂直偏振光2种光状态,即可以判断数据的正值或负值2种情况,如图10所示:

Fig. 10 The principle diagram of the structure of MSD data discriminator图10 MSD数据判断器结构原理图

图10所示的判断器具有2个输出端Y1和Y2,Y1和Y2的组合逻辑如表8所示.在某一时刻,Y1和Y2只要有一个为有光态,那么MSD数据判断器就可以判断出输入光数据的正负性,即Y1有光输入则MSD数据为正值,Y2有光输入则MSD数据为负值.但是Y1和Y2还有2个组合状态,可以推断出Y1和Y2若都为无光态,则输入MSD数据肯定为零值,所以图10判断器是一个能够判断MSD数据是否为正数/负数和零值等所有功能的判断器,符合MSD数据判断的功能要求.

Table 8 The Combinational Logic Table of Y1 and Y2表8 Y1和Y2组合逻辑表

若A3,A2均无光信号输入而A1有光信号输入时,其光信号能直接到达相应的输出端,输入为水平偏振光时,Y2输出为有光态,输入的数值X为负数;输入为垂直偏振光时,Y1输出为有光态,输入的数值X为正数.

仅当Y1和Y2均无光信号输出时,输入的数值X才为零值.

所以图10所示的判断器结构就是一个典型的MSD数据判断器,分析其工作原理,可以归纳出MSD数据判断器具有3个显著特点:

1) 自动识别符号位能力

图10所设计的MSD数据判断器具有自动识别N位光输入信号最高符号位的能力.这个能力是由MSD数据判断器自身结构决定的,对于N位光信号输入端,其输入数据的有效位数在0~N-1之间,具有不同位数的数据,其最高位也是不固定的,根据图10判断器结构可以容易分析出,无论输入光信号具有多少位、光数据的最高位处在输入端的哪一位,判断器的输出光态信息保证与输入光信号最高位的光态一致.这就为处理MSD数据时省略了寻找数据最高位位置环节,加快三值光学处理器的处理数据的速度.

2) 自动屏蔽低位数据能力

在判断MSD数据最高位符号时,除最高位之外,需要考虑其他低位数据对判断结果的影响.图10所设计的MSD数据判断器,通过自身结构,很好地化解了这个问题.判断器设计中,最高位数据的输出结果直接影响低位的液晶显示器的旋光性,控制低位输入端侧的光信号,只允许输出与最高位数据一致的信息,屏蔽不一致的信息.因此MSD数据判断器具有自动屏蔽低位数据的能力.

3) 硬件结构可扩展性

该电路具有简单方便的可扩展性.因为三值光学处理器数据位众多,可以达到成千上万位,对于数以千位的MSD数据判断器结构的设计并不困难,只需对判断的位数进行扩展,最高位的判断方法原理没有变化.图10所示的3位判断器结构扩展到n位数的情形,如图11所示.

但是,针对图11中的n位判断器结构,在硬件设计中也存在一个明显问题,由于采用的液晶层数将会很多,这势必会带来光强的衰减问题.1)在不含半反半透镜情况下,由于折射反射等原因,光通过液晶(包括透过其他任何非理想介质)肯定会有衰减,所以透过一层液晶和2层偏振片当然也就会有衰减,如果液晶和偏振片层数巨大,势必会使光强衰减非常严重,以至于感光器件能否探测到有光.2)在含半反半透镜情况下,半反半透镜每次将光的一半反射、一半透过,如果一束光经过n个半反半透镜,那么光强就只剩下原来的12n,这个光强也不一定能被感光器件探测到.所以图11中的n位判断器结构研究方案,理论上是可行的,在真正设计时还要考虑光强的衰减问题,通过增加其他硬件提高光的传输强度.

Fig.11 The principle diagram of the structure of N-bit tri-state optical data discriminator图11 N位三态光数据判断器结构原理图

5 判断器硬件设计及仿真验证

根据图10所示的MSD数据判断器结构原理图,可以选择目前市场上的已有元器件或芯片,设计出符合逻辑关系的各种各样的判断器.本设计的硬件结构由2部分组成:光处理部分(light processing section, LPS)和FPGA部分,3位MSD数据判断器硬件结构框架图如图12所示.在这个设计中,考虑到半反半透镜的尺寸较大且不易精确调整位置,故将其对光信号的叠加作用改为:用光电管感知每束光的光状态,再将光电管的输出电信号用FPGA中的电路进行叠加的方法,即将半反射镜的物理功能用感光管加电路来替代.

Fig. 12 The hardware frame structure diagram of 3 b MSD data discriminator图12 3位MSD数据判断器硬件结构框架图

5.1 硬件结构设计与实现

FPGA开发板采用的是Altera Cyclone Ⅲ系列,主芯片为780pin的BGA封装的EP3C120F780.以3位MSD数据为例的判断器共有12个光信号输入端,若将处理器的每个数据位的4个输出端中的2个水平光信号通路和2个垂直光信号通路进行合并,则3个数据位的判断器连接到FPGA的输入端就简化为6个;另外每个输入光信号在信号传递过程中,受到液晶是否旋光控制,而液晶状态需要一个反馈信号来控制,该信号通过FPGA输出获得,针对6个输入光信号需要6个液晶进行控制,所以需要FPGA以输出方式提供6个反馈控制信号;最后液晶正常工作需要一个稳定的方波电压信号,它也是通过FPGA输出来提供的.可见,为了满足判断器中光处理器部分的正常工作要求,FPGA需要提供至少13个输入输出引脚,本设计中所选择的FPGA开发板能够完全满足设计要求.对于判断器的判断结果,本设计利用FPGA开发板的现有资源,在40个可用引脚的左边,有2个表示状态的发光二极管LED13和LED15,用以指示判断结果.FPGA与光处理部分信号传递与逻辑控制引脚连接图,如图13所示:

Fig. 13 The connection diagram between FPGA and optical processing part of the pins图13 FPGA与光处理部分引脚连接图

光学处理部分输出的光信号需要转换成电信号才能被FPGA识别和处理,所以需要设计一个光电转换部分.本设计中,光电转换部分采用光敏电阻和双运放LM358P放大比较器2部分组成.其中光敏电阻型号为MG45,其特性为:当无光照射到光敏电阻上时,其暗阻阻值在几百kΩ左右;当有光照时,其亮阻阻值将为几kΩ,光敏电阻接收到的光强越强,其阻值就越低,有时甚至只有几百Ω.虽然MG45光敏电阻响应时间较慢,在ms和s之间,实际应用并不合适,但是不影响本实验验证判断器原理的正确性和可行性的目的.

光敏电阻和LM358P连接的电路原理图如图14所示:

Fig. 14 The principle diagram of the photoelectric conversion circuit图14 光电转换电路原理图

图14中LM358P引脚2为反相输入端,引脚3为同相输入端,当LM358P的反相输入端电位高于同相输入端电位时,输出电压Vo为低电平;当LM358P的反相输入端电位低于同相输入端电位时,输出电压Vo为高电平.RL表示光敏电阻,当光敏电阻受到光照时,其阻值发生改变.当无光照射到光敏电阻时,(R2R1)>(R3R4),放大器输出为0,Vo输出低电平;而当有光照射到光敏电阻时,其阻值迅速减小,使(R2R1)<(R3R4),输出高电平,Vo=Vcc,实现了通过光敏电阻控制Vo输出高低电平.

MSD数据判断器是对三值光学运算器的光信号输出结果进行正负性判断的,理论上应该将MSD数据判断器直接连接到运算器的输出端,但是由于器件原因暂时无法实现.而本实验采用的是LED发光二极管的亮与灭来代替运算器的每个数据位相应的光信号输出状态,通过外加的手动开关控制相应的光信号的输入.三值光学运算器每个数据位的4个像素位,同时最多只能有一个像素位输出相应的光状态,对应本实验的每个数据位的光信号输入端,最多也只能允许有一个光信号输入.为了避免因人为误操作而出现使同一个数据位有不止一种输入光状态的非正常现象,设置了开关结构.该结构中,每个数据位采用2个独立光源,一个单刀双掷开关和一个单刀单掷开关,以保证每个数据位不会出现2个光输入端出现同时有光状态的现象.开关控制电路图如图15所示:

Fig. 15 The control circuit of single pole double throw switch图15 单刀双掷开关控制电路图

图15中,开关SW1断开时,无论SW2连接到哪一个端口,LED的D1和D2均不发光,表示该光信号对应的数据位的输入为无光态.开关SW1闭合后,当SW2连接到上端口时,发光二极管LED的D1亮而D2不亮,表示该数据位的输入光状态为水平偏振光;当SW2连接到下端口时,发光二极管LED的D1不亮而LED的D2亮,表示该数据位的输入光状态为垂直偏振光.

液晶部分采用的是EDC006大尺寸TN型正显7段段码液晶,其尺寸为72.6×52.8 mm2,工作电压为5 V,采用静态驱动方式即可.图16所示的是一个电极型笔段式液晶驱动的电路原理图、真值表及波形图.

图16(a)中是一个液晶的异或门驱动电路,振荡脉冲信号直接输入到异或门的输入端A,同时连接到段码液晶的背电极端C端,输入端B可以接高低电平,用于控制液晶电极的亮与灭.图16(b)为异或门的真值表.由图16(b)可知,当B为高电平时,A和C两端的电平刚好一高一低,当A输入具有适当频率和适当幅度电压的方波信号时,即可满足液晶的驱动电压要求,使液晶相应段码显示而呈黑色;而当B为低电平时,A和C两端电压同为高电平或低电平,没有电位差,液晶不显示,使其呈透明状能透光.实验所使用的FPGA输出的电压为2.5 V,而液晶所需要的工作电压为5 V,刚好满足要求.

Fig. 16 The drive principle and waveform of segment code LCD图16 段码液晶的驱动原理和波形图

实际电路中,为了方便观察和控制,我们采用了3片段码液晶EDC006,单片液晶的段码分布如图17所示,每片使用其中的2个段码,表示三值数据的一个位,比如用A段表示数据位的A3v光通路,D段表示数据位A3h光通路.

Fig. 17 The schematic diagram of segment code LCD EDC006图17 段码液晶EDC006示意图

EDC006液晶模块的背面有偏振片,正面也有偏振片,中间是液晶模块,对应的引脚是用电信号来控制各个段码的亮与灭的.

这里需要说明的是:在同一个数据位选择了相同类型的液晶,但是并不影响本实验的结果.因为最终所有光信号都转换为电信号,通过FPGA进行电处理,所以该方案仍是可行的.

5.2 Quartus Ⅱ软件仿真

本文所提出的MSD数据判断器结构,其工作原理也可以通过软件仿真来验证.因为本设计使用的开发板为Cyclone Ⅲ系列,所以采用Altera提供的Quartus Ⅱ平台非常合适.Quartus Ⅱ设计工具支持VHDL,Verilog的设计流程,其内部嵌有VHDL,Verilog逻辑综合器.Quartus Ⅱ也具备仿真功能,支持第三方的仿真工具,如ModelSim.

1) 基于Quartus Ⅱ软件平台,在新建立的工程设置窗口中,逐一选择Cyclone Ⅲ开发板、引脚780pin、芯片型号为EP3C120F780C7等参数,如图18所示,完成开发环境配置参数的设置.

Fig. 18 The schematic diagram of chip selection图18 芯片选型图片示意图

2) 在工程建立完成后,建立Verilog程序的文件,并根据功能需求编写相应的程序,所编写程序的核心部分包括:液晶控制信号的异或门程序、输入信号优先级的逻辑程序等.所用液晶工作频率为32 Hz左右,而FPGA开发板自带的时钟为125 MHz,所以需对该时钟信号进行4分频,通过编写Verilog程序,以计数器方式精确分频来实现.

3) 查询FPGA开发板的相关手册,配置引脚再编译完成后,在新建的VWF文件中导入之前编译生成的QSF文件,设置结束时间为60 μs,单格时间间隔为1 μs,运行仿真后,其结果如图19所示.

Fig. 19 The software simulation results diagram图19 软件仿真结果示意图

图19中,y2和y1均为低电平有效,其他均为高电平有效.FPGA开发板的硬件电路定义了低电平时,绿色发光二极管D13和D15亮,高电平时灭.为了降低成本和尽量减少外部接线,选择的开发板上用户可自己定义这2个二极管的亮和灭作为观察判断结果的依据.

5.3 测试结果分析

根据5.1节所述的硬件设计方案进行硬件电路的连接和调试成功后,将事先编写的程序下载到FPGA芯片上,并将相应的输入输出贴好对应的标签,以便观察结果.硬件器件连接图如图20所示:

Fig. 20 The hardware connection diagram图20 硬件连接示意图

图20中左侧的3块液晶用来表示3个数据位的输入状态,最上面的一块表示最低位,中间的表示次高位,下面的表示最高位.每个液晶模块用2个对应的发光二极管的亮和灭来表示每个数据位的输入光状态.当液晶上段对应的红色发光二极管亮时,表示该数据位输入的是水平偏振光;当液晶模块下段对应的红色发光二极管亮时,表示该数据位输入的是垂直偏振光;当该液晶模块对应的2个红色发光二极管都不亮时,表示无光输入.这2个红色发光二极管采用了单刀单掷的总开关和单刀双掷的选择开关,所以是不会出现单个液晶模块对应的2个发光二极管同时亮的现象.

在右边的FPGA开发板上,在2个绿色LED旁贴了“+”号和“-”号,用来表示正负值的判断结果.贴有“+”号的LED灯亮,表示输入的数据为正数;贴有“-”号的LED灯亮,表示输入的数据为负数;当2个LED灯都不亮时,表示输入的数据为零值.

同时,当最高有光输入的数据位,该位的光状态能使FPGA的输出点亮该位及更低位的表示与其相异的偏振光态的相应液晶,以屏蔽掉表示不同输入光状态的数据位的光通路,使该位及更低位的数据位的输出只能为表示该偏振光态的类型.

比如,最高位表示垂直偏振光的a6灯亮,则a6的输入将点亮a5,a3,a1对应的液晶,使其屏蔽掉该位表示水平偏振光的a5,a3,a1的输入光状态.同时点亮FPGA开发板上贴有正号的LED灯D15,表示该数为正.

当最高位表示水平偏振光的a5灯亮,则a5的输入将点亮a6,a4,a2对应的液晶,使其屏蔽掉该位表示垂直偏振光的a6,a4,a2的输入光状态.同时点亮FPGA开发板上的贴有负号的LED灯D13,表示该数为负.

当最高位输入为无光态,则数的正负由次高位的输入光状态决定.

当次高位表示垂直偏振光的a4灯亮时,a4的输入将点亮a3,a1对应的液晶,使其屏蔽掉该位表示垂直偏振光的a3,a1的输入光状态.同时点亮FPGA开发板上的贴有正号的LED灯D15,表示该数为正.

当次高位表示水平偏振光的a3灯亮时,a3的输入将点亮a4,a2对应的液晶,使其屏蔽掉该位表示垂直偏振光的a4,a2的输入光状态.同时点亮FPGA开发板上的贴有负号的LED灯D13,表示该数为负.

以此类推.仅当这3 b输入均为无光态时,此时液晶都不亮,2个表示正负结果的LED灯也都不亮,表示判断结果为零值.

本次实验对3个数据位的27种状态组合全部进行了验证,并对实验测试结果做了记录.各种输入状态下,实验测试结果与理论分析结果之间的对照关系如表9所示,表9中亮用1表示,灭用0表示,结果中的正数用PN表示,负数用NN表示,零用zero表示.由表9可知,实验测试结果与理论分析结果完全一致,证实了理论的正确性和设计的可行性.

Table 9 The Compared Table Between Experimental Results and Theoretical Results

6 结 论

三值光学计算机的MSD数据判断器是在2014年前后研究“运算例程”时所遇到的新课题,截止到目前还未见到相关的报道,本文首次提出“三值光学计算机的MSD数据判断器”的设计思想并实现.而MSD数据判断器是三值光学计算机的重要部件之一,它可以解决MSD数据的正/负值判断和零值判断问题.对MSD数据判断器的研究,必将加快三值光计算机整体进入应用阶段的步伐.

虽然本文已设计出了固定位长的MSD数据判断器,可供暂时解决三值光学计算机无判断器的难题.但是仍然存在很多的不足,比如此次设计的判断器都是单独测试验证的,单个数据位都是以2个光输入端为例设计的,使用在三值光学计算机上时,每个数据位都是4个光状态输入端,则相应的判断器的输入端应增加成4个输入端,同时随着输入端数量的增加,数据位的对应问题以及半反半透镜和全反射透镜的对应问题就越发明显.如何解决上述问题将是接下来要考虑的问题.

另外,三值光学处理器的数据位现已达到数千位,而且任一数据位随时可以重构,同时可以分配给不同的运算器同时使用,这就要求理想的三值光学计算机的MSD数据判断器也最好根据处理器的重构和数据位的重新分配,做相应的调整以使其满足并行判断的需求,即MSD数据判断器的可重构性.对判断器可重构进一步的研究,将是未来的主要工作内容之一.

[1]Jin Yi, Xu Qun, Ouyang Shan et al. Structured data computer—Application characteristics of a ternary optical computer[J]. Scientia Sinica Informationis, 2016, 46(3): 311-324 (in Chinese)

(金翊, 徐群, 欧阳山, 等. 结构量计算机——三值光学计算机的应用特点[J]. 中国科学: 信息科学, 2016, 46(3): 311-324)

[2]Jin Yi. Ternary optical computer principle and architecture[D]. Xi’an: Northwestern Polytechnical University, 2002 (in Chinese)

(金翊. 三值光计算机原理和结构[D]. 西安: 西北工业大学博士学位论文, 2002)

[3]Jin Yi, Ouyang Shan, Song Kai, et al. Management of many data bits in ternary optical computers[J]. Scientia Sinica Informationis, 2013, 43(3): 361-373 (in Chinese)

(金翊, 欧阳山, 宋凯, 等. 三值光学处理器的数据位管理理论和技术[J]. 中国科学: 信息科学, 2013, 43(3): 361-373)

[4]Jin Yi, Wang Hongjian, Ouyang Shan, et al. Principles, structures, and implementation of reconfigurable ternary optical processors[J]. Scientia Sinica Informationis, 2012, 42(6): 778-788 (in Chinese)

(金翊, 王宏健, 欧阳山, 等. 可重构三值光学处理器的原理、基本结构和实现[J]. 中国科学: 信息科学, 2012, 42(6): 778-788)

[5]Yan Junyong, Jin Yi, Zuo Kaizhong. Reducing design theory of non-incoming bit operators and its application in three-valued light computer[J]. Scientia Sinica Informationis, 2008, 38(12): 2112-2122 (in Chinese)

(严军勇, 金翊, 左开中. 无进(借)位运算器的降值设计理论及其在三值光计算机中的应用[J]. 中国科学: 信息科学, 2008, 38(12): 2112-2122)

[6]Ouyang Shan, Peng Junjie, Jin Yi, et al. Structure and theory of dual-space storage for ternary optical computer[J]. Scientia Sinica Informationis, 2016, 46(6): 743-762 (in Chinese)

(欧阳山, 彭俊杰, 金翊, 等. 三值光学计算机双空间存储器的结构和理论[J]. 中国科学: 信息科学, 2016, 46(6): 743-762)

[7]Zhan Xiaoqi, Peng Junjie, Jin Yi, et al. Static allocation strategy of data bits of ternary optical computer[J]. Journal of Shanghai University (Natural Science), 2009, 15(5): 528-533 (in Chinese)

(詹小奇, 彭俊杰, 金翊, 等. 三值光计算机数据位资源的静态分配策略. 上海大学学报: 自然科学版, 2009, 15(5): 528-533)

[8]Jin Yi, Gu Yingying, Zuo Kaizhong. Theory, technology and progress of a ternary optical computer’s decoder[J]. Scientia Sinica Informationis, 2013, 43(2): 275-286 (in Chinese)

(金翊, 顾莹莹, 左开中. 三值光学计算机解码器的理论、技术和实现[J]. 中国科学: 信息科学, 2013, 43(2): 275-286)

[9]Shi Yeqiang, Jin Yi, Ouyang Shan, et al. Design of parallel photosensitive array in ternary optical computer decoder[J]. Journal of Shanghai University (Natural Science), 2016, 22(4): 4495-460) (in Chinese)

(石也强, 金翊, 欧阳山, 等. 三值光学计算机解码器中并行感光阵列的设计[J]. 上海大学学报: 自然科学版, 2016, 22(4): 449-460)

[10]Huang Weigang, Jin Yi, Ai Lirong et al. Design and implementation of the 100 bit coder for ternary optical computers[J]. Computer Engineering & Science, 2006, 28(4): 139-142 (in Chinese)

(黄伟刚, 金翊, 艾丽蓉, 等. 三值光计算机百位编码器的设计与构造[J]. 计算机工程与科学, 2006, 28(4): 139-142)

[11]Jin Yi, Shen Yunfu, Peng Junjie, et al. Principles and construction of MSD adder in ternary optical computer[J]. Scientia Sinica Informationis, 2011, 41(5): 541-551 (in Chinese)

(金翊, 沈云付, 彭俊杰, 等. 三值光学计算机中MSD加法器的理论和结构[J]. 中国科学: 信息科学, 2011, 41(5): 541-551)

[12]Song Kai, Yan Liping. The symmetric MSD encoder for one-step adder of ternary optical computer[J]. Optics Communications, 2016, 372(08): 221-228

[13]Song Kai, Yan Liping. Design and implementation of the one-step MSD adder of optical computer[J]. Applied Optics, 2012, 51(7): 917-926

[14]Hu Xiaojun, Jin Yi, Ouyang Shan, et al. A 40 bit multiplication routine of ternary optical computer[J].

Journal of Shanghai University (Natural Science), 2014, 20(5): 645-657 (in Chinese)

(胡晓俊, 金翊, 欧阳山, 等. 三值光学计算机的40位乘法例程[J]. 上海大学学报: 自然科学版, 2014, 20(5): 645-657)

[15]Xu Qun, Jin Yi, Shen Yunfu et al. MSD iterative division algorithm and implementation technique for a ternary optical computer[J]. Scientia Sinica Informationis, 2016, 46(4): 539-550 (in Chinese)

(徐群, 金翊, 沈云付, 等. 三值光学计算机的MSD迭代除法算法和实现技术[J]. 中国科学: 信息科学, 2016, 46(4): 539-550)

[16]Avizienis A. Signed-digit number representations for fast parallel arithmetic[J]. IRE Trans on Electronic Computers, 1961, 10(3): 389-400

[17]Draker B L, Bocker R P, Lasher M E, et al. Photonic computing using the modified signed-digit number representation[J]. Optical Engineering, 1986, 25(1): 38-43

Zhang Honglie, born in 1966. PhD. Professor. Senior member of CCF. Her main research interests include ternary optical computer and embedded system.

Zhou Jian, born in 1987. Master. His main research interest is ternary optical computer.

Zhang Sulan, born in 1980. PhD. Her main research interest is ternary optical computer.

Liu Yanju, born in 1974. PhD. Professor. Her main research interests include surface reconstruction, intelligence control and deep learning.

Wang Xianchao, born in 1973. PhD. Member of ACM and senior member of CCF. His main research interests include optical computing, complex network, big data and machine learning.

Design and Implementation of Positive and Negative Discriminator of MSD Data for Ternary Optical Processor

Zhang Honglie1, Zhou Jian1, Zhang Sulan2, Liu Yanju1, and Wang Xianchao3

1(CollegeofComputerandControlEngineering,QiqiharUniversity,Qiqihar,Heilongjiang161006)2(SchoolofComputerEngineeringandScience,ShanghaiUniversity,Shanghai200072)3(SchoolofMathematicsandStatistics,FuyangTeachersCollege,Fuyang,Anhui236041)

The numerical positive/negative or zero value discriminator is a key component to compare the data size in computer. With the advent of the MSD (modified signed-digit) parallel adder which using three state optical signal to express number in the ternary optical processor, the research of positive/negative or zero value discriminator of MSD digit is becoming an important test to perfect ternary optical processor. Based on the characteristics of MSD data and the correspondence of the optical signal and the MSD digit, this paper proposes a method to ascertain the positive/negative or zero value of the multi-bit MSD data via direct analysis of a group of tree state optical signals which expressing the MSD data. By applying this method to the subtraction result of MSD data, it is realized to discriminate the size of two MSD data. According to the above theory, in this paper a structure of MSD data discriminator is established, which is made of polarizer, liquid crystal and half-mirror. In addition to FPGA as the control circuit, a 3-bit MSD data discriminator is realized. The validity of the discriminator is proved by some experiment, and the correctness of the basic theory and the feasibility of the structural design are proved too.

ternary optical processor; positive/negative value judgment method of MSD data; structure design of the discriminator; hardware design of the discriminator

2017-02-27;

2017-04-13

国家自然科学基金项目(61672006);黑龙江省自然科学基金项目(F201440) This work was supported by the National Natural Science Foundation of China (61672006) and the Natural Science Foundation of Heilongjiang Province (F201440).

TP38