驱动回路参数对碳化硅MOSFET开关瞬态过程的影响

王旭东 朱义诚 赵争鸣 陈凯楠

(清华大学电机系 电力系统及发电设备安全控制和仿真国家重点实验室 北京 100084)

驱动回路参数对碳化硅MOSFET开关瞬态过程的影响

王旭东 朱义诚 赵争鸣 陈凯楠

(清华大学电机系 电力系统及发电设备安全控制和仿真国家重点实验室 北京 100084)

在电力电子系统中,碳化硅(SiC)MOSFET的开关特性易受系统杂散参数的影响,表现为电磁能量脉冲形态属性的非理想特性,并进一步影响系统效率和可靠性。针对SiC MOSFET,首先分析控制脉冲、驱动脉冲及电磁能量脉冲三者间形态属性的关系,提取影响SiC MOSFET开关瞬态过程的关键参数,即开关过程中的dv/dt和di/dt。基于SiC MOSFET的开关过程,分析驱动回路参数对dv/dt和di/dt的影响,并通过PSpice仿真及搭建SiC MOSFET双脉冲测试实验平台进行分析和比较。在此基础上,对基于驱动回路参数的瞬态控制方法进行对比分析,为实际应用中对SiC MOSFET的开关特性改善提供重要的理论基础。

碳化硅MOSFET 脉冲 杂散参数 开关特性

0 引言

相较于硅(Silicon, Si),碳化硅(Silicon Carbide, SiC)材料具有更宽的禁带宽度,更高的击穿场强及更高的热传导率[1,2]。与同等硅器件相比,SiC MOSFET具有更小的结电容和导通电阻,可以实现10倍以上的开关速度[3]。因此,基于SiC器件的电力电子系统往往有更高的系统效率和功率密度[4]。但同时更高的开关速度意味着在开关过程中有更高的dv/dt和di/dt,因而更容易受系统杂散参数的影响,表现为较强的电磁能量脉冲非理想特性,如能量脉冲的延迟和畸变。这些非理想瞬态行为威胁着电力电子系统的稳定可靠运行,容易造成器件失效和装置损坏[5]。

针对功率开关器件的开关特性控制,主要有控制算法层面、主电路层面及驱动电路层面三类控制方式。控制算法层面主要有死区控制及输出失真补偿,解决由于电磁能量脉冲延迟引起的系统故障(如桥臂直通)及输出失真问题[6-8],但无法改善开关过程的瞬态行为,如电压、电流的尖峰和振荡现象。主电路层面通过缓冲吸收电路抑制开关瞬态过程的过电压和过电流[9,10],以及使用软开关技术改变功率开关器件的开关轨迹,降低开关损耗[11,12]。但两者均需在主电路侧加入无源或有源元件,造成系统体积和成本的增加,且加入的元件也往往会带来额外的损耗及过电压和过电流问题。近年来,从驱动电路层面对器件开关瞬态过程进行控制的研究受到更多关注,主要分为变驱动电阻、变驱动电压、变驱动电流三种控制方式[13]。相比于前两类控制方法,驱动侧控制可控性更高,且无需对主电路进行改动,可减小系统体积和损耗[14]。但目前针对SiC MOSFET的驱动控制方法研究相对较少,且主要针对特定的变换器系统设计,缺乏对一般性影响规律的认识和分析。

因此,分析驱动回路参数对SiC MOSFET开关瞬态过程的影响规律,对于研究SiC MOSFET的驱动控制方法有着重要的指导意义。目前国内外在系统杂散参数对功率开关器件的开关特性影响方面进行了广泛的研究,取得了较大的进展。文献[15]通过实验的方法研究了驱动回路、主回路以及共源极杂散电感对MOSFET开关特性的影响。文献[16,17]分阶段对MOSFET的开通关断过程建立了分析模型,比较全面地研究了杂散电感、器件结电容以及驱动电阻对开关特性的影响,并进行了实验验证。但是所建立的分析模型比较复杂,难以直观地反映杂散参数的影响规律。文献[18]研究了非线性结电容对于SiC MOSFET开关瞬态过程的影响,并提出了改进的开关仿真模型,但并未考虑驱动回路的影响。文献[19]研究了SiC器件由于驱动电压振荡引起的自维持振荡现象,类似的稳定性问题也在SiC MOSFET模块中进行了研究[20]。然而这些研究主要针对一些特定的问题进行,对驱动回路参数的影响分析不够全面,也不具有一般性。

本文在上述研究工作的基础上,分析控制脉冲、驱动脉冲和电磁能量脉冲的相互关系,提取影响SiC MOSFET开关瞬态过程的关键参数,即开关过程中的dv/dt和di/dt。通过理论分析和实验验证,分析了驱动回路参数对dv/dt和di/dt的影响规律,并对比分析了各驱动参数对开关瞬态行为的可控性及对系统性能的影响规律。

1 开关瞬态过程的非理想特性

1.1 脉冲形态属性关系

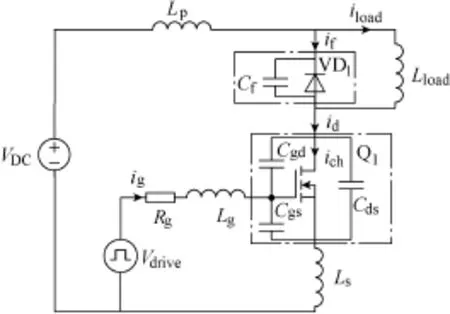

双脉冲测试电路一般多用于分析功率开关器件的开关特性。考虑了系统中主要杂散参数的双脉冲测试电路如图1所示,其中Q1为待测试的SiC MOSFET,VD1为SiC肖特基势垒二极管(Schottky Barrier Diode, SBD)。

图1 考虑杂散参数的双脉冲测试电路Fig.1 Double pulse test circuit with parasitic parameters

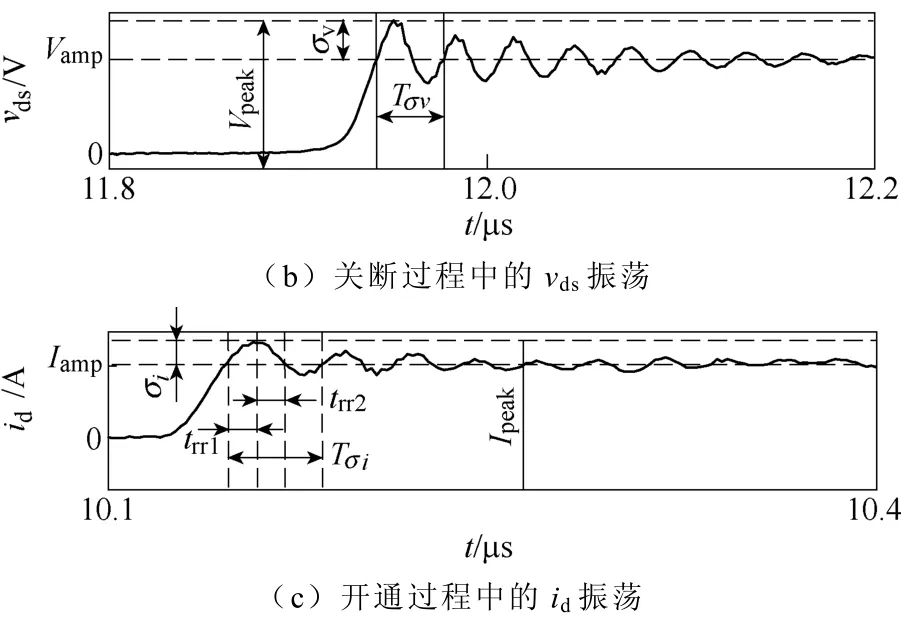

基于双脉冲测试电路的典型实验波形,得到控制脉冲vctr、驱动脉冲vgs、电磁能量脉冲vds与id的延迟和畸变关系,如图2a所示。

从控制角度来讲,设计者更关注控制脉冲到电磁能量脉冲的延迟,分别为tdon和tdoff。脉冲的畸变主要指功率开关器件输出的电磁能量脉冲与理想方波脉冲的差异,从控制脉冲到电磁能量脉冲的畸变关系反映了控制信息的变化规律,也会影响系统控制性能。如图2所示,电磁能量脉冲与控制脉冲的畸变关系主要有以下三方面:

图2 脉冲间的延迟和畸变关系Fig.2 Delay and deformation among the pulses

1)上升沿、下降沿的过渡过程,可用dv/dt和di/dt表征。

2)电流、电压尖峰如图2所示,其中开通过程中的Ipeak由续流二极管的反向恢复电流(对Si Diode而言)或结电容充电电流(对SiC SBD而言)引起,可近似表示为[16]

式中,Qrr为反向恢复电荷,对于SiC SBD则为结电容充电电荷;S=trr2/trr1。关断电压尖峰主要由回路杂散电感的感应电压引起,可表示为

3)电流、电压振荡,可用振荡周期和最大振荡幅值表征。其中振荡周期也可由振荡频率表征。这里主要分析器件开通过程中的电流振荡和关断过程中的电压振荡。开关过程中的高频振荡主要来源于回路杂散电感与开关器件结电容的串联谐振。对于开通过程中的电流振荡,如图2c所示,振荡周期可近似表示为

同理,对关断过程的电压振荡,如图2b所示,振荡周期可近似表示为

当器件选型及电路结构选定后,振荡频率基本确定。最大振荡幅值则与电流、电压尖峰有关,即可见,最大振荡幅值会影响器件电压电流的高频分量及系统电磁干扰(Electromagnetic Interference, EMI)性能,因此应当受到关注。

1.2 关键控制参数

脉冲间的延迟与畸变关系会对系统性能产生多方面影响,如功率器件的电应力、开关损耗、输出失真以及EMI等。其中延迟主要影响输出失真,可通过常规的闭环PWM算法予以补偿。而畸变关系主要影响系统瞬态性能,是短时间尺度瞬态控制的主要研究对象。然而如1.1节所示,脉冲间的畸变关系有多种表现形式,为了在考虑多种畸变关系的同时,降低控制的复杂度,需提取出影响畸变关系的关键参数。

从1.1节对脉冲畸变关系的分析看出,三种畸变关系均与器件开通关断过程中的dv/dt及di/dt有关。其中电磁能量脉冲上升沿与下降沿的过渡过程可直接由dv/dt和di/dt表征,电压电流尖峰则会受di/dt影响,而峰值电流和电压又同时影响了电磁能量脉冲振荡的幅值。因此将器件开通关断过程中的dv/dt和di/dt作为对器件瞬态开关特性进行控制的关键控制参数。

2 控制参数影响因素分析

在确定了瞬态控制参数后,关键是分析控制参数的主要影响因素。本节以SiC MOSFET为对象,分析驱动回路参数对dv/dt和di/dt的影响。如图1所示,驱动回路参数主要包括驱动电阻Rg、驱动杂散电感Lg、共源极电感Ls、栅源极电容Cgs以及栅漏极电容Cgd。驱动回路中,Lg的增加会引起驱动电压的振荡,易造成开关器件误动作,而Ls的增加则会降低器件开关速度,增加开关损耗。因此,从设计角度来看,一般要求Lg和Ls尽量小,即将驱动电路尽可能地靠近开关器件。因此,为了简化分析,下面主要分析Rg、Cgs及Cgd对SiC MOSFET开关过程中dv/dt和di/dt的影响,并在理论推导中忽略Lg和Ls,以及跨导(gfs)和Cgd的非线性。

2.1 电压变化率dv/dt

2.1.1 开通过程

SiC MOSFET开通过程的dv/dt发生在id上升至负载电流Iload,驱动电流通过Cgd充电阶段。此时,驱动电压维持在米勒电压附近,可近似表示为

式中,Vth为阈值电压。

此时驱动电流ig为

式中,VCC为开通时的驱动电压;Vmiller为米勒电压。

根据式(7)和式(8),推导得到开通过程dv/dt的表达式为

2.1.2 关断过程

SiC MOSFET关断过程的dv/dt发生在vgs下降至米勒电压附近,ig对Cgd放电阶段。类似开通过程的推导过程,可得到关断过程dv/dt的表达式为

式中,VEE为关断时的驱动电压。

2.2 电流变化率di/dt

2.2.1 开通过程

SiC MOSFET开通过程的di/dt发生在vgs升至Vth后,ig对Cgs的充电阶段。此时id可近似表示为

Cgs充电过程表达式为

ig的表达式为

根据式(11)~式(13)可以得到开通过程di/dt开始时刻的表达式为

2.2.2 关断过程

SiC MOSFET关断过程的di/dt发生在vds升至母线电压Vbus后,ig对Cgs的放电阶段。类似开通过程的推导分析,可得到关断过程di/dt开始时刻的表达式为

2.3 分析讨论

以上分析表明,开关过程中的dv/dt主要受Rg和Cgd影响,而di/dt主要受Rg和Cgs影响。然而上述推导建立在忽略Lg、Ls及gfs、Cgd的非线性的假设条件下,考虑与实际系统的差异,有必要通过仿真和实验的方法,定量分析驱动回路参数对开关过程中dv/dt和di/dt的影响。

3 仿真与实验

3.1 仿真模型介绍

在PSpice仿真软件中搭建双脉冲测试的仿真电路,电路原理如图1所示。主电路元件包括SiC MOSFET、SiC SBD、负载电感、直流母排吸收电容与杂散电感、电阻,其中负载电感与吸收电容模型采用高频等效电路模型。

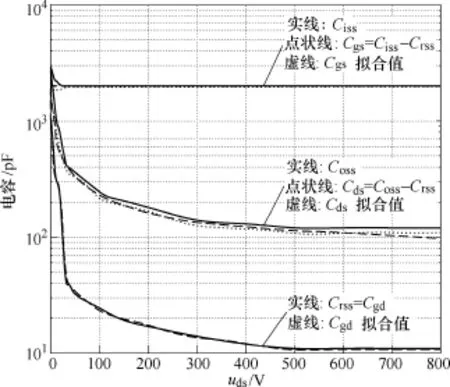

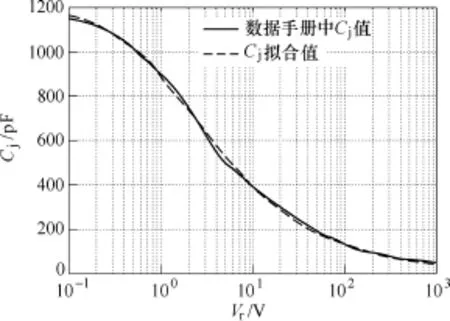

SiC MOSFET为Wolfspeed公司的CMF20120D,SiC SBD为Wolfspeed公司的C4D30120D。在Wolfspeed提供的PSpice模型基础上,对器件结电容的非线性特性进行了修正,拟合结果分别如图3和图4所示。图3中,Ciss、Coss及Crss分别为MOSFET的输入电容、输出电容及反向传输电容。

图3 SiC MOSFET CMF20120D的寄生电容Fig.3 Parasitic capacitances of CMF20120D

图4 SiC SBD C4D30120D的结电容Fig.4 Junction capacitance of C4D30120D

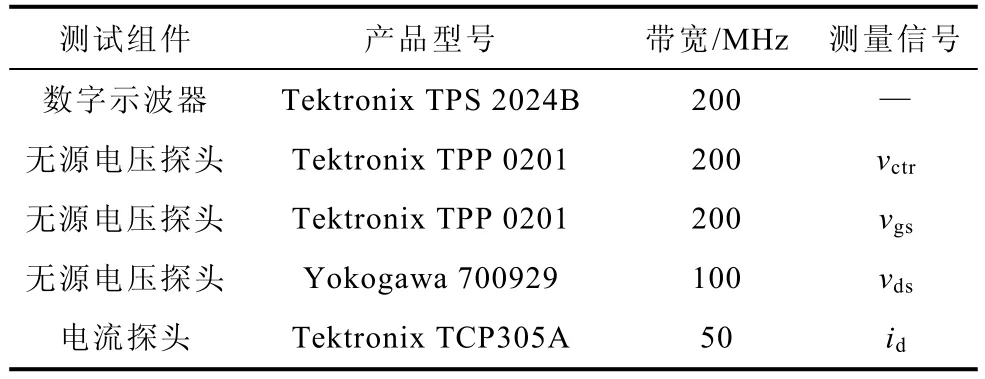

3.2 实验平台介绍

图5为双脉冲实验测试电路。控制信号与驱动信号用光纤隔离,以抑制EMI。同时将0.47μF的吸收电容放在开关器件附近,以抑制电压振荡。为了使实验结果准确可信,需使用宽频带的测试探头与示波器,相关参数见表1。同时尽量缩短电压探头接地回路,以减小EMI对测量结果的影响。另外也对电压、电流探头的延迟进行了校正。

图5 双脉冲测试电路Fig.5 Double pulse tester

表1 测试平台参数Tab.1 Parameters of measurement setup

3.3 结果分析

不同Rg、Cgd、Cgs下的开关波形如图6~图8所示,其中Cgd、Cgs的改变是通过改变并联在SiC MOSFET栅漏极和栅源极的外部电容Cgd(ext)和Cgs(ext)实现的。从图中可以看出,仿真结果与实验波形比较吻合。

图6 不同Rg下的仿真与实验波形对比Fig.6 Simulation and experimental waveforms comparison with different Rg

图7 不同Cgd下的仿真与实验波形对比Fig.7 Simulation and experimental waveforms comparison with different Cgd

图8 不同Cgs下的仿真与实验波形对比Fig.8 Simulation and experimental waveforms comparison with different Cgs

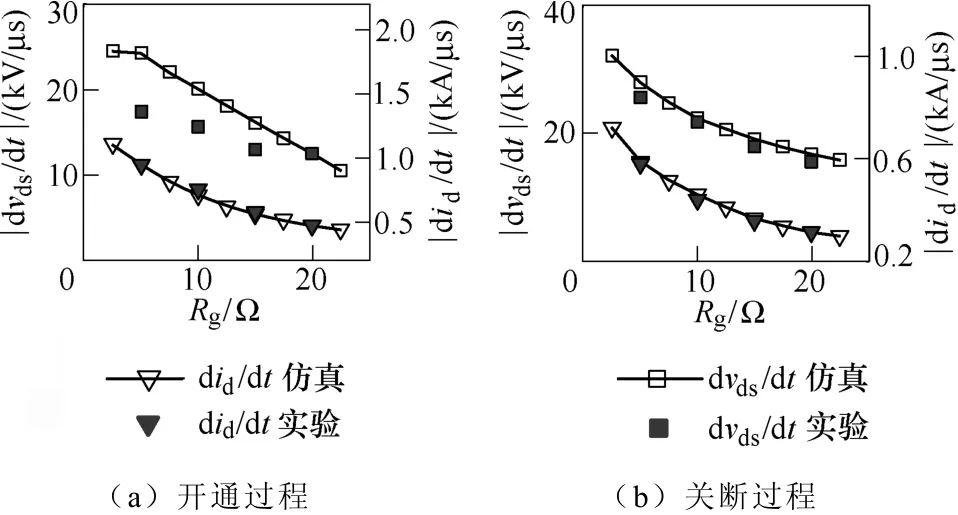

图9 不同Rg对dv/dt和di/dt的影响Fig.9 Impact of different Rgon dv/dt and di/dt

图10 不同Cgd对dv/dt和di/dt的影响Fig.10 Impact of different Cgdon dv/dt and di/dt

图11 不同Cgs对dv/dt和di/dt的影响Fig.11 Impact of different Cgson dv/dt and di/dt

图9表明,Rg对SiC MOSFET开关过程的dv/dt及di/dt均有影响。对实验结果的变化趋势进行分析:当Rg从5Ω增至20Ω时,开通与关断过程的dv/dt数值分别下降了29%及40%,而开通与关断过程的di/dt数值分别下降了50%及45%。这表明随着Rg的增加,SiC MOSFET开关过程中的dv/dt及di/dt数值上均有明显的下降趋势,与理论分析一致。

在图10中,Cgd(ext)的变化同样会对SiC MOSFET开关过程的dv/dt及di/dt产生影响。当Cgd(ext)从0变化至49.5pF时,开通与关断过程的dv/dt数值分别下降了47%及44%,而开通与关断过程的di/dt数值分别下降了14%及16%。这表明Cgd的增加会使SiC MOSFET开关过程的dv/dt数值有明显下降,与理论分析结果一致。但di/dt数值也会随Cgd的增加,有轻微的下降趋势,这主要是由于在di/dt阶段,小部分驱动电流也会流经Cgd,因而等效输入电容Ciss会随着Cgd的增加而增加,进而通过vgs影响di/dt。

图11研究了Cgs对SiC MOSFET开关过程的影响。其中开通过程的dv/dt数值呈现先增加后下降的趋势,关断过程的dv/dt数值呈现下降趋势。以实验数据为例,当Cgs(ext)从1 000pF增至4 400pF时,开通过程中的dv/dt数值只下降了7%,而关断过程中的dv/dt数值也只下降了12%。对于di/dt,数值上仿真与实验结果均呈现下降趋势,同样以实验结果为例,当Cgs(ext)从1 000pF增至4 400pF时,开通与关断过程的di/dt数值分别下降了36%与31%,下降效果显著,与理论分析结果一致。

4 控制方法分析比较

通过研究驱动回路主要参数对SiC MOSFET开关过程的影响,将为研究基于驱动参数来改善SiC MOSFET开关特性的瞬态控制方法提供参考。下面将分别从dv/dt及di/dt的可控性及系统性能方面,对基于Rg、Cgd、Cgs的瞬态控制方法进行比较分析。

4.1 可控性

仿真及实验结果表明,驱动参数对SiC MOFET开关过程中的dv/dt及di/dt呈现不同的影响关系,进而会影响改变驱动参数对dv/dt及di/dt的控制效果。根据3.3节实验结果可以看出:Rg对SiC MOFET开通和关断过程中的dv/dt及di/dt均具有较强的可控性。而Cgd对di/dt的可控性较弱,但对dv/dt有较强的可控性。与Cgd相反,Cgs对SiC MOSFET开关过程的控制效果则主要体现在开关过程中的di/dt上。

4.2 系统性能影响

SiC MOSFET的开关特性将进一步影响系统性能,特别是瞬态特性,如开关损耗及开关器件所承受的电压与电流尖峰。

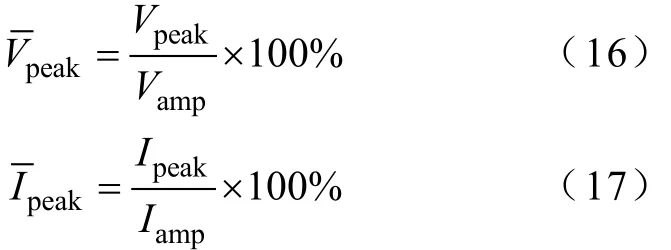

通过实验波形提取得到不同驱动参数下开关器件应力(电压尖峰与电流尖峰)以及开关损耗的关系,如图12所示。其中电压尖峰和电流尖峰均采用相对值进行表示,计算方法为

图12 Rg、Cgd、Cgs对器件应力与开关损耗的影响Fig.12 Impact of Rg, Cgdand Cgson device stress and switching loss

图12a和图12c表明,增加Rg或Cgs,会降低器件承受的电压和电流尖峰,但会引起开关损耗的增加。图12b表明,改变Cgd对器件的电流尖峰基本没有影响,但电压尖峰与开关损耗之间仍存在制约关系。

针对这一制约关系,可以将基于驱动参数的控制方法与主动钳位电路相结合,分别针对开关损耗和器件应力进行控制。另外,以上分析是针对在开通或关断过程中驱动参数保持不变的情况,若进一步对开关过程分阶段选择驱动参数,以实现dv/dt和di/dt的独立控制,则可进一步提升控制性能。

5 结论

本文对SiC MOSFET的开关瞬态过程进行了研究,通过分析控制脉冲、驱动脉冲及电磁能量脉冲间的延迟与畸变关系,提取出影响开关特性的关键控制参数,即开关过程中的dv/dt及di/dt。结合SiC MOSFET的开关过程,对影响dv/dt及di/dt的主要因素进行了理论分析,并通过双脉冲测试的仿真与实验结果,分析比较了不同驱动回路参数对SiC MOSFET开关过程中dv/dt及di/dt的影响。

结果表明,通过改变驱动参数控制dv/dt及di/dt,可以弥补宏观调制算法无法控制功率开关器件瞬态开关过程的不足,是改善开关特性的有效方法。本文进一步从可控性及系统性能影响的角度对基于Rg、Cgd、Cgs的瞬态控制方法进行了对比分析,其结果可为SiC MOSFET及类似的Si MOSFET或IGBT开关特性的改善而选择有效的瞬态控制方法提供重要的理论基础。

[1] Yan Q, Yuan X, Geng Y, et al. Performance evaluation of split output converters with SiC MOSFETs and SiC schottky diodes[J]. IEEE Transactions on Power Electronics, 2017, 32(1): 406-422.

[2] 梁美, 郑琼林, 可翀, 等. SiC MOSFET、Si CoolMOS和IGBT的特性对比及其在DAB变换器中的应用[J]. 电工技术学报, 2015, 30(12): 41-50. Liang Mei, Zheng Trillion Q, Ke Chong, et al. Performance comparison of SiC MOSFET, Si Cool-MOS and IGBT for DAB Converter[J]. Transactions of China Electrotechical Society, 2015, 30(12): 41-50. [3] Yi P, Murthy P K S, Wei L. Performance evaluation of SiC MOSFETs with long power cable and induction motor[C]//IEEE Energy Conversion Congress and Exposition (ECCE), 2016: 1-7.

[4] Biela J, Schweizer M, Waffler S, et al. SiC versus Si—evaluation of potentials for performance improvement of inverter and DC-DC converter systems by SiCpower semiconductors[J]. IEEE Transactions on Industrial Electronics, 2011, 58(7): 2872-2882.

[5] 赵争鸣, 白华, 袁立强. 电力电子学中的脉冲功率瞬态过程及其序列[J]. 中国科学E辑: 技术科学, 2007, 37(1): 60-69.

[6] Lewicki A. Dead-time effect compensation based on additional phase current measurements[J]. IEEE Transactions on Industrial Electronics, 2015, 62(7):4078-4085.

[7] Zhang Z, Wang F, Costinett D J, et al. Dead-time optimization of SiC devices for voltage source converter[C]//IEEE Applied Power Electronics Conference and Exposition (APEC), 2015: 1145-1152.

[8] 周娟, 陈映, 唐慧英, 等. 基于脉冲调整的四桥臂逆变器死区补偿策略[J]. 电工技术学报, 2016, 31(3): 16-24. Zhou Juan, Chen Ying, Tang Huiying, et al. Deadtime compensation strategy for four-leg inverter based on pulse-tuning[J]. Transactions of China Electrotechical Society, 2016, 31(3): 16-24.

[9] 罗剑波, 范伟, 彭凯. SiC MOSFET模块高频吸收电路研究[J]. 大功率变流技术, 2016, 31(5): 23-30. Luo Jianbo, Fan Wei, Peng Kai. High frequency snubber circuit for SiC MOSFET module[J]. High Power Converter Technology, 2016, 31(5): 23-30.

[10] Torsæter B N, Tiwari S, Lund R, et al. Experimental evaluation of switching characteristics, switching losses and snubber design for a full SiC half-bridge power module[C]//IEEE 7th International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Vancouver, BC, Canada, 2016: 1-8.

[11] 张强, 林维明. 一种最小应力的无源无损软开关方案[J]. 中国电机工程学报, 2016, 36(18): 4999-5008. Zhang Qiang, Lin Weiming. A novel lossless passive soft-switching cell with minimum stresses[J]. Proceedings of the CSEE, 2016, 36(18): 4999-5008.

[12] Hua G, Lee F C. Soft-switching techniques in PWM converters[J]. IEEE Transactions on Industrial Electronics, 1995, 42(6): 595-603.

[13] Shahverdi M, Mazzola M, Schrader R, et al. Active gate drive solutions for improving SiC JFET switching dynamics[C]//Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 2013: 2739-2743.

[14] Wittig B, Fuchs F W. Analysis and comparison of turn-off active gate control methods for low-voltage power MOSFETs with high current ratings[J]. IEEE Transactions on Power Electronics, 2012, 27(3):1632-1640.

[15] Chen Z, Boroyevich D, Burgos R. Experimental parametric study of the parasitic inductance influence on MOSFET switching characteristics[C]//The 2010 International Power Electronics Conference, Sapporo, Japan, 2010: 164-169.

[16] Wang J, Chung H S, Li R T. Characterization and experimental assessment of the effects of parasitic elements on the MOSFET switching performance[J]. IEEE Transactions on Power Electronics, 2013, 28(1):573-590.

[17] 巴腾飞, 李艳, 梁美. 寄生参数对SiC MOSFET栅源极电压影响的研究[J]. 电工技术学报, 2016, 31(13): 64-73. Ba Tengfei, Li Yan, Liang Mei. The effect of parasitic parameters on gate-source voltage of SiC MOSFET[J]. Transactions of China Electrotechical Society, 2016, 31(13): 64-73.

[18] Chen K, Zhao Z, Yuan L, et al. The impact of nonlinear junction capacitance on switching transient and its modeling for SiC MOSFET[J]. IEEE Transactions on Electron Devices, 2015, 62(2): 333-338.

[19] Lemmon A, Mazzola M, Gafford J, et al. Instability in half-bridge circuits switched with wide band-gap transistors[J]. IEEE Transactions on Power Electronics, 2014, 29(5): 2380-2392.

[20] Sadik D P, Kostov K, Colmenares J, et al. Analysis of parasitic elements of SiC power modules with special emphasis on reliability issues[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2016, 4(3): 988-995.

(编辑 张玉荣)

Impact of Gate-Loop Parameters on the Switching Behavior of SiC MOSFETs

Wang Xudong Zhu Yicheng Zhao Zhengming Chen Kainan

(State Key Lab of Control and Simulation of Power Systems and Generation Equipments Department of Electrical Engineering Tsinghua University Beijing 100084 China)

The switching behavior of Silicon Carbide (SiC) MOSFETs is susceptible to the parasitic elements in the system. It manifests non-ideal characteristics of the power pulses, and further limits the system reliability and efficiency. The relationship among the control pulse, the drive pulse and the power pulse is analyzed. Two parameters dv/dt and di/dt are extracted as two critical factors affecting the switching behavior of SiC MOSFETs. The impacts of the gate-loop parameters on dv/dt and di/dt are analyzed theoretically and verified through PSpice simulation and experiments. Furthermore, several transient control methods based on the gate-loop parameters are compared, as a guideline for the control of the switching behavior of SiC MOSFETs in real applications.

SiC MOSFET, pulse, parasitic parameters, switching behavior

TM131.2

王旭东 男,1991年生,博士研究生,研究方向为电磁能量收集和任意波形功率放大器。

E-mail: wxd13@mails.tsinghua.edu.cn

赵争鸣 男,1959年生,教授,博士生导师,主要研究方向为大功率电力电子变换系统、光伏发电、电机控制、无线电能传输等。E-mail: zhaozm@tsinghua.edu.cn(通信作者)

10.19595/j.cnki.1000-6753.tces.170389

国家自然科学基金重大项目资助(51490680,51490683)。

2017-04-05 改稿日期 2017-04-28