氮化硅等离子体刻蚀工艺研究

曲鹏程,唐代飞,向鹏飞,袁安波

(重庆光电技术研究所 工艺中心,重庆 400060)

氮化硅等离子体刻蚀工艺研究

曲鹏程,唐代飞,向鹏飞,袁安波

(重庆光电技术研究所 工艺中心,重庆 400060)

针对氮化硅刻蚀工艺中硅衬底刻蚀损伤的问题。为了提高氮化硅对二氧化硅的刻蚀选择比,采用CF4,CH3F和O2这3种混合气体刻蚀氮化硅,通过调整气体流量比、腔内压强及功率,研究其对氮化硅刻蚀速率、二氧化硅刻蚀速率及氮化硅对二氧化硅选择比等主要刻蚀参数的影响。实验表明,在CH,F流量为25 ,O2流量为40 sccm,腔内压强为67 Pa,功率为150 W的条件下,得到氮化硅对二氧化硅选择比为15∶1,非均匀性3.87% 的氮化硅刻蚀工艺。

氮化硅;二氧化硅;等离子体刻蚀;选择比

半导体制造工艺中,刻蚀工艺是一个重要的工艺步骤,主要原理是利用光刻胶做掩膜,通过物理溅射和化学作用刻蚀介质层,将图形转移到介质层上,形成器件的结构。刻蚀分为干法刻蚀和湿法腐蚀,干法刻蚀是反应气体形成等离子体后对介质进行刻蚀,而湿法腐蚀是利用化学液体对材料进行腐蚀。与湿法腐蚀相比,干法刻蚀具有各向异性、精度高、危险性低、均匀性好等优点,更适合小线宽器件制作,成为目前主流的刻蚀方式[1-4]。

氮化硅薄膜具有良好的化学稳定性、绝缘性及优良的光学特性,在微电子工业和太阳能电池等诸多领域有着广泛的应用[5]。尤其是在硅基光电探测器领域中,氮化硅薄膜作为器件的减反射膜具有重要的作用。典型光电探测器结构中,氮化硅下层生长着氧化层,目的是在氮化硅刻蚀工艺过程中避免对硅的刻蚀损伤。如果在氮化硅刻蚀工艺中对硅衬底有刻蚀损伤,会造成器件暗电流增大[6-7]。因此要求氮化硅刻蚀工艺中氮化硅对二氧化硅具有较高的刻蚀选择比,确保不损伤硅衬底。影响刻蚀选择比的因素主要有射频功率、反应气体流量、腔内压强等几个参数。实验采用等离子体刻蚀机在不同工艺条件下对氮化硅进行刻蚀,从氮化硅与二氧化硅的刻蚀速率、氮化硅对二氧化硅的选择比两个方面进行分析,根据结果优化刻蚀工艺条件,得到了氮化硅对氧化层刻蚀选择比达到15∶1的刻蚀工艺。

1 等离子体刻蚀原理

等离子体刻蚀是通过化学作用或者物理作用,或者化学和物理的共同作用来实现的。反应腔室内的气体辉光放电,产生包括离子、电子及游离基等活性物质的等离子体,通过扩散作用吸附到介质表面,与介质表面原子发生化学反应,形成挥发性物质。同时高能离子在一定压力下对介质表面进行物理轰击和刻蚀,去除再沉积的反应产物和聚合物。通过化学和物理的共同作用来完成对介质层的刻蚀[8-10]。

实验所用材料为单晶硅片,依次生长17 厚度的二氧化硅及130 厚度的氮化硅。刻蚀设备为等离子体刻蚀机。刻蚀气体采用CF4,CH3F和O2。工艺采用二步刻蚀,主刻蚀和过刻蚀,主刻蚀保证大部分氮化硅被刻蚀掉,过刻蚀步骤刻蚀剩余的氮化硅。刻蚀氮化硅和二氧化硅的主要化学反应如下[11-12]

(1)

(2)

F*+H*→HF↑

(3)

Si+F*→SiF4↑

(4)

Si3N4+F*→SiF4↑+N2

(5)

SiO2+4F*→SiF4↑+O2

(6)

2 结果与分析

刻蚀气体采用CF4,CH3F和O2等刻蚀气体,通过改变气体流量比、腔内压强及射频功率来分析其对刻蚀速率及选择比的影响,根据实验结果优化过刻蚀步骤中氮化硅对二氧化硅的选择比。采用膜厚仪测试氮化硅与氧化层的前值与后值,计算两者的刻蚀速率与选择比。

2.1 气体流量比对刻蚀速率的影响

氮化硅和二氧化硅主要都是利用F*进行刻蚀。为了降低过刻蚀工艺中对氧化层的刻蚀速率,方法是通过保持F*气体流量不变,只调整氧气流量,来提高氮化硅对二氧化硅的刻蚀选择比。

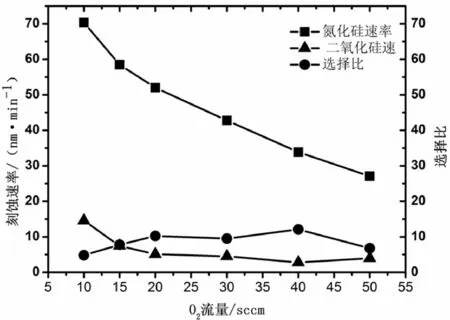

图1 氧气流量与氮化硅、氧化层刻蚀速率及选择比的关系

图1为在只改变氧气流量条件下,氮化硅刻蚀速率、二氧化硅刻蚀速率及选择比三者的变化趋势。其中CH3F流量为25 sccm保持不变。当氧气流量为10 sccm,氮化硅的刻蚀速率较快,这是因为CH3F的浓度较大,氧气的稀释作用不明显。随着O2流量的增大,其对整个气体氛围的稀释作用显著,所以氮化硅的刻蚀速率不断减小。氧气流量增加,会消耗CH3F中的C,而C含量减少,会减弱与氧化层中的氧反应,因此二氧化硅的刻蚀速率下降范围不是很大。在CH3F与O2流量比为25∶40时,氮化硅对氧化层的选择比最高,可以达到12.1∶1。

2.2 压强对刻蚀速率的影响

干法刻蚀由物理和化学两方面组成,物理刻蚀是离子对薄膜的溅射作用,溅射作用越强对介质的垂直刻蚀速率也就越快,剖面形貌越好。而溅射作用的强弱主要由腔内压强和射频功率决定。通过调节腔内压强来减弱溅射作用,降低氧化层的刻蚀速率。在CH3F和O2流量比为25∶40条件下改变过刻蚀步骤中腔内压强。具体变化趋势如图2所示。

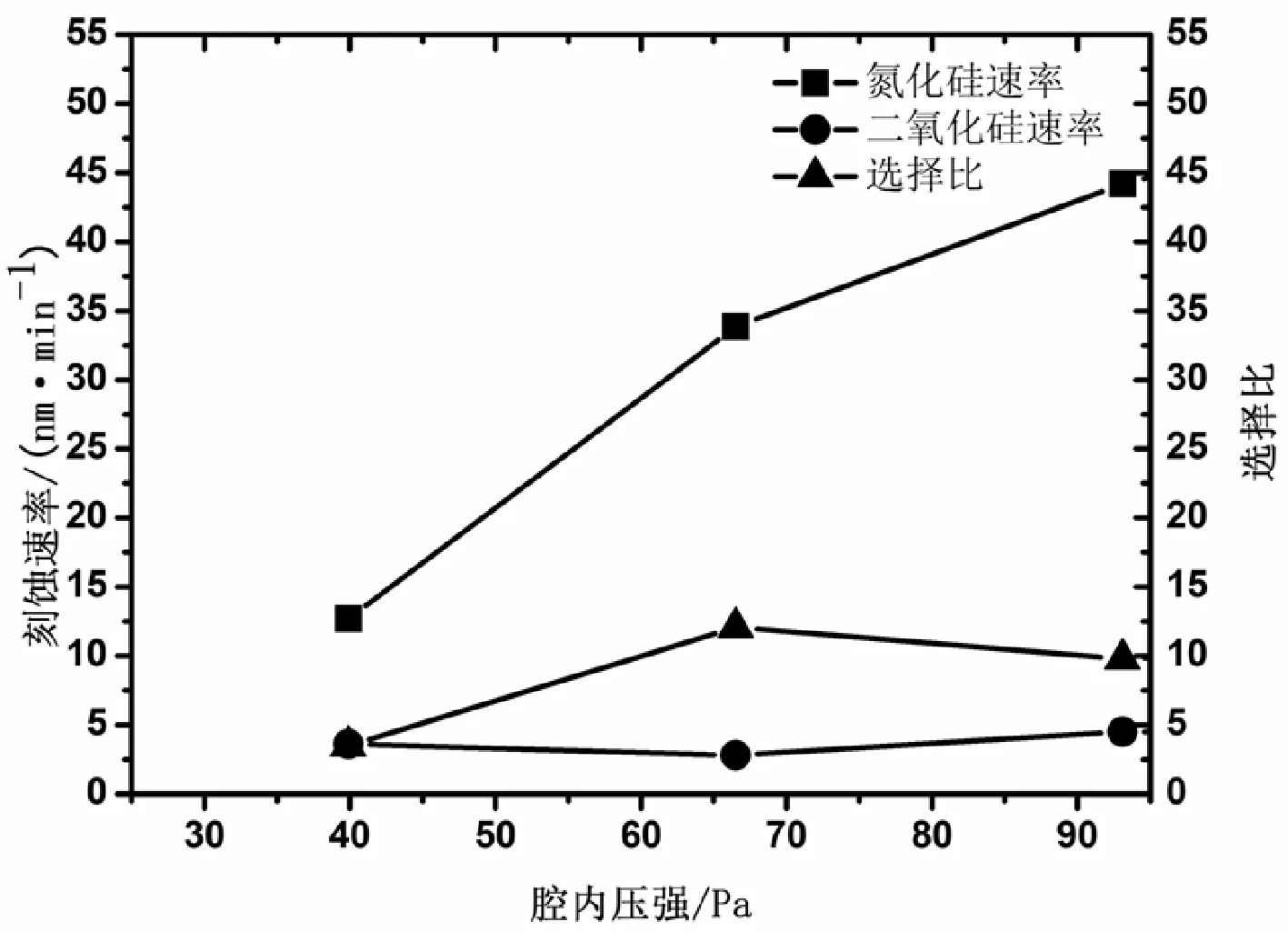

图2 腔内压强与氮化硅、氧化层刻蚀速率及选择比的关系

随着腔内压强的增大,参与反应的气体浓度上升,电离的F*增加,因此氮化硅的刻蚀速率增大。然而二氧化硅的刻蚀速率先降低后增大,降低可以理解为腔内压强增大,离子浓度增大而其自由程减少,离子间碰撞的概率增大,反应离子就会损失较多能量,进而速度减小,物理刻蚀作用减弱,导致氧化层的刻蚀速率减低。当腔内压强由67~120 Pa后,二氧化硅刻蚀速率开始增加,造成该现象的原因可以由式(7)得到,这是因为氧气消耗了部分C原子,使F*原子比例上升,导致对二氧化硅刻蚀速率增大[14]。而在腔内压强为67 Pa时,氮化硅对氧化层的选择比最高

(7)

2. 3 射频功率对刻蚀速率的影响

通过优化反应气体比例和腔内压强可以使氮化硅对二氧化硅的选择比达到12.1∶1。为获得更高的刻蚀选择比,改变射频功率来减少物理刻蚀作用,降低硅衬底损伤。

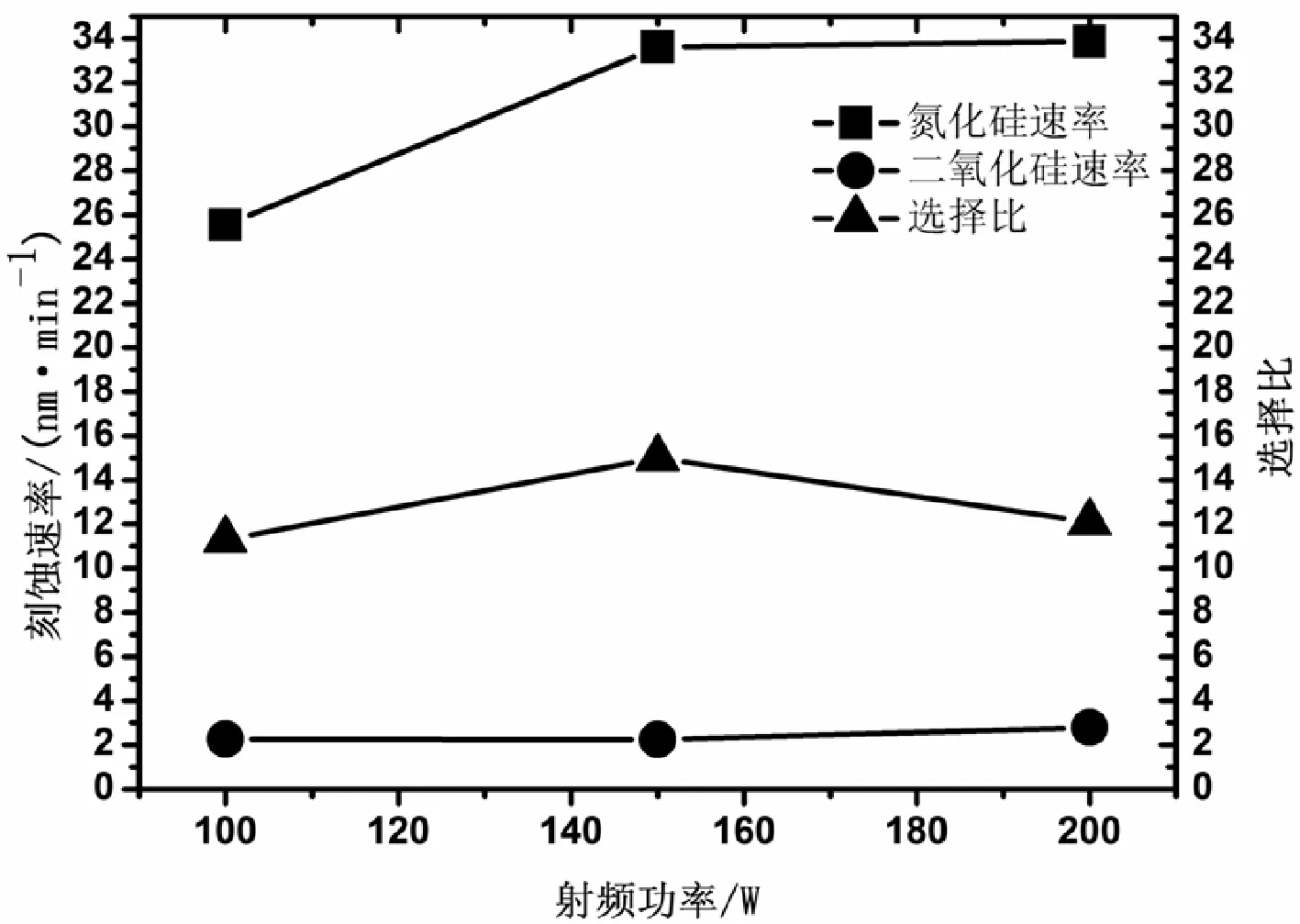

图3为改变射频功率后,刻蚀速率及选择比的变化趋势图。过刻蚀步骤中射频功率由100 W增加到200 W,氮化硅的刻蚀速率增大。这是由于增大射频功率,等离子体的浓度会增加,同时等离子体内自由电子的能量会变大,通过碰撞产生的自由基增多。因此物理和化学刻蚀作用都会相应的增大,导致刻蚀速率相应变大[15]。当射频功率>150 W后,氮化硅与二氧化硅刻蚀速率增加幅度减小,原因是功率增大,反应生成的聚合物增多,附着在介质表面,阻碍刻蚀作用,造成刻蚀速率变化不大。图3中二氧化硅的刻蚀速率在功率为150 W下最小,此时氮化硅对二氧化硅的选择比最高,可达15∶1。

图3 射频功率与氮化硅、氧化层刻蚀速率及选择比的关系

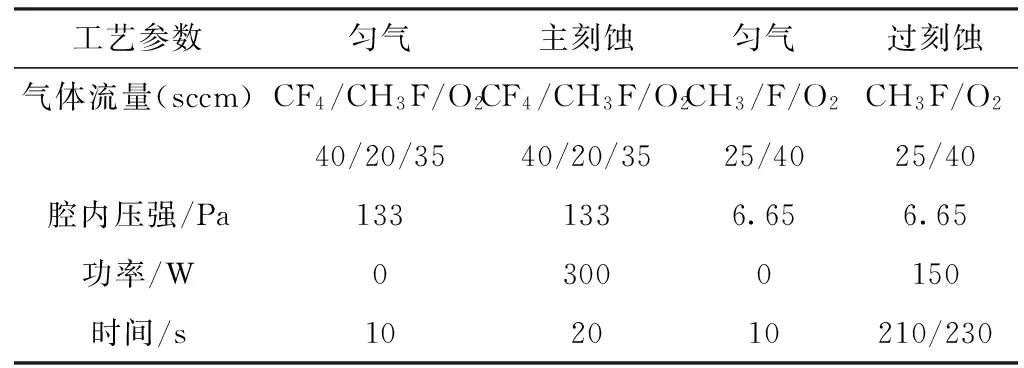

2.4 优化刻蚀菜单

通过调节过刻蚀步骤中气体流量、压强、功率可以使氮化硅对二氧化硅选择比达到15∶1。计算得到在主刻蚀时间为20 s,过刻蚀时间为180 s条件下,130 nm厚度的氮化硅可以刻蚀干净。为避免由于刻蚀均匀性导致的氮化硅残留,增加过刻蚀时间分别为210 s和230 s。刻蚀菜单如表1所示。

表1 氮化硅刻蚀菜单

刻蚀后经膜厚仪测试硅片上5点剩余氧化层厚度。具体数据如表2所示。

表2 膜厚仪测试数据

实验结果表明,主刻蚀时间为20 s,过刻蚀时间分别为210 s及230 s,刻蚀后剩余氧化层的厚度均值分别为9 nm及4.4 nm。与过刻蚀时间230 s相比,过刻蚀时间为210 s条件下刻蚀后剩余氧化层厚度均匀性更好,因此过刻蚀时间选择210 s。

3 结束语

采用CF4,CH3F和O2混合气体刻蚀氮化硅,分

析了不同流量比、压强和射频功率对氮化硅刻蚀速率、二氧化硅刻蚀速率及刻蚀选择比的影响。研究表明提高射频功率会增加刻蚀速率,但不利于刻蚀选择比的提高。适当增加氧气流量与腔内压强有助于提高氮化硅对氧化层的选择比,通过优化参数降低了过刻蚀对二氧化硅的刻蚀速率,最终得到氮化硅对二氧化硅15:1的刻蚀选择比,降低了氮化硅刻蚀工艺中硅衬底的损伤,提高了器件成品率。

[1] 杨光,苟君,李伟,等.二氧化硅的反应离子刻蚀工艺研究[J].微机处理,2012,33(3):1-3.

[2] 李元元.二氧化硅和光阻等离子刻蚀影响因素正交试验研究[D].天津:天津大学,2010.

[3] Abe H,Yoneda M,Fujiwara N.Developments of plasma etching technology for fabricating semiconductor devices[J].Japanese Journal of Application Physics,2008,47(3):1435-1455.

[4] 展明浩,宋同晶,皇华,等.基于ICP的硅高深宽比沟槽刻蚀技术[J].电子科技,2012,25(8):77-79.

[5] 赵毅红,陈荣发,刘伯实.Si3N4薄膜的成分与结构研究[J].真空,2004,41(4):71-73.

[6] 陈树华,武华,周弘毅,等.硅片表面粗糙度对界面态的影响[J].电子科技,2013,26(9):50-53.

[7] 李改灵.亚表面损伤预测模型的仿真分析与研究[J].军事交通学院报,2009,11(3):92-94.

[8] 斯蒂芬·A·坎贝尔.微电子制造科学原理与工程技术[M].2版.北京:电子工业出版社,2003.

[9] 杜文涛,曾志刚,胡志宇.氧化硅RIE刻蚀工艺研究[J].半导体光电,2014,35(1):1001-1008.

[10] 张锦,冯伯儒,杜春雷,等.反应离子刻蚀工艺因素研究[J].光电工程,1997(S1):47-52.

[11] Chang C Y,Sze S M.ULSI technology[M].NewYork:McGraw Hill Publication Services,Inc.,1996.

[12] 陈晓南,杨培林,庞宣明,等.等离子体刻蚀中工艺参数对刻蚀速率影响的研究[J].西安交通大学学报,2004,38(5):546-547.

[13] 高菁如.台阶覆盖工艺中0.6μm接触孔刻蚀形貌对ALSICU的填充效果的影响[D].上海:上海交通大学,2010.

[14] Michael Quirk,Julianserda.半导体制造工艺[M].韩郑生,译.北京:电子工业出版社,2006.

[15] Choudhary A,Cugat J,Pradeesh K,et al.Single mode rib waveguides in (Yb,Nb):RbTiOPO4 by reactive ion etching[J].Journal of Physics D:Application Physics,2013,46(14):108-145.

Study on Plasma Etching Process of Silicon Nitride

QU Pengcheng,TANG Daifei,XIANG Pengfei,YUAN Anbo

(Technology Center,Chongqing Institute of Optical-Electronics Technology,Chongqing 400060,China)

Etching silicon nitride process, which damage silicon substrate.The plasma etching for silicon nitride,was performed using CF4,CH3F and O2.By adjusting the gas flow ratio, chamber pressure and power, the three major parameters of silicon nitride etching rate,silicon dioxide etching rate and selectivity was researched. Under the condition of CH3F flow rate of 40 sccm, O2flow rate of 40 sccm,the pressure of 67 Pa and the power of 150 W,Experiments show that ,the silicon nitride etching process was obtained with the selectivity of 15∶1 and the uniformity of 3.87%.

silicon nitride; silicon dioxide; plasma etching; selectivity

2016- 10- 29

曲鹏程(1986-),男,硕士,工程师。研究方向:CCD与探测器工艺技术。

10.16180/j.cnki.issn1007-7820.2017.08.042

TN405.98+2

A

1007-7820(2017)08-153-03