卡诺图在数字电子技术课程中的应用

李金灿

(华南农业大学珠江学院,广东 广州 510900)

卡诺图在数字电子技术课程中的应用

李金灿

(华南农业大学珠江学院,广东 广州 510900)

卡诺图是数字电子技术课程一项重要的图形工具,它在逻辑函数化简方面要优于公式法.它能快速验证实验数据的准确性,为数据选择器实现逻辑函数提供直观的降维卡诺图,其次态卡诺图在时序逻辑电路设计中可以起到重要的桥梁作用.

卡诺图化简;降维卡诺图;次态卡诺图

1 引言

数字电子技术课程作为电气电子类专业一门重要的专业基础课,其教学目标是让学生通过系统的学习,能掌握基本原理,认识常用的逻辑芯片,并能设计出满足要求的逻辑电路.而卡诺图在整门课程中的地位是非常重要的,它典型用于逻辑函数的化简,亦可用于快速验证实验结果,还可用于组合逻辑电路如数据选择器的设计,及时序逻辑电路的设计[1].本文将通过实际的例子来叙述卡诺图在这几方面的应用.

2 卡诺图的应用

卡诺图(Karnaugh map)是由美国贝尔实验室电信工程师莫里斯·卡诺(Maurice Karnaugh)在1953年根据维奇图(Veitch diagram)改进而得到,在数字逻辑、故障诊断等许多领域广泛应用[2].卡诺图是逻辑函数一种用图形表示的描述方法,它可以与真值表、逻辑代数式、逻辑图、波形图等其它描述方法相互转换.

2.1 卡诺图在逻辑函数化简的应用

为减少逻辑电路使用的门电路数量或门输入端,需对逻辑函数进行化简,化简方法有公式法和图形法即卡诺图法.公式法化简比较快速,但需对常用公式非常熟悉.且某些逻辑函数在化简过程中,不能直观的判断结果是否为最简.而使用卡诺图化简[3],则可以直接得到最简结果.其缺点是对于变量个数超过4个的函数,卡诺图方格数将急剧增多,难以绘制.

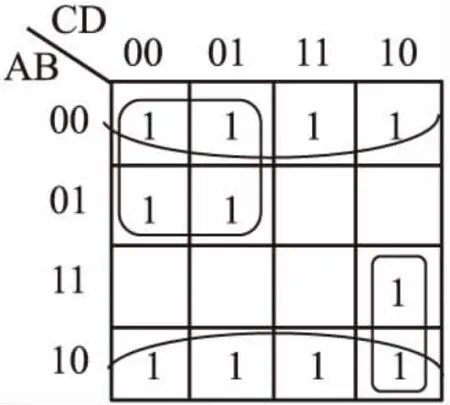

要使用卡诺图快速化简逻辑函数,必须掌握逻辑函数的卡诺图填入、画“卡诺圈”和与项求解.逻辑函数可分为标准和非标准与或式,对于标准式,可直接在卡诺图中相应的最小项方格填“1”即可.但对于非标准式,则需通过找出“交集方格”填“1”.如化简函数,该函数属于非标准式,要找出函数中每个“与项”的公共部分.因变量A、B负责卡诺图的行,变量C、D负责卡诺图的列,以为例,只需令“A=0,C=0”,“A=0”可找出第1、2行,“C=0”可找出第1、2列,它们交集为m0、m1、m4、m5,在相应的最小项方格填“1”即可.其它“与项”按相应的方法填入,如图1所示.

图1 卡诺图填入

接下来需画“卡诺圈”,即将卡诺图中所有为“1”的小方格用最少的圈数圈完.其合并规律有3个,(1)2个相邻的小方格可以合并,消去1个变量;(2)4个相邻的小方格可以合并,消去2个变量;(3)8个相邻的小方格可以合并,消去3个变量.这里涉及“相邻”的概念,是指“几何相邻”,包括相接、相对、相重合.在画圈时一般按“8个1→4个1→2个1→1个1”的顺序,画完后需对“卡诺圈”进行检验是否成立,其方法是检查圈内是否至少有一个从未被其它圈圈过的“1”.画完“卡诺圈”的卡诺图如图2所示:

图2 卡诺圈

最后将每个“卡诺圈”对应的“与项”写出再进行“相或”即可得到函数的最简与或式.大部分图书资料并没有将“与项”的获得方法写出,只是列举一些常见的“卡诺圈”及结果.作者根据多年的教学经验,归纳出方便快捷的方法:行看左边AB,列看上方CD;卡诺图内所有的“1”对应的变量取值不同,则将该变量去掉;对应的变量取值相同则保留该变量,变量取值为“1”时保留为原变量,为“0”时保留为反变量.

以卡诺图中“8个1”的卡诺圈为例,先看左边,上面“4个1”对应变量A取值为0,而下面“4个1”对应变量A取值为1,取值不同,去掉变量A;上下“4个1”对应变量B均取值为0,保留为反变量B.再看上方,4列“2个1”对应的变量C、D的取值均不相同,所以去掉变量C、D.该卡诺圈对应的与项是,与“8个相邻小方格合并消去3个变量”的化简规律是一致的.按同样的方法可以写出其它2个卡诺圈对应的与项是和,函数的化简结果为

2.2 卡诺图在实验过程中的应用

数字电子技术是一门对动手能力要求很高的课程,在理论课堂教学外,还需配套进行验证性和综合性实验.学生在实验过程中,往往只会按实验指导书给出的步骤搭建逻辑电路,并根据实验箱的显示状态记录实验数据,但对数据的正确性不能快速判断.

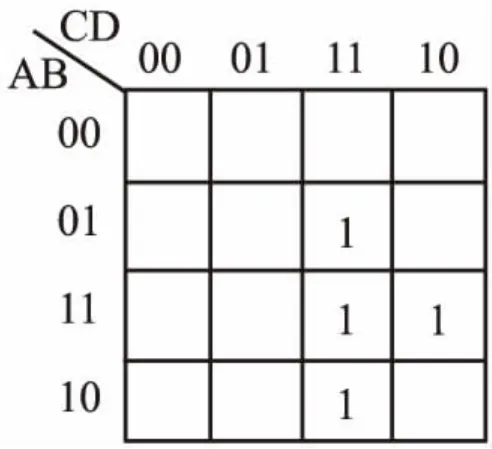

现以逻辑函数F(A,B,C,D)=ABC+ACD+BCD为例,要求用合适的逻辑芯片实现,并根据实验结果列出真值表进行验证.若直接对该函数式进行实现,需要2片三输入端或四输入端的与门和1片三输入端的或门.但若将函数式转换成与非-与非形式,即则只需使用2片三输入端或四输入端的与非门.搭建好电路便能很快得到该函数的真值表,学生一般会将16种的取值可能一一代入原函数进行验证,验证时间过长.若能巧妙使用卡诺图,便可快速验证.先将函数填入到卡诺图中,如图3所示:

图3 验证函数卡诺图

从卡诺图中立刻可以看出,当变量ABCD的取值组合为0111、1011、1110和1111这4种组合时,函数输出值为1,其余取值组合输出均为0.

2.3 卡诺图的降维应用

一般将卡诺图的变量数称为维数,如果把某些变量也作为卡诺图小方格的值,则会减少卡诺图的维数,这种卡诺图称为降维卡诺图[4].在使用数据选择器(MUX)实现组合逻辑函数时,教材一般只会介绍公式法,亦即拼凑法.拼凑法的关键是要分别列出数据选择器的输出端表达式和待求函数的标准与或式,然后将待求函数拼成与数据选择器输出表达的样式,通过对比,得出数据选择器地址输入端和数据输入端的值.当待求函数变量数是2-3个时,拼凑的过程不会很复杂,但若变量是4个时,则会变得很繁琐,对比过程容易出错.此时若引入图形法即降维卡诺图将会大大减少工作量.降维卡诺图一般适用于数据选择器地址端数少于待求函数变量数的情况.下面举例说明卡诺图如何降维,以及如何应用于函数实现过程.

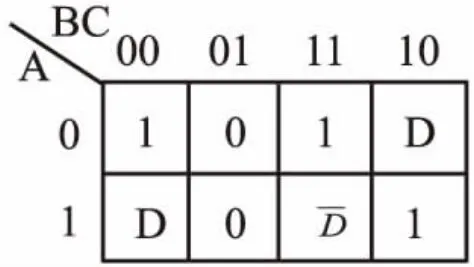

现使用八选一数据选择器74LS151来实现函数F(A,B,C,D)=∑m(0,1,5,6,7,9,12,13,14),因74LS151的地址端只有3个,而函数变量数有4个,所以需对函数降维.首先画出函数的卡诺图,如图4所示:

一般默认降变量“D”,可以先画出三变量“A,B,C”的空白卡诺图,根据原卡诺图的小方格取值即函数值来确定其值.降维可分成四种情况:

(1)当ABC取值为000时,当D=0,F=1;当D=1,F=1,不论D取值为0还是1,F都为1,所以在三变量卡诺图m0对应小方格填“1”.

(2)当ABC取值为001时,当D=0,F=0;当D=1,F=0,不论D取值为0还是1,F都为0,所以在三变量卡诺图m1对应小方格填“0”.

(3)当ABC取值为010时,当D=0,F=0;当D=1,F=1,F的取值与D的取值相同,所以在三变量卡诺图m2对应小方格填“D”.

(4)当ABC取值为111时,当D=0,F=1;当D=1,F=0,F的取值与D的取值相反,所以在三变量卡诺图m7对应小方格填“”.

图4 函数卡诺图

最后得函数的降维卡诺图,如图5所示.再将74LS151输出信号的卡诺图画出,如图6所示,通过两卡诺图对比,可以快速得出74LS151地址输入端A2A1A0和数据输入端D7-D0的值,之后便可画出74LS151的连线图,实现待求函数.

图5 降维卡诺图

图6 数据选择器卡诺图

2.4 次态卡诺图的应用

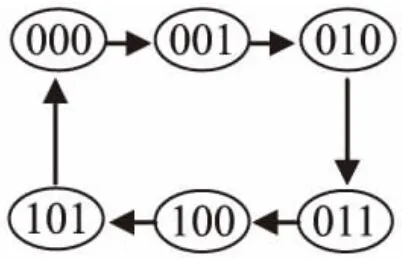

次态卡诺图是指卡诺图小方格填入的数据不是一个函数值,而是当前状态的下一个状态,一般是一组二进制数.在进行时序逻辑电路设计,需根据给定的条件,如状态转移图求解状态方程,此时需引入次态卡诺图,之后再将其拆分成各触发次态卡诺图来求解[5].现以设计一个同步六进制加法计数器为例,首先根据其计数规则,采用3个触发器实现,画出相应的状态转移图,如图7所示:

图7 状态转移图

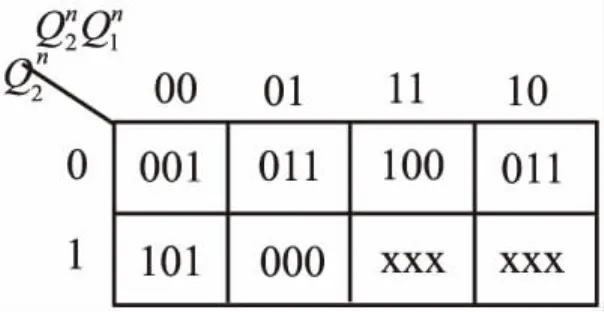

设图中状态圈内二进制数组合对应Q2Q1Q0状态,按箭头指向可以清晰的看出某一状态在输入信号作用下的下一个状态,即次态,可用次态卡诺图表示,如图8所示:

图8 次态卡诺图

将次态卡诺图中8个小方格中的二进制数组合分别取左、中、右各1个数字构成三个新的卡诺图,化简可得次态的表达式.再根据所选用触发器的类型,变换状态方程的形式,通过对比法可以求出触发器的驱动方程.

3 结语

上面叙述的4种情况基本是卡诺图在数字电子技术课程的全部应用,通过实例分析,可以快速掌握各种卡诺图应用的使用场合及方法.熟练使用卡诺图可加深对课程的理解,亦可加快逻辑电路的设计进度.

〔1〕余孟尝.数字电子技术基础简明教程[M].北京:高等教育出版社,2006.

〔2〕王芳.基于数字电路中卡诺图的应用研究[J].山西电子技术,2008(06):22-24.

〔3〕叶腾,朱桂英.卡诺图化简数学新方法[J].河北科技大学学报,2012,33(03):202-206.

〔4〕郝卜,张阳,柴毅哲,等.降维卡诺图在逻辑函数设计中的应用[J].降维卡诺图在逻辑函数设计中的应用,2012,25(04):33-36.

〔5〕任骏原.基于次态卡诺图的J、K激励函数最小化方法及时序逻辑电路自启动设计[J].浙江大学学报(理学版),2010,37(4):425-427.

G642

A

1673-260X(2017)08-0212-03

2017-05-06

2014年广东省质量工程项目《从化供电局校外实践教学基地建设》(4720);北方国际大学联盟第四期教育教学研究项目《EDA仿真软件在数字电子技术课程教学中的应用研究》(20140408002)