HKMG技术发展概况

王建霞+董乐

摘 要: HKMG技术在CMOS器件中有着广泛的应用,并支撑着45nm、32nm、28nm及以下工藝代的发展;本文重点介绍了HKMG技术的重要技术分支情况,并对HKMG在未来的走向进行了预测。

关键词: HKMG;CMOS;栅极漏电流;工艺代

The development situation of HKMG technology

Wang Jianxia,Dong Le(Equal to the first author)

(Patent Examination Cooperation Center of the Patent office,SIPO,Zhengzhou Henan, 450000)

Abstract:HKMG technology,which supports the development of 45-nm、32-nm、28-nm process and smaller-nm process,have been widely used in CMOS devices.The main technology branches of HKMG were emphatically analyzed,and the future trend was also forecasted in this paper.

Keywords:HKMG;CMOS;gate leakage current;process generation

1、引言

集成电路(IC)尤其是超大规模集成电路中的主要器件是金属氧化物半导体场效应晶体管(MOS),随着半导体集成电路工业技术日益的成熟,超大规模的集成电路的迅速发展,具有更高性能和更强功能的集成电路要求更大的元件密度,而且各个部件、元件之间或各个元件自身的尺寸、大小和空间也需要进一步缩小。

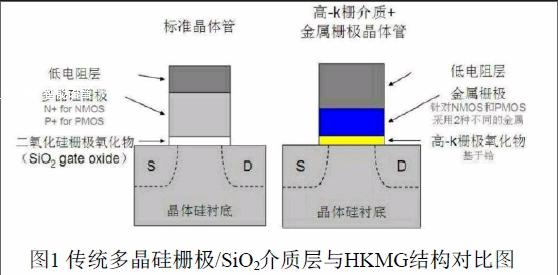

传统的栅极结构是多晶硅栅极/二氧化硅栅介质层,在进入亚微特征尺寸领域后,随着集成电路尺寸不断缩小,其中沟道长度和栅极氧化层厚度也在不断缩小,器件的物理极限对器件制备带来的影响越来越大,器件的特征尺寸按比例缩小也变得越来越困难。到了65nm工艺时,栅极氧化层达到了其物理极限,带来了高栅极漏电流、多晶硅耗尽损耗、硼穿透(掺杂硼原子扩散)等问题。上述问题严重影响着MOS晶体管器件的应用。

为解决上述问题,Intel率先于2007年在45nm工艺时启用了高介电常数金属栅极(HKMG,High-k/Metal Gate)技术[1],即采用基于金属铪(Hafnium)的氧化物作为栅极电介质,TiN替代传统的多晶硅栅极作为金属栅极。高k栅氧化层与金属栅极的组合使用,不仅能够大幅减小栅极漏电流,同时因高k栅氧化层的等效氧化物厚度(Equivalent Oxide Thickness,EOT)较薄,还能有效减低栅极电容。HKMG技术,有效支持由NMOS晶体管和PMOS晶体管共同构成的互补金属-氧化物-半导体(CMOS,complementary metal oxide semiconductor)场效应晶体管技术向28nm及以下技术代前进,并成为CMOS器件结构的新分水岭。

2、HKMG结构

所谓的高介电常数金属栅极(high-k metal gate,HKMG)技术就是采用具有高介电常数的材料(>20)替代传统的二氧化硅栅极氧化层作为栅极电介质,并采用金属替代多晶硅作为栅极材料。高k介质层必须满足以下条件:1、高介电常数,小于50nm的CMOS要求k>20;2、与Si有良好的热稳定性;3、在工艺处理过程中始终是非晶态,以减少泄漏电流;4、有大的带隙和高的势垒高度,以降低隧穿电流;5、具有低缺陷态密度,以抑制器件表面迁移率退化。最初发现满足这些条件的材料为基于金属铪的氧化物,如HfO2。但新材料的引入在带来希望的同时,也伴随着一定风险,基于铪的高k介质材料和原来作为栅极的多晶硅并不兼容。业内人员经过多次尝试发现,采用金属代替多晶硅作为栅极材料可进一步提高器件性能。

图1为传统的晶体管与具有HKMG结构的晶体管的对比图。与传统的多晶硅/二氧化硅栅介质层结构相比,HKMG技术不仅能够大幅减小栅极的漏电量,同时还能有效降低栅极电容。这样晶体管的关键尺寸得到进一步的缩小,其驱动能力也得到有效改善。HKMG技术的出现,使摩尔定律的神话得以延续。

3、HKMG工艺发展历程

在HKMG技术的工艺方面,存在以IBM为代表的先栅(gate-first)工艺和以Intel为代表的后栅(gate-last)工艺。本领域技术人员所公知的,MOS晶体管要通过离子注入在衬底中形成源漏区结构,之后进行高温退火对注入的离子进行激活。先栅工艺即是在进行源漏区离子注入及随后的退火步骤之前形成金属栅极,而后栅工艺是在源漏区离子注入及高温退火步骤之后形成金属栅极。

3.1 先栅工艺

先栅工艺也称前栅工艺,其与传统CMOS集成方案一致,工艺较为简单。如上图2为先栅工艺得到的HKMG的典型结构图[2]。如图2所示,该半导体结构即是通过先栅极HKMG工艺制成,栅极结构160分别包括高k栅介质层101,功函数金属层102(用于调整晶体管的阈值电压),金属栅极103,以及覆盖层Si3N4 105。形成栅极结构160之后,以栅极结构160为掩膜,通过离子注入在半导体衬底100中形成源漏区106,之后进行高温退火处理以对注入离子进行激活。先栅工艺中的高温退火工序会引起金属栅极的有效功函数改变,增加控制阈值电压的难度。这是先栅工艺中面临的最主要的问题。

为了满足高性能器件的技术要求,先栅工艺尝试了各种改进技术,如引入较为复杂的覆盖层(capping layer)技术,采用注入掺杂技术来调节有效功函数等,这些技术的引入不仅增加了工艺集成难度和工艺成本,而且仍无法满足器件进一步缩小后对阈值电压的要求。因此,业界内普遍认为先栅工艺可作为32nm或28nm技术代的过渡技术,但不具备进一步技术延伸的能力。

3.2 后栅工艺

为解决先栅工艺中离子注入、高温退火对金属栅极的影响,业内发展出了后栅工艺。后栅工艺又称替代栅(replacement metal gate,RMG)工艺,或牺牲栅工艺。即先在衬底上形成多晶硅虚设栅电极(dummy gate)结构,然后以虚设栅电极结构为掩膜进行源漏极区域离子注入以及高温退火,之后去除多晶硅虚设栅电极材料并进行金属栅极的沉积。因为金属栅极能够避免高温退火步骤,对制作金属栅极的金属材料要求更低,材料选择范围相对宽松,并可分别对PMOS和NMOS采用不同的金属电极,充分控制阈值电压Vt,功耗更低、漏电更少,高频运行状态也更稳定。虽然后栅工艺的工艺集成复杂,但业界己经公认后栅极技术具备可持续应用潜力,满足28nm及以下技术代、甚至新器件结构FinFET的技术要求。

后栅工艺先后发展出了两种工艺:先高k后栅极(high-k first gate-last)工艺和后高k后栅极(high-k last gate-last)工艺。

先高k后栅极工艺是先在衬底上形成高k栅氧化层和虚设栅电极,然后进行源/漏极的离子掺杂、高温退火等步骤,最后再刻蚀掉虚设栅极形成凹槽,采用合适的金属填充凹槽形成金属栅极。但在先高k后栅极工艺中,因高k栅介质层形成在高温退火之前,高温退火会对高k栅介质层的材料特性造成很大的影响,以至于器件的稳定性、迁移率在退火处理后显著恶化。

为了解决上述问题,业内又提出了后高k后栅极工艺,即高k栅介质层和金属栅极都在高温退火之后形成。后高k后栅极工艺使得高k栅介质层能避免高温退火,可改善器件的稳定性和迁移率[3],并也可进一步改善TDDB和NBTI效应。后栅极工艺虽能大幅提高CMOS器件性能,但因其工艺复杂,在其制作过程中存在一些技术难点。双金属电极的形成工艺是后栅极工艺中的难点之一,目前业内常用的两种工艺集成方案为金属反刻蚀技术和光刻胶保护技术,但这两种技术依然存在一些问题。吴世华等人提供了一种双金属电极的形成工艺,并减少工艺步骤,降低成本以及工艺集成难度,利于量产应用[4]。对于较先进节点栅极堆叠难于填充的问题,桑宁波等人提出了一种增加沟槽的开口的方法,使得后续的金属填充更易完成,同时降低接触电阻,且不影响虚拟栅下表面的宽度[5]。

4、HKMG面临的问题

无论是HKMG技术中的先栅工艺还是后栅工艺,对提升晶体管的性能均有重大的意义,但在工艺节点持续降低的发展中,HKMG技术也面临一些问题:如器件稳定性问题、界面态问题、费米钉扎效应等。

4.1器件稳定性

器件稳定性问题是HKMG技术中比较关键的问题,其主要体现在两个方面,一是偏压温度不稳定性(BTI,bias temperature instability),包括通常存在于NMOS器件中的正偏压温度不稳定性(PBTI,positive bias temperature instability)和存在于PMOS器件中的负偏压温度不稳定效应(NBTI,negative bias temperature instability);二是与时间相关的介质击穿(TDDB,time-dependent dielectric breakdown)。

4.2界面陷阱(interface traps)问题

CMOS器件的特性被HKMG中的各类陷阱所影响[6]-[7],在SiOx/Si界面的界面陷阱对超小晶体管的影响比大规模电路要严重得多。不同的HKMG制备工艺对出现在SiOx/Si界面处的随机界面陷阱(Random interface traps)有不同的影响,带有HKMG结构的鳍状场效应晶体管(FinFETs)在亚22nm工艺节点提高电学性能、控制各种波动等方面发挥着巨大的作用[8]-[9]。Sheng-CHia Hsu等人分析了RITs对16nm HKMG结构的体FinFET器件的影响,通过器件模拟,得出16nm HKMG结构的体FinFET器件能有效抑制由RITs引起的DC特性和SCE参数波动[10]。

4.3 费米钉扎效应(Fermi level pinning)

解决费米钉扎效应最好的方法是调节PMOS晶体管和NMOS晶体管的阈值电压,使得NMOS晶体管和PMOS晶体管的阈值电压对称并尽可能低。为了调节栅极整体的功函数,在高k介质层和金属栅极材料层之间引入功函数金属层。采用不同的功函数可调的金属分别作为PMOS晶体管和NMOS晶体管的功函数材料,以此调节PMOS晶体管和NMOS晶体管的功函数,并由此调节PMOS和NMOS晶体管的阈值电压。

PMOS晶体管中金属栅极的功函数范围需4.8~5.1eV,NMOS晶体管中金属栅极的功函数需位于4.0~4.3eV,但实际上PMOS晶体管的功函数偏低,在4.8eV左右浮动,无法达到更高的数值,其原因是作为金属栅极的Al原子扩散至功函数层、高k栅介质层,从而降低了金属栅极整体的功函数数值,其直接影响CMOS晶体管的性能。高汉杰[11]等公开了一种通过在功函数层上形成一扩散阻挡层并使其包裹住金属栅极材料层,从而避免基于金属原子扩散而导致金属栅极整体功函数下降的缺陷。报道称,在高k介质层与金属栅极之间设置阻挡层,也可帮助减少或消除多晶与高k之间的费米钉扎效应[12]。

HKMG中存在的上述主要問题,在一定的程度内影响着其应用发展,但也正是这些问题的存在,引领着HKMG行业内各研究人员采取各种技术手段,提升HKMG性能,并推动其向前发展。

5、HKMG的前景展望

2016年3月,全球半导体行业正式承认,自上世纪60年代起推动信息技术革命的原则——摩尔定律正走向终结,且全球半导体行业将发布以应用为导向的新路线图。该行业路线图将首次部署一份未以摩尔定律为中心的研发计划。相反,它将遵循“超越摩尔定律”的战略:以应用——智能手机、超级计算机、云数据中心——为开端,然后向下寻求所需芯片来支撑,而非让芯片变得更好并使应用跟随其后。从字面上理解,摩尔定律正在终结,因为晶体管数量的指数级增长已无法继续下去;不过从消费者角度来说,“用户价值每隔两年就会翻番”,从这层意义上说,摩尔定律将继续下去,只要半导体行业能持续用各种新功能填充其设备。

虽然HKMG技术已发展较为成熟,但就本文作者来看,其还未到达终点。半导体行业内持续对其结构、工艺各个方面的改进,该技术与其他器件集成的持续探索,以应用为导向的新路线图的战略部署等,将会继续使该技术支撑着半导体行业蜿蜒前行!■

参考文献

[1] K.Mistry et al. A 45nm Logic Technology with High-k+Metal gate Transistors, Strained Silicon, 9 Cu Interconnect Layers, 193nm Dry Patterning, and 100% Pb-free Packaging. IEEE Int Electron Dev Meet 2007 247-250

[2] S·弗莱克豪斯基,J·亨治尔,R·博施克,简化的先栅极HKMG制造流程,CN104517902A,2015.

[3]Takashi Ando, Eduard A. Cartier, Kisik Choi, Vijay Narayanan, Method to improve reliability of replacement gate device, US, US2015/0243762A1.

[4] 吴世华,尹英,一种双金属栅极的形成方法,中国,CN 105097473A.

[5] 桑宁波,李润领,关天鹏. 一种金属栅结构的形成方法,中国,CN104966668A,2015.

[6] Li Y, Cheng HW, Chiu YY, Yiu CY, Su HW: A unified 3D device simulation of random dopant, interface trap and work function fluctuations on high-K/metal gate device. In Proceedings of the IEEE International Electron Devices Meeting. Washington, DC: IEEE; 2011:107-110

[7] Tallarico AN, Cho M, Franco J, Ritzenthaler R, Togo M, Horiguchi N, Groeseneken G, Crupi F. Impact of the substrate orientation on CHC reliability in n-FinFETs—separation of the various contributions. IEEE Trans Device Mater Reliab 2014 14 52-56.

[8] Koh SM, Samudra GS, Yeo YC, Contact technology for strained nFinFETs with silicon-carbon source/drain stressors featuring sulfur implant and segregation. IEEE Trans Electron Devices 2012, 59:1046-1055.

[9] Chen SH, Liao WS, Yang HC, Wang SJ,Liaw YG, Wang H, Gu H, Wang MC, High-performance III-V MOSFET with nano-stacked high-K gate dielectric and 3D fin-shaped structure. Nanoscale Res Lett 2012, 7:431.

[10] Sheng-Chia Hsu and Yiming Li. Electrical characteristic fluctuation of 16-nm-gate High-K/metal gate bulk FinFET devices in the presence of random interface traps, Nanoscale Research Letters 2014, 9:633.

[11] 高漢杰, 赵杰,宋伟基.半导体器件及其形成方法,中国,CN104752179A,2015.

[12] 李达元;陈建豪;陈启群;叶明熙;李幸睿. 制造半导体装置的方法,中国,CN101752317 A,2010.

作者简介:王建霞(1986- ),女,博士研究生,助理研究员,研究方向:半导体器件的制备方法及设备; 董乐(1980- ),女,本科,主任科员,研究方向:计算机技术(等同于第一作者)