一种用于音频的2-2级联结构Sigma-Delta调制器设计

张 婷,钟传杰

(江南大学 物联网工程学院,江苏 无锡214122)

一种用于音频的2-2级联结构Sigma-Delta调制器设计

张 婷,钟传杰

(江南大学 物联网工程学院,江苏 无锡214122)

基于csmc0.35μm CMOS工艺,设计了一种用于音频设备的低功耗Sigma-Delta调制器,该调制器采用四阶噪声整形2-2级联结构实现,在获得高动态范围和高精度的同时更能够保证系统的稳定性。运算放大器采用两级全差分电路结构,仿真结果表明,运放的直流开环增益为90.9 dB,在3.3 V电源电压下,信号带宽为20 kHz,过采样率为64时,信噪比为101.45 dB,有效位数达到了16 bit,调制器功耗约为7.8 mW。

音频;低功耗;Sigma-Delta调制器;运算放大器

数字电路广泛应用于通信、视频等领域,而声音等自然界的信号均为模拟信号。因此作为连接模拟域与数字域的桥梁,模数转换器的性能对于集成电路的发展起着至关重要的作用。Sigma-Delta调制器借助于过采样技术和噪音整形技术,具有精度高、结构简单、对元件匹配要求低等优点[1],被广泛应用于便携式音频设备中。而保持高精度的同时降低系统功耗成为音频Sigma-Delta调制器设计的重点与难点[2]。

基于CSMC 0.35 μm CMOS工艺,设计了一款四阶噪声整形2-2级联结构的Sigma-Delta调制器,在Matlab Simulink平台下对调制器进行了系统结构设计,重点设计了运算放大器、带隙电压源以及一位量化器等电路模块,给出了调制器输出的仿真结果。

1 Sigma-Delta调制器系统结构设计

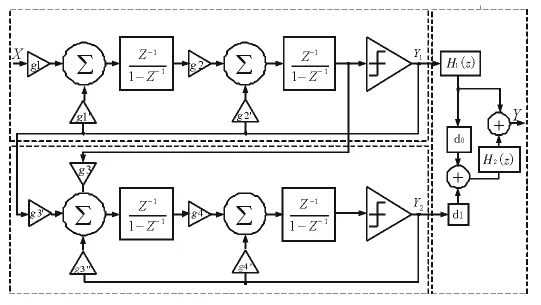

由于高阶单环结构的调制器系统不够稳定[4],本设计选取了四阶一位量化2-2级联结构的Sigma-Delta调制器,由两个稳定的二阶子调制器级联而成,因此可以确保整个级联结构的调制器系统是稳定的。系统结构由调制器和数字消除逻辑两部分组成,如图1所示。理想情况下,当增益衰减系数和传输函数满足表1的关系式时[5],调制器系统能够将第一级的量化噪声完全抵消掉,使得调制器的最终输出信号中只含有最后一级的量化噪声。

为了实现高精度和低功耗的设计目标,调制器结构的选择是至关重要的。由式(1)可知[3],理想情况下,当量化器的位数和过采样率一定时,调制器的阶数越高,系统达到的信噪比越大,精度越高。

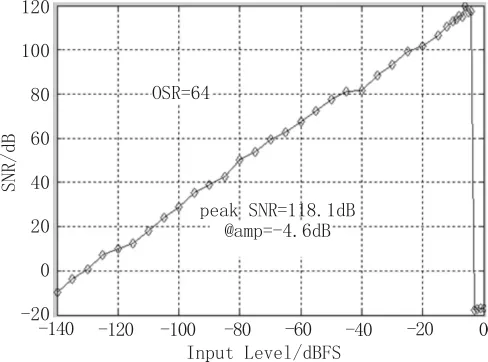

表1 2-2级联结构Sigma-Delta调制器系数关系表达式

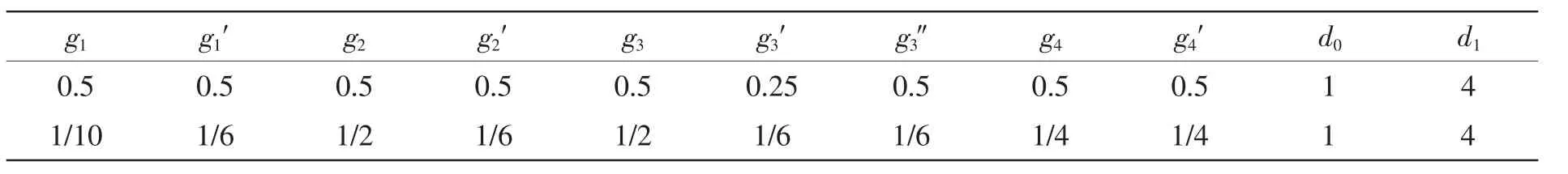

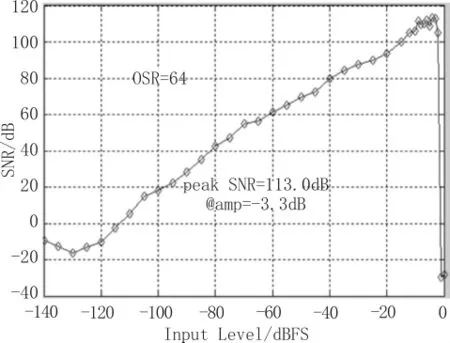

系统建模的主要目的是选取适当的系数使得调制器的性能得到优化。本设计基于Matlab Simulink平台,根据选定的2-2级联结构系统框图,构建了Sigma-Delta调制器的系统模型。表2所示的第一组增益衰减系数和反馈系数为大多数文献里提到的经典系数[6]。对于音频设备而言,调制器应当具有尽量大的输入动态范围[7]。在仿真的过程中发现,第一级积分器的增益衰减系数对于整个调制器的性能影响很大,适当减小g1的值能够达到增加输入摆幅的目的。根据表1列出的系数关系表达式,对于调制器的系数进行调整,得到了表2所示的第二组增益衰减和反馈系数。

图1 2-2级联结构调制器系统框图

表2 调制器传输系数

分别将两组系数代入系统模型之后进行仿真,得到如图2和图3所示的仿真结果。对比仿真结果发现,修改了系数之后的调制器模型输入电平的最大幅度有所降低,但是具有更大的动态范围,更能满足音频调制器的系统设计要求。

图2 经典系数调制器的动态输入范围

2 Sigma-Delta调制器电路级设计

2.1 运算放大器

图3 修改系数之后调制器的动态输入范围

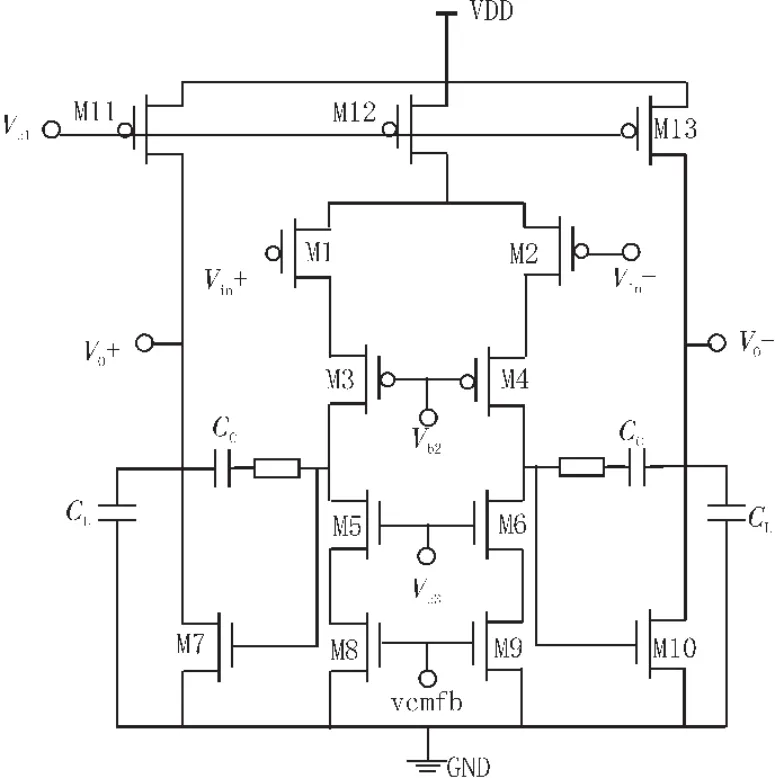

在Sigma-Delta调制器的设计中,第一级积分器的性能从很大程度上决定了调制器的性能[8],而积分器中最重要的组成部分便是运算放大器。由于设计的Sigma-Delta调制器应用于音频信号处理,对于转换速度的要求并不高[9],同时为了达到高增益低功耗的目的,本设计选择了两级全差分运放结构,电路如图4所示。为了进一步降低功耗,输入级选择了套筒式共源共栅结构。并且在运放第一级输出部分加上了共源放大器,达到增加信号输出摆幅的目的。

运放总的增益等于运放第一级的增益乘以运放第二级的增益:

图4 两级全差分结构运放

gm1表示输入级的跨导,gm2表示运放第二级的输入跨导。在两级运放之间增加米勒补偿电容,达到频率补偿的效果,从而降低输出极点对于运放性能的影响。米勒补偿电容给系统增加了一个处于右半平面的零点,与极点一样使系统变得很不稳定[10]。本文设计的两级全差分运放结构,通过在电路中放置一个调零电阻与米勒补偿电容相连接,将处于系统右半平面的零点移动到左半平面第二主极点所在的位置,保证了整个系统的稳定性。

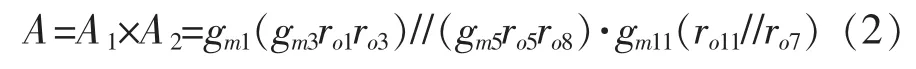

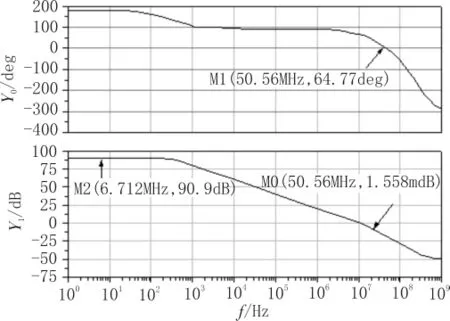

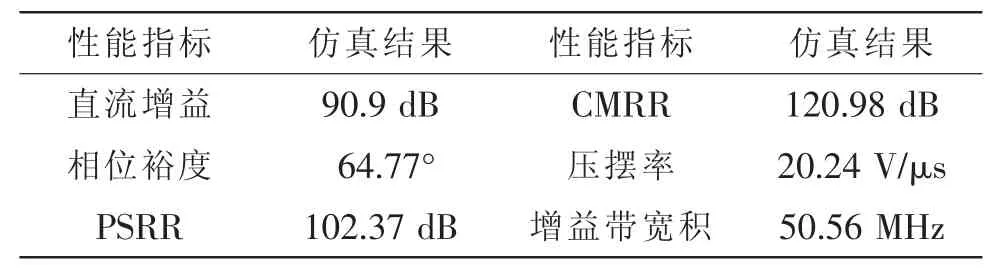

在cadencespectre下,仿真环境为:电源电压3.3V,温度27℃,第一级运放的仿真结果如图5所示。

图5 第一级运放的仿真结果

第一级运放的整体仿真结果如表3所示。

表3 运放仿真结果

2.2 带隙基准电压源

电压基准源是整个模拟电路设计中非常重要的模块,用来给电路的其他模块供应参考电压。基准源对于运放的增益和噪声都有显著影响,因此在高精度的模数转换器中,对基准源的稳定性和精度提出了更加严苛的要求。而温度系数以及电源电压抑制比成为衡量带隙基准源性能的主要指标[11]。

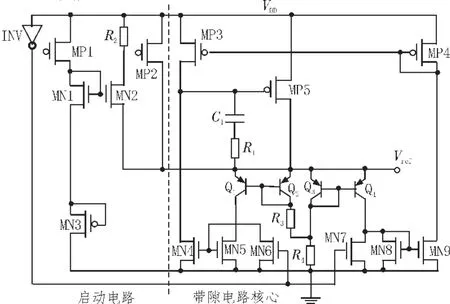

本设计选择的带隙基准电压源电路为带有自偏置电流镜的结构,如图6所示,包括启动电路和带隙核心电路。

图6 带隙基准电压源电路

MOS管MP5和电流镜构成了闭环负反馈的电路结构,用于电流补偿。双极型电流镜上的电流值提高时,MP3和MP4上的电流也跟着变大,导致MP5栅极上的电压提高,流过MP5的电流下降,使得双极型电流镜中的电流也跟着降低;如果双极型电流镜中的电流减小,那么MP5的作用便是提高双极型电流镜中的电流。与此同时,MP5与R3、R4一起组成了电压Vref采样负反馈电路,确保了基准源的输出电压Vref更加稳定[12]。调零电阻R1和补偿电容C1一起构成了RC电路,用于负反馈电路的频率补偿[13]。本设计选用的电路与传统带隙基准电压源电路相比,舍弃了运算放大器的运用,因此不受输入失调噪声以及电源抑制比的束缚。又因为深度负反馈从很大程度上增加了电源抑制比[14],所以自偏置电流镜结构带隙基准电压源电路的性能足以达到系统要求。

2.3 量化器

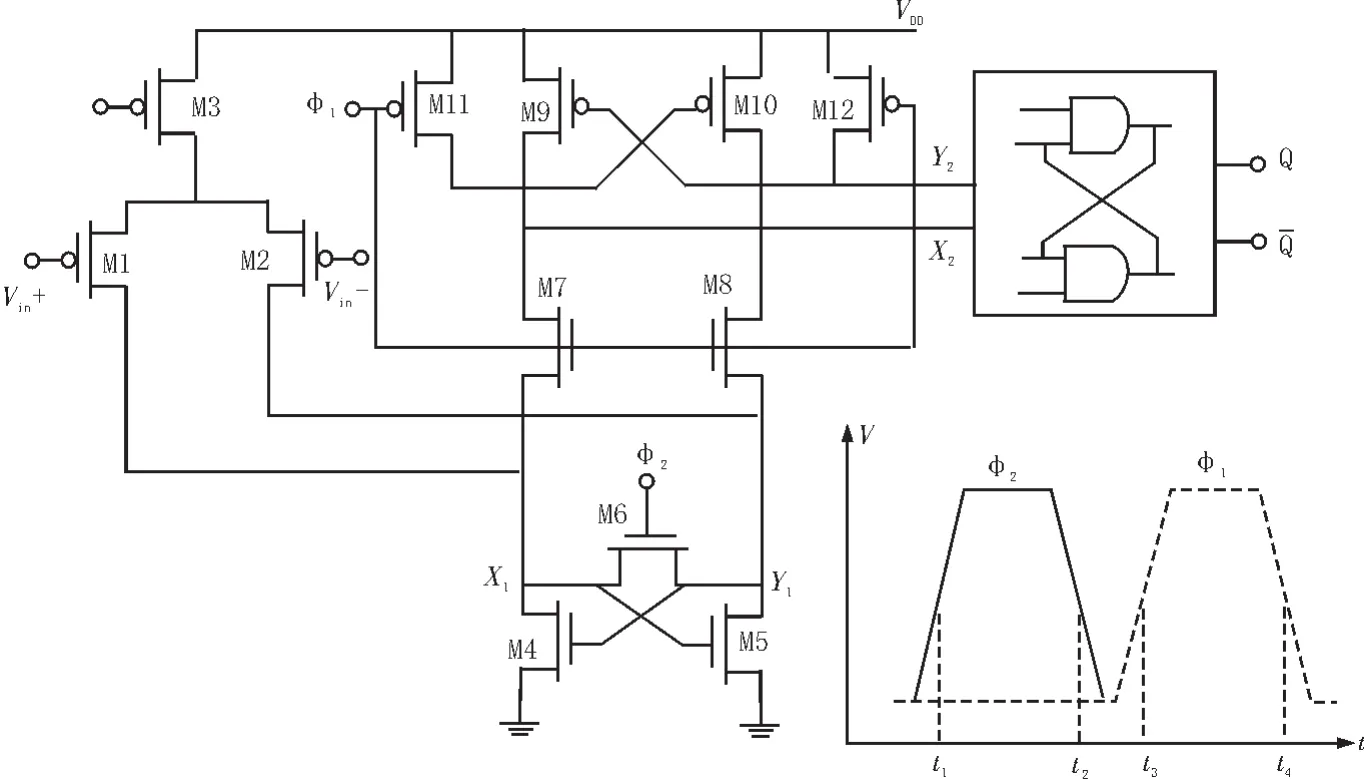

当量化器的位数大于1时,电路元器件间的不匹配性增加,从而容易给系统带来非线性误差[15],需要额外的辅助电路,增加电路的功耗。文中采用动态闩锁比较器实现调制器中的1 bit量化器,由输入级、闩锁级和触发器3个部分构成。该比较器工作速度快且功耗低,电路结构如图7所示。

图7 比较器电路原理图

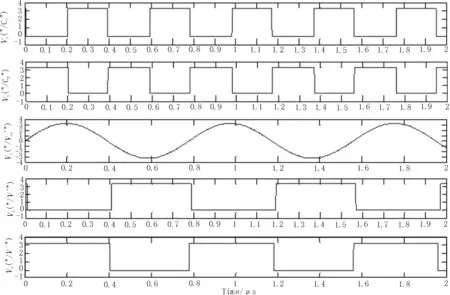

在cadence spectre下,仿真环境为:电源电压3.3 V,温度 27℃,C1,C2为两项非交叠时钟信号,周期为390 ns。比较器两端所加的激励信号为3.3sin(2π×1.28×106t)V。 仿真结果如图 8 所示。 从图中可以看出,动态闩锁比较器很好地实现了一位量化的功能。

图8 动态闩锁比较器瞬态仿真结果

3 调制器整体仿真结果

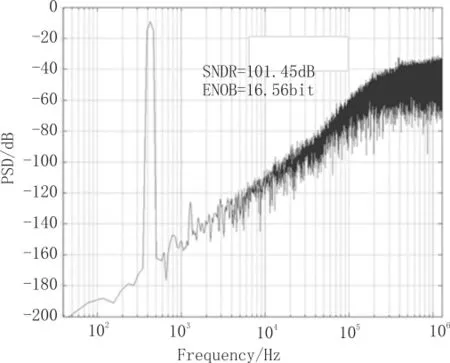

在Cadence软件下对调制器整体电路进行模数混合仿真,电路的仿真环境为:采用csmc0.35μm工艺,TT工艺角,温度为27℃。将仿真输出的数据导入Matlab中进行频谱分析,得到输出信号的功率谱曲线,如图9所示。从仿真结果分析可知,调制器的输出信噪比为101.45 dB,有效位数达到了16 bit,满足了高精度的设计要求。

图9 Sigma-Delta调制器整体仿真输出频谱图

4 结 论

文中设计了一个基于csms0.35 μm标准CMOS工艺的高精度Sigma-Delta调制器。调制器采用四阶2-2级联结构。为了降低调制器系统功耗,设计采用两级全差分结构的运算放大器。仿真结果表明,该调制器在3.3 V电源电压下实现了101.45 dB的信噪比,达到了16 bit的有效位数,整体功耗约为7.8 mW,可以用于高质量的音频设备中。

[1]YANG Shou-jun,TONG Zi-quan,JIANG Yuming.The design of a muti-bit sigma-delta ADC modulator[C]//International Conference on Measurement,Information and Control.Harbin:[s.n.],2013:280-283.

[2]Koli K,Kallioinen S,Jussila J,et al.A 900-MHz Direct Delta-Sigma Receiver in 65-nm CMOS[J].IEEE Solid-state circuits,2010,45 (12):2807-2810.

[3]Souri K,Chae Y,Makinwa K.A CMOS temperature sensor with a voltage-calibrated inaccuracy of±0.15℃(3σ)from-55 to 125℃[J].IEEE Journal Solid-State Circuits,2013,48(1):292-301.

[4]WU Hai-jun,Li Bin,ZHANG Hua-bin.A 1.2V power adaptable 95-to-67 dB DR 2-2 mash delta-sigma ADC with configurable OSR[C]//Electron Devices and Solid-State Circuits,Hong Kong,2013,12(1):1-2.

[5]Xie H L,Rakers P,Femandez R,et al.Single-Chip Multi-band SAW-less LTE WCDMA and EGPRS CMOS Receiver with Diversity[J].IEEE Radio Frequency Integrated Circuits Sympo-sium,2011,60(5):1-4.

[6]GE Bin-jie,WANG Xin-an,ZHANG Xing,et al.Sigma-delta modulator modelinganalysisand design[J].Semicond,2010,31(9):198-202.

[7]Agah A,Vleugels K,Griffin P B,et al.A highresolution low-power incremental Σ-Δ ADC with extended range for biosensor arrays[J].IEEE J Solid-State Circuits,2010,45(6):1099.

[8]GE Bin-jie,WANG Xin-an,ZHANG Xing,et al.Study and analysis of coefficient mismatch in MASH21 sigma-delta modulator[J].Semicond,2010,31(1):015007-1-4.

[9]Seo M W,Suh S H,Iida T,et al.A low-noise high intrascene dynamic range CMOS image sensor with a 12 to 19b variable-resolution columnparallel folding-integration/cyclic ADC[J].IEEE JournalofSolid-StateCircuits,2012,47(1):272-283.

[10]CAI Chen-yan,YANG Jiang,SUN Sai-weng,et al.A passive excess-loop-delay compensation technique for gm-C based continuous-time ΔΣ modulators[C]//Circuits and Systems(MWSCAS),2011 IEEE 54th International Midwest Symposium.Seoul,2011:1-4.

[11]Chae Y,Cheon J,Lim S,et al.A 2.1 M pixels,120 frame/s CMOS image sensor with columnparallel ADC arachitecture[J].IEEE Journal of Solid-State Circuits,2011,46(1):236-247.

[12]李亮,陈海珍.应用于数字音频的二阶Sigma-Delta调制器设计[J].微电子学与计算机,2010,27(7):198-201.

[13]Liang J,Johns D A.A frequency-scalable 15-bit incremental ADC for low power sensor applica-tion[C]//Proceeding ofInternationalSymposium on Circuits and Systems(ISCAS),IEEE,2010:2418-2412.

[14]Shin S K,Rudell J C,Daly D C,et al.A12bit 200MS/s zero-crossing-based pipelined ADC with earlySub-ADC decision and outputresidue background calibration[J].IEEE Journal of Solid-State Circuits,2014,49(6):1366-1382.

[15]Shafti A,Yavari M.A zero-crossing based 10 bit 100MS/s pipeline ADC with controlled current in 90 nm CMOS[J].Analog Integrated Circuits and Signal Processing,2014,80(1):141-145.

A 2-2 mash Sigma-Delta modulator design for audio application

ZHANG Ting,ZHONG Chuan-jie

(School of Internet of Things Engineering,Jiangnan University,Wuxi 214122,China)

In this paper,A low-power 2-2 multi stage noise shaping (MASH) Sigma-Delta analog to digital modulator for audio application is implemented.The design was fabricated in a 0.35 μm CMOS process.In order to reduce power consumption,fully differential two stage operational amplifiers are used.The simulation shows that the DC open loop gain is up to 90.9 dB.When the power is 3.3 V and OSR is 64,the simulation results show that SNDR of the modular can reach 101.45 dB,while the power consumption is merely 7.8 mW.

audio; low power consumption; Sigma-Delta modulator;operational amplifier

TN47

A

1674-6236(2017)17-0124-05

2016-07-22稿件编号:201607162

张 婷(1990—),女,江苏宿迁人,硕士研究生。研究方向:集成电路设计。