基于多核DSP信号处理机关键技术研究

钟佰志+韩霄

摘要:日益复杂的电磁环境要求雷达具备抗干扰的能力,抗干扰手段通常在信号处理过程中实施。应对复杂的信号处理,需要高性能的雷达信号处理机,评价其性能的两个重要指标是信号处理能力和数据传输能力。TMS320C6678是TI公司新型浮点数字信号处理器(DSP),片内集成8个C66x+内核,单核主频高达1.25GHz。一片DSP单精度浮点并行运算能力理论上可达160G Flops,被广泛应用于雷达信号处理机中。

关键词:雷达;抗干扰;信号处理机;DSP

中图分类号:TN492 文献标识码:A 文章编号:1007-9416(2017)05-0050-02

1 前言

现代雷达为应对电磁干扰,增加了信号处理流程,使信号处理更为复杂化。此过程的实现需要高性能的雷达信号处理机做支持。作为信号处理机的核心,处理器(PowerPC、DSP)的主频越来越高,如今已经跨过了GHz的门槛,精简指令集的使用极大提升了处理器的性能,但是这依然难以满足雷达信号处理的需求。随着处理器主频的提升,对制造工艺的要求更加苛刻,生产难度加大,同时成本也大幅度提升。面对这样的瓶颈,芯片厂商选择由单核单线程向多核多线程的方向转变。TMS320C6678是TI公司推出的一款基于KEYSTONE架构的高性能浮点/定点DSP,片内集成8个C66x+核。每个核的主频最高可达1.25 GHz,其进行定点和浮点运算的能力分别为40G Macs和20G Flops,被广泛应用于雷达、声呐、卫星系统、医疗成像等对定浮点运算能力和实时性有较高要求工程领域中。

2 信号处理机架构

雷达信号处理机包括AD采集板,预处理板,主处理板,主控板等,通过高速AD采集接收机发送的中频信号,经过FPGA脉压后数据送到DSP进行相关运算。FPGA将有效数据重排后,根据不同任务类型进行打包,并通过SRIO接口发送到DSP。DSP会根据预先设置的路由系统分别跳转到相应的ISR,进行数据处理。由于数据间的耦合性以及对实时性的要求,需要核间通信(IPC)来保证同步性能。经过需求分析,提出图1所示信号处理机架构。该方案需解决2个技术难题,即SRIO接口互联以及核间通信(IPC),本文主要围绕这两项技术展开研究。

随着雷达通道数的增加,数据量也随之加大,为了减轻处理器内核的压力,数据缓存工作由EDMA负责。为解决数据存储问题,采用通过DSP的DDR控制器扩展8GB DDR3,用于进行FFT、高阶复数矩阵运算等。预设数据存储在DSP外挂的NOR FLASH中,DSP通过SPI接口进行数据访问。为实现上电BOOTLOAD,将应用程序镜像固化到NAND FLASH中,通过配置DSP启动项为EMIF引导方式,实现上电自举。

3 关键技术研究

决定一个数字信号处理系统运算能力的两个重要指标为:一是信号处理能力,指系统中总的可用处理资源,在多核处理器中主要体现在核间通信方面;二是数据传输能力,指板内片间、板间的数据链路能提供的最大带宽。下面将对这两项重要技术做具体分析。

3.1 高速数据互联

Serial Rapid IO(SRIO)是一种开放的、高带宽系统级通信标准,类似于以太网,基于包交换格式,能为片间或板间通信提供吉比特每秒的数据带宽。该通信协议被广泛应用于网络设备、存储器子系统、通用计算机中的微处理器、存储器、存储器映射I/O之间的互联。目前SRIO标准已发展到第二代,数据率支持5G bps和6.25G bps。RapidIO協议规范包括逻辑层、传输层和物理层,如图2所示。顶层为逻辑层,离用户最近,提供面向用户接口;居中为传输层,记录了系统内路由信息,传输端点地址等;底层为物理层,包含设备级接口信息,如电气特性、纠错管理等。这种多层传输机制能够保证数据传输的安全性、完整性,通过采用逐层向上打包的方式,使传输包具有丰富的校对信息,又不影响有效载荷比率,同时为协议的扩充提供了结构基石。扩展协议时只需在相应层中进行添加协议规范而不改变其他层级结构,扩展方式更为灵活。

SRIO协议的逻辑层定义了操作协议和相应的包格式,其支持的逻辑层业务主要是DirectIO(DIO)和消息传递(Message Passing)。DIO模式是最简单实用的传输方式,其实现的前提是主设备知道被访问端的存储器映射。消息传递模式类似于以太网,数据在被访问设备中的位置则由邮箱号确定。

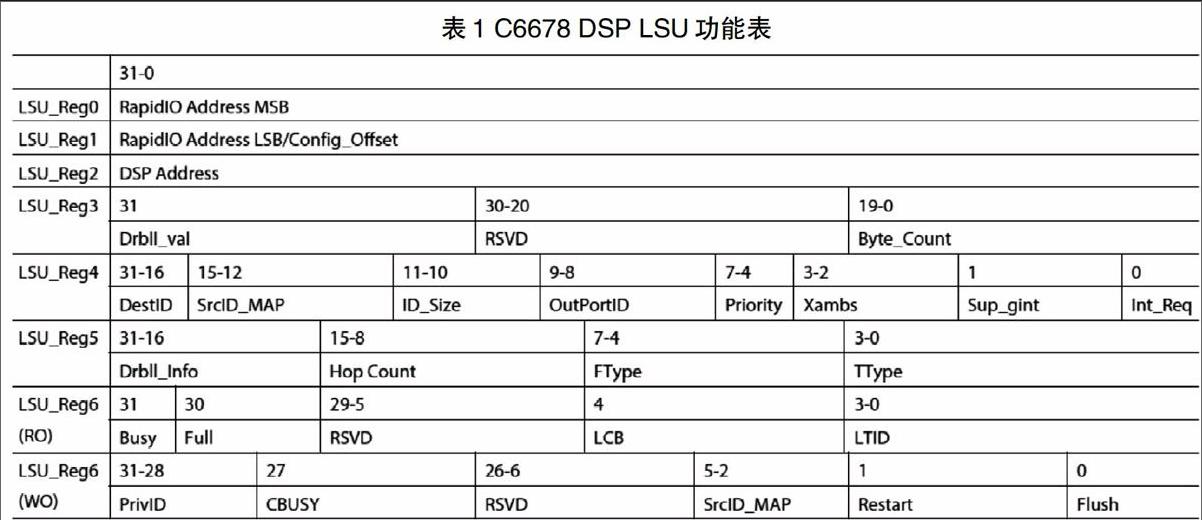

本文采用DirectIO模式,此模式包括NWRITE、NWRITE_R、SWRITE、NREAD等传输方式,其中 NWRITE 和NREAD为对应模式,可以直接向从设备内存写读数据,不要求接收端响应,每个数据包最大数据量为256 Bytes。DIO模式通常需要传输两种事务,即DIO包和DOORBELL包。其中DIO包为数据包,主要传输有效载荷。门铃包为消息包,相当于网络内端点间的握手信号。DSP的SRIO接口传输控制通过Load/Store Unit(LSU)控制单元实现。DSP中LSU单元是一系列寄存器,Master DSP要想通过SRIO访问Slave DSP的内存数据,需要配置LSU寄存器,数据打包过程由硬件实现。LSU寄存器功能见表1。

3.2 核间通信

传统的单板多片DSP之间通常采用McBSP菊花链进行数据互传,采用FPGA同步各片DSP,该方法效率低,而且容易出现总线竞争现象。多核DSP具备核间资源共享,总线仲裁等机制,性能明显优于单板多片DSP架构。C6678 DSP为解决该问题在片内建立了Inter-Processor Communication(IPC)机制,每个核能够通过内部中断的方式同其他核进行核间同步。通过在软件中设置触发条件,能够对任意一个核的中断标志寄存器进行置位。

IPC中断默认对应91号事件,通过中断通道选择器可以绑定到INT4~INT15任意一个中断上。首先需要配置中断向量表,根据系统内可屏蔽中断数量和优先级规划出IPC中断服务函数入口,通过映射IPC事件到指定的物理中断号,并使能相应中断。DSP有两组核间通信寄存器,中断生成寄存器IPCGR和中断确认寄存器IPCAR,每组有8个32位的寄存器。通过向某个核对应的IPCGR末位写1,即可触发该核IPC中断,IPCGR中4~31位为中断信源信息,最多可以容纳28个中断源。当中断发生后,信源信息会同步到IPCAR中的对应位置,目标核通过检测该信息判断信主身份,并将当前正在执行的程序挂起,由硬件保护现场,根据绑定的中断地址跳转到中断服务程序。当中断被响应后要及时清除中断确认寄存器(SRCC)中的状态位,以便接收下一次中断请求,清除方法是将对应的SRCC位置写1即可。为了避免多个核同时对某个核的IPCGR进行数据写入,DSP建立了防竞争机制,设置了KICK0和KICK1两个防陷阱寄存器,在进行中断触发前需要先解锁这两个寄存器才能向IPCGR中写入数据。

4 结语

本文围绕多核DSP + FPGA架构的信号处理机开展研究,信号处理过程需要解决两个关键技术,即高速数据传输以及核间通信。文中对这两项技术进行了原理研究,并针对硬件平台进行了实验验证。实验结果表明该架构信号处理机能够满足海量数据传输和并行数据处理的要求,为复杂的雷达信号处理提供计算平台,尤其在日益恶劣的电磁环境下,这种雷达信号处理机能够有效地实现抗干扰等复杂运算。

参考文献

[1]牛金海.TMS320C66x KeyStone架构多核DSP入门与实例精解[M].上海:上海交通大学出版社,2014:155-160.

[2]Texas Instruments.TMS320C66x DSP CorePac User Guide[J].USA:Texas,2011:21-26.

[3]马友科,宋万杰,吴顺君,等.基于多DSP 的雷达阵列信号处理系统[J].雷达科学与技术,2009,7(2):115-118.endprint