基于IEEE1588v2的时间同步模块设计

陈子龙

(第七一五研究所,杭州,310023)

基于IEEE1588v2的时间同步模块设计

陈子龙

(第七一五研究所,杭州,310023)

以FPGA为核心芯片,基于IEEE1588v2协议,设计了一种时间同步模块。该模块以GPS或本地时间为基准,按IEEE1588v2协议,在以太网物理层和MAC层之间的MII处检测和标记IEEE1588报文,实现高精度时间同步。测试结果显示该同步模块误差小于300 ns,可以用于多台声呐设备间基阵信号的同步采集或声呐系统的网络授时等工作场合。

声呐;基阵信号;时间同步;IEEE1588v2;GPS;FPGA

声呐信号处理中,空间处理器的目的是利用信号和干扰噪声之间在空间特性上的差异,把弱信号从干扰背景中提取出来。信号可认为是远场的平面波,而干扰噪声却是各个方向射入平面波声场的线性叠加。信号和干扰噪声的这种不同空间特性,使我们可以利用基阵对声场进行空间处理,获得空间处理增益。为了得到较为理想的空间增益,必须做到各阵元精确定位。声呐前置预处理机中,有明确的多通道间相位一致性的要求[1]。影响基阵信号相位精度的因素有放大电路、滤波电路的相位不一致性和模数转换电路工作的采样偏差等。为了尽可能减小采样偏差,在声呐基阵信号采集中常用多路信号同步采集技术。

在大型声呐设备的基阵信号采集电路中,同步信号直接送到应用层,即同步采集端,避开了以太网底层对时间信息的延时[2]。这种架构破坏了开放系统互联 (Open System Interconnect,OSI)的分层思想,适合局部范围应用。美国电气和电子工程师协会(Institute of Electrical and Electronics Engineers,IEEE)推出的精确时间协议(Precision Time Protocol,PTP)技术,即 IEEE1588,全名“网络测量和控制系统的精密时钟同步协议标准”。该协议采用时间戳机制和主从时钟方案,对时间信息进行编码传送,利用网络链路的对称性和延时测量技术[3],实现主从时钟频率、相位的高度同步。

本文基于IEEE-1588v2协议,利用FPGA实现了一种时间同步模块。该模块通过NMEA-0813标准解析GPS报文,也可以解析本地时间,为网络终端提供秒脉冲信号作为授时信号。

1 基于IEEE-1588v2和GPS的时钟同步原理

基于 IEEE-1588v2和 GPS的同步原理如图1所示,分布式系统根据地理位置等因素分为若干个子网,子网内部拥有一个主时钟节点与若干个从时钟。基于 IEEE-1588v2协议的主时钟通过支持IEEE-1588v2协议的交换机对网络中所有从时钟进行同步,各子网之间的主时钟通过GPS实现同步。该方案能够解决从时钟设备没有条件接收 GPS时间信号的等场合,通过IEEE-1588v2协议达到各从设备的时间同步。如果主时钟设备没有条件获取GPS时间信息,则主时钟模块可以以本地时间信息作为基准,做到各从设备跟主设备之间的时间精确同步。主时钟设备间则无法获得时间同步。

图1 基于IEEE1588v2和GPS的分布式同步网络

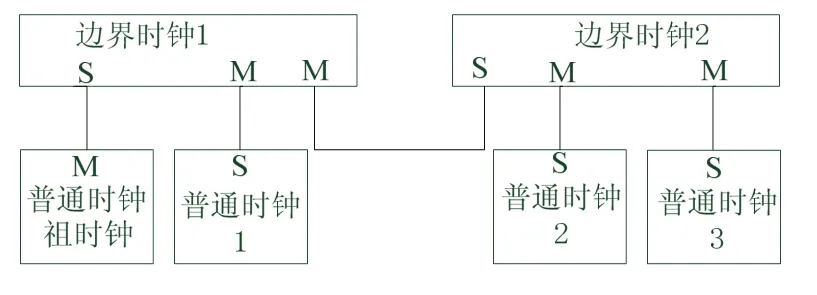

IEEE1588v2标准规定了将分散在测量和控制系统内的分离节点上独立运行的时钟,同步到一个高精度和标准度的协议。其网络拓扑如图2所示,网络由主参考时钟(GrandmasterClock)、边界时钟(BoundaryClock)和普通时钟(OrdinaryClock)构成,通过主钟与从钟协议通信的方式完成时钟同步。

图2 IEEE1588时钟系统结构

2 时间同步模块设计

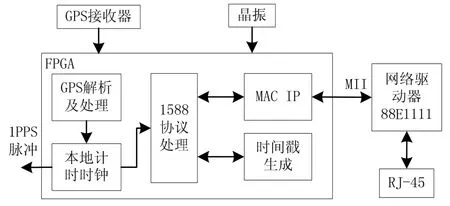

如图3所示,时间同步模块主要由FPGA、GPS接收器、网络驱动器88E1111、RJ_45、恒温晶振等构成。时间同步模块在FPGA中完成GPS解析及处理、控制1588同步过程的功能,并用GPS同步信号作为同步源校正本地时钟;在以太网链路MII处检测和标记同步报文,实现基于以太网的 1588同步;提供PPS脉冲做为授时信号。通过FPGA内部逻辑实现 1588 协议栈的高层(应用层、传输层和网络层),数据链路层通过开源MAC和自定义代码的方式实现,物理层使用88E1111实现。

图3 时间同步模块功能框图

2.1 GPS信号接收与解析

时间同步模块依据 NMEA-0813 标准格式解析$GPZDA 报文,语法格式见图4。图中,解析时、分、秒数据,对本地时钟进行对时,同时利用GPS的 PPS脉冲将本地时钟的计数器清零。在使用GPS_PPS脉冲之前需要首先判断 GPS 接收机锁星是否正常,大于3颗为正常,若锁星异常,则不使用GPS秒脉冲,而选择 FPGA 生成PPS脉冲[4];其次需要对GPS秒脉冲进行抗干扰处理[5],以避免干扰产生的伪PPS脉冲可能导致的错误对时。

图4 GPS报文格式

2.2 基于1588v2的同步实现

FPGA通过 MII 接口与以太网收发器88E1111相连,通过内部逻辑检测和标记同步报文。如图5所示,IEEE-1588v2协议规定,同步报文的时间戳产生时刻为:帧开始标志字节最后一位的结束和MAC目的地址第一个字节的第一位到来之前的间隙,时间戳在输出帧和输入帧都进行标记。

图5 同步报文时间戳标记时刻

FPGA内部逻辑中采用开源MAC IP和自定义逻辑的方式实现IEEE1588协议报文的检测:从帧开始标志结束后[6],检测报文数据流中的 MAC 地址、报文类型和 UDP 端口号,符合协议规定则被视作同步报文。FPGA的协议处理部分采用了IEEE-1588v2中的透明时钟模型和点对点延迟请求消息模式。点对点延迟请求是一种新的、专门用于测量两个端口间平均网路延迟时间的独立消息模式,这种模式可以测量同步系统中任意两点之间的平均延迟时间,而且可以在任意时刻进行任意次的测量。透明时钟模型的建立使得网络节点对 IEEE-1588事件信息包的处理变得简单、易于实现,降低了IEEE-1588协议的实施难度。IEEE1588同步系统通过主从设备间消息传递,计算时间和频率偏移,达到主从频率和时间同步,实现机制如图6所示。

图6 IEEE1588时间同步原理图

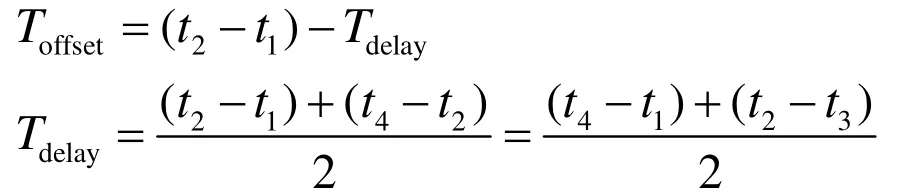

图6中,t1为主时钟发送同步报文的时间,t2为从时钟收到同步报文的时间,t3为从时钟发送延时请求报文的时间,t4为主时钟收到延时请求报文的时间。这里假定路径是对称的,即同步报文的收到延时与延时请求报文的发送延时相同。从时钟相对于主时钟的偏差Toffset和传输延时Tdelay计算公式为:

2.3 本地时钟实现方法

本地时钟的基准频率为50 MHz,由外部频率经FPGA内部PLL倍频获得。内部分别用两个32位的寄存器存放计秒和纳秒的时间值。通过对基准时钟的上升沿计数,每计到5时,计数值清零同时纳秒寄存器的值增加100。纳秒寄存器计满109后秒寄存器的值加1,同时纳秒寄存器清零。

在与GPS进行同步时,为了避免时间出现跳跃甚至倒退现象,本地时钟采用逐步修正的方法。例如:正常计时基准时钟的计数值为 5;当基准时钟慢于真实情况时,增大基准时钟的计时值,例如将计时值修改为 2,即每两个基准时钟周期本地时钟值增加100 ns,从而滞后偏差减少60 ns;当基准时钟快于真实情况时,将计数值改为10,即每10个基准时钟周期本地时钟值增加100 ns,从而超前偏差减少60 ns。在进行上述修正前,需要先测量本地时钟超前或滞后于GPS的时间误差,然后根据误差获得补偿的总时长生成补偿标志。

3 测试结果

实际应用中,授时单元将时间信息通过以太网按 IE1588v2发布,通过交换机送到各个终端,终端根据上述设计方法解析时钟。当有GPS信号时,同步模块的时间信息来自GPS,当没有GPS信号时,同步模块的时间信息来自本模块的晶体振荡器。用本模块的晶体振荡器时,其频率稳定度取决于本振的质量。测试平台如图7所示,主时钟同步模块产生1PPS信号,同时把授时信号通过以太网送到从时钟同步模块,从时钟同步模块提取1PPS信号。主从时钟模块的1PPS可以保持高度同步。

图7 时钟同步测试平台

一般地,对于IEEE1588的测试通常有两种办法:一种是通过软件对收到的脉冲进行统计,得出偏差值的分布图;还有一种是采用示波器,在无限余辉模式下进行同步测量。本项目中采用示波器观察法。两个1PPS信号送入示波器观察,从图8可以看到,两者的时间偏差小于300 ns。在声呐的基阵信号采集中,如果基阵工作频率为1 kHz,则300 ns的时钟偏差,将会引起 0.11°的相位偏差,完全满足工程要求。

图8 主时钟与从时钟PPS信号的同步波形

4 结束语

本文基于IEEE-1588v2协议和GPS,利用FPGA实现的时间同步模块,在通过1级交换时,其同步精度在300 ns以内,完全满足多型声呐对水声信号同步采集的要求。本文采用的同步技术,不同于之前声呐设备基阵信号采集的同步技术,符合OSI分层思想,具有良好的可扩展性,其应用可扩展到多基地声呐或一体化声呐等应用场合。针对基于IEEE1588v2同步技术的同步精度研究,还需要从网络架构、带宽,高精度温补晶振以及时间精度校准等方面进行深入研究,以适应更多的应用场合。

[1]徐荣,任磊,邓春胜.GJB22A-99声呐通用规范:9-10分组传送技术与测试[M].北京:人民邮电出版社,2009:217-250.

[2]颜科峰.大孔径拖线阵数据采集的同步技术研究[J].声学与电子工程,2012,(2):17-18.

[3]IEEE Instrumentation and Measurement Society.IEEE standard for a precision clock synchronization protocol for networked measurement and control systems:IEEE Std 1588™-2008[S].2008.

[4]杨永标,杨晓渝,周捷.利用 FPGA 实现 GPS 失步下精确守时[J].电力自动化设备,2007,27(7):109-112.

[5]张鹏,王少荣,程时杰.电网状态监测系统 GPS 同步时钟的稳定性研究[J].继电器,2004,32(23):19-20.

[6]魏丰,孙文杰. IEEE1588 协议时钟同步报文的精确时间标记方法研究[J].仪器仪表学报,2009,30(1):163-169.