一种高精度低温度系数带隙基准源*

王文建

(浙江商业职业技术学院应用工程学院,杭州310053)

一种高精度低温度系数带隙基准源*

王文建*

(浙江商业职业技术学院应用工程学院,杭州310053)

通过相同材料电阻的比值来抵消带隙基准源的一阶温度系数来达到低温度系数,同时还设计了修调电路进一步提高基准电压的精度。采用0.8 μm BiCMOS 9V工艺流片,带隙基准源面积为0.035 mm2。结果表明:在-40 ℃~125 ℃范围内,基准电压的温度系数为11×10-6/℃;电源电压在4.5 V~9.0 V范围内变化时,基准电压的变化量为0.4 mV,电源调整率为0.09 mV/V。

温度系数;修调电路;带隙基准;电源调整率

在锂电池充电管理集成电路中集成了对充放电过程中所有状态的监测功能,包括涓流充电监测、恒定电流充电监测、恒定电压充电监测,自动再充电监测、充电终止监测等,这些监测是需要精度很高温度系数很低的参考电压作为比较点,所以带隙基准电压的性能直接关系到集成电路的性能。这就对带隙基准源的性能提出了更高的要求,包括高输出精度、低温度系数、低电源电压调整率、高电源抑制比等[1-12]。

本文设计的带隙基准源是通过相同材料电阻的比值来抵消带隙基准源的一阶温度系数,获得低温度系数的基准电压;同时设计了修调电路以进一步提高基准电压精度,最后流片并给出测试结果。

1 电路实现

带隙基准源图如图1所示,包括启动电路和基准电压产生电路。

1.1 启动电路

如图1所示,上电后,M1和M2导通,使得M4、M5、M6的栅极为低电平而导通,启动电路开始工作。当基准电压产生电路开始工作后,M1导通,M4、M5、M6的栅极拉到高电平,M4、M5、M6管截止,启动电路停止工作。

图1 带隙基准源

1.2 基准电压产生电路

如图1所示,启动电路停止工作后,M4、M5和M6处于截止状态,此时由M8管提供电流。由于放大器的反馈作用,A和B点电位相同,流过Q1、Q2的电流相同。

Q2的发射极面积是Q1的8倍,所以流过R3的电流为:

(1)

设计中R3取60 kΩ,由此算出支路电流的值约为1.38 μA,与仿真结果一致。

(2)

两边对温度求导有:

(3)

(4)

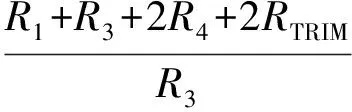

通过调整电阻比值可得到零温度系数基准电压。

图2 修调电阻

1.3 修调电阻RTRIM

如图2为修调电阻,通过调整修调电阻RTRIM,一方面可以调整温度系数,另一方面也可以调整基准电压的输出精度;其中A、B、C、D为修调点,修调前修调点是通过铝条连接的,把所并联的电阻短掉。

根据式(2)得,修调前后的基准电压值与VBE、电阻比值有关,因此修调前后的基准电压值由修调前后的电阻比值确定,可以把这个比值作为修调测试的判据。

具体烧断哪个修调点,根据表1查询可知得。测试时,记下修调前的基准电压值V0,然后用目标值1.225 0 V除以V0得到X值,表1中查找接近的X值,由X值确定烧断哪个修调点。例如,设修调前的基准电压值为1.210 0 V,则

查询表1,序号4接近,需要修调A、B。

通过在修调点上加电流来烧断铝条。具体过程是:在修调点的一端PAD上加如图3所示的电路,另一端PAD接地;在VCC端加电压3 V,控制继电器S1闭合30 ms。

图3 修调点烧断电路

序号修调点基准电压值/VX12345678910111213141516不修调ABA、BCA、CB、CA、B、CDA、DB、DA、B、DC、DA、C、DB、C、DA、B、C、D1.20191.20511.20791.21101.21411.21691.22011.22291.22591.22911.23181.23501.23781.24091.24381.24691.01921.01651.01421.01161.00901.00671.00401.00170.99930.99670.99450.99190.98970.98720.98490.9824

图4 芯片版图

2 芯片版图

图4为锂电池充电管理集成电路版图,其中带隙基准源面积为0.035 mm2。集成电路采用0.8 μm BiCMOS 9 V工艺进行制作。

3 测试结果及分析

锂电池充电管理集成电路采用0.8 μm BiCMOS 9 V工艺进行流片,对带隙基准源进行了测试。

测试工具:稳压电源(精度为0.1 V)、示波器(两种带宽输入,不同带宽探头具有不同寄生电容)、加热炉、冷柜、万用表(电压精确度为0.1 mV~1 mV,电流精确度为0.1 μA)等。

图5为基准电压随电源电压VCC变化曲线。电源电压VCC在4.5 V~9.0 V变化时,基准电压VREF的变化量约为0.4 mV,电源调整率为0.09 mV/V。

图5 基准电压随电源电压变化曲线

图6为基准电压VREF温度特性曲线。在6.0 V电源电压下,在-40 ℃~125 ℃温度范围内的温度系数为11×10-6/℃。

图6 基准电压温度特性曲线

图7为带隙基准源的电源抑制特性曲线,在低频(小于1 kHz)时为-74 dB。

图7 带隙基准源电源抑制特性曲线

4 结束语

为了适应锂电池充电管理集成电路对带隙基准源精度的要求,设计了一种高精度低温度系数带隙基准源。该带隙基准源是通过相同材料电阻的比值来抵消带隙基准源的一阶温度系数,获得低温度系数的基准电压;还设计了修调电路进一步提高基准电压的输出精度;使得输出的基准电压的精度和温度系数有了很大改善。锂电池充电管理集成电路采用0.8 μm BiCMOS 9 V工艺进行流片,带隙基准源所占面积为0.035 mm2。测试结果表明:在6 V电源电压下,在-40 ℃~125 ℃温度范围内的温度系数为11×10-6/℃;电源电压在4.5 V~9.0 V范围内变化时,基准电压的变化量为0.4 mV,电源调整率为0.09 mV/V;在电源电压6 V时,带隙基准源的电源抑制比在低频(小于1 kHz)时为-74 dB。该设计的带隙基准源可广泛应用于电源管理类集成电路中,具有较高的参考价值。

[1] 高献坤,雷君召,丁赪璐,等. 高电源抑制比、低温漂带隙基准电压源的设计[J]. 河南农业大学学报,2011,45(4):442-444.

[2] 胡佳俊,陈后鹏,蔡道林,等. 高电源抑制比低温漂带隙基准源设计[J]. 微电子学,2012,42(1):34-37.

[3] 张万东,陈宏,王一鹏,等. 高电源抑制比和高阶曲率补偿带隙基准源[J]. 微电子学,2011,41(1):57-60.

[4] 杨宁,史仪凯,袁小庆,等. 高精度、低功耗带隙基准源及其电流源设计[J]. 传感技术学报,2014,27(1):58-63.

[5] 黎官华,王卫东. 高刷新率高稳定性LED恒流驱动电路的设计[J]. 电子器件,2015,38(3):531-537.

[6] 徐星,袁红辉,陈世军,等. 高性能CMOS带隙基准电压源及电流源的设计[J]. 半导体技术,2011,36(3):229-233.

[7] 李沁莲,陈向东,王丽萍,等. 基于衬底运放的2阶温度补偿带隙基准电路[J]. 微电子学,2011,41(3):332-335.

[8] 吴金,聂卫东,常昌远,等. 基于失配控制的非线性补偿带隙基准电路设计[J]. 东南大学学报(自然科学版),2011,41(5):917-922.

[9] 李睿,冯全源. 一种低功耗高精度带隙基准的设计[J]. 电子技术应用,2015,41(3):51-54.

[10] 朱彤,黄飞,谢森,等. 一种低温度系数高驱动能力的带隙基准电路[J]. 微电子学,2011,41(4):545-549.

[11] 唐宁,李佐,李琦. 一种改进的非线性匹配高阶补偿基准源的设计[J]. 电子器件,2013,36(6):797-801.

[12] 杨金,代月花,宗桂林,等. 一种高电源抑制比低温漂系数带隙基准电路[J]. 微电子学,2014,44(3):297-300.

AHighPrecisionLowTemperatureCoefficientBandgapReference*

WANGWenjian*

(Applied Engineering College,Zhejiang College of Business,Hangzhou 310053,China)

By the same material resistance ratio to offset the bandgap of the first order temperature coefficient a low temperature coefficient is achieved,and the trim circuit is also designed to further improve the accuracy of the reference voltage. Used 0.8 μm BiCMOS 9 V process flow sheet,the bandgap reference area is 0.035 mm2. Test results show that in the temperature range of -40 ℃~125 ℃,the temperature coefficient of the reference voltage is 11×10-6/℃;when the power supply voltage variation is within the range of 4.5 V~9.0 V,the reference voltage variation is 0.4 mV,power adjustment rate 0.09 mV/V.

temperature coefficient;trim circuit;bandgap reference;power adjustment rate

10.3969/j.issn.1005-9490.2017.05.003

项目来源:浙江省科技厅公益技术应用研究计划项目(2017C31077);浙江省教育厅科研项目(Y201635565)

2016-08-16修改日期2016-10-28

TN432

A

1005-9490(2017)05-1065-03

王文建(1973-),男,硕士,高级工程师,从事电源管理和数模混合集成电路设计和研究,540843839@qq.com。