2FSK调制解调器的FPGA与MATLAB设计与实现

贺 炜

(西安石油大学 电子工程学院 陕西 西安 710065)

2FSK调制解调器的FPGA与MATLAB设计与实现

贺 炜

(西安石油大学 电子工程学院 陕西 西安 710065)

文章介绍了相位连续的2FSK调制解调的原理。利用FPGA,采用键控法设计了可以根据检测到的脉冲码元分时输出不同频率正弦波的DDS发生器。利用MATLAB 窗函数设计了FIR滤波器,研究了不同窗函数及量化位数对于FIR滤波器频率响应曲线的影响,求出FIR滤波器抽头系数并导入FPGA FIR IP核,实现了全并行分布式结构的FIR低通及带通滤波器。最后采用Verilog hdl语言实现了基于FPGA的2FSK调制及非相干解调,通过Modelsim仿真得到非相干解调各节点信号的波形。仿真及实验结果表明基于FPGA和MATLAB设计的相位连续2FSK调制解调器是正确的,具有较高的实用性和可靠性。

FPGA;MATLAB;2FSK;FIR;调制;解调

1 引言

随着EDA技术的高速发展,现场可编程门阵列(Field-Programmable Gate Array,FPGA) 因其具有可编程性、开发周期短、集成化程度高、灵活性强等特点,在通信领域的应用越来越广[1]。频移键控(Frequency-shift keying,FSK)调制解调技术是现代通信中一项关键的技术[2-3],调制解调效果的好坏更是直接关系着通信是否成功。文章以 Altera型号FPGA 作为硬件核心,硬件与软件相结合,采用verilog hdl语言及MATLAB仿真,设计了DDS发生器及FIR滤波器,实现了相位连续的2FSK调制解调器,具有较高的实用性、可靠性和灵活性。

2 2FSK调制解调原理

频移键控(FSK)是利用载波的频率变化来传递数字信息,在2FSK中,载波的频率随二进制基带信号在f1和f2两个频率点间变化。由于在FSK信号中提取相干相干载波相对困难,因此实际工程中多采用非相干解调法[4]。

3 2FSK调制设计与仿真

本节利用20KHz和40KHz正弦波作为载波,根据上节所述2FSK调制解调原理,采用键控法设计一个分辨率为0.012Hz的DDS(Direct Digital Synthesis)发生器,可以根据检测到的码元输出两种相位均为0且频率为20KHz和40KHz的正弦波,即2FSK调制。

3.1 DDS发生器

采用Altera EP4CE15F17C8型号FPGA,时钟频率为50MHz。使用MATLAB将一个周期正弦波分成256个点,计算频率50M/256,分辨率约等于195.31kHz,则DDS只能输出频率为195.31KHz整数倍的正弦波,显然达不到我们设计20KHz和40KHz正弦波的要求,因此需要采用相位控制字pword、频率控制字fword及地址计数器N分别来改变相位、频率与分辨率。

如式(1)所示,其中Fout为输出频率,Fclk为50M,N=32为地址计数器,分辨率为50M/232约等于0.012Hz,DDS能够输出频率为0.012Hz整数倍的正弦波,满足设计要求。在QuartusⅡ中例化一个256×8位的 ROM IP核,将通过MATLAB得到的256个点的值初始化到ROM中。让地址计数器每次增加一定的值后把高8位当作有效地址送给ROM将相位控制字设置为0,因此根据式(1),20KHz和40KHz对应的fword大约分别为3333333和1666666。

3.2 键控法

为了得到相位连续且初始相位为0的2FSK调制波,利用PC通过串口发送1个8bit数据,在FPGA接收到数据以后,经过脉冲扩展使得每位码元能保持1ms,即频率为1KHz,由于每个码元持续的时间分别为载波一个周期时间的40倍和20倍,由于pword为0,所以初始相位为0。检测到高电平则输出40KHz的正弦载波,检测到低电平则输出20KHz的正弦载波。

以FPGA接收到一个字节01011011为例,脉冲扩展后通过开关电路对20KHz和40KHz两个不同的正弦载波源进行选通,即为2FSK调制。非连续FSK调制,采用键控法产生相位连续的调制信号(CPFSK)频谱宽度小且主瓣宽度明显小于FSK,旁瓣衰落更快,因此能够有效避免杂波产生,提高信号传输的稳定性和识别率。

4 2FSK解调设计与仿真

本节为了实现2FSK解调,利用MATLAB对FIR滤波器进行仿真,求出低通及带通滤波器系数,导入到FPGA FIR IP核,利用Verilog hdl语言实现了基于FPGA的2FSK调制及非相干解调,并通过Modelsim仿真给出了非相干解调各节点信号的波形。

4.1 FIR滤波器的MATLAB设计与仿真

数字滤波器分为无限脉冲响应(IIR)滤波器和有限脉冲响应(FIR)滤波器。在FPGA设计中,由于可以采用IP核进行设计,使得FIR滤波器设计更为简便。FIR滤波器的设计方法有频率取样法、窗函数法(包括矩形窗、汉宁窗、海明窗、凯塞窗等)及等纹波优化设计方法等。文章采用窗函数法设计实现了FIR低通及带通滤波器。

通过MATLAB仿真,得到矩形窗、汉宁窗、海明窗、凯塞窗等窗函数设计的滤波器,频率响应曲线如图1所示,由图1可以看出相同滤波器阶数情况下的凯塞窗具有更好的性能;利用凯塞窗等三种方法设计的滤波器,频率响应曲线由图2所示,由图2可以看出对比窗函数法与最优设计方法,相同滤波器阶数下凯塞窗滤波器的阻带纹波逐减小,因此采用凯塞窗滤波器;滤波器系数未量化、12位和14位量化的滤波器频率响曲线如图3所示,由图3可以看出,量化位数对滤波器的阻带纹波有较大的影响,且量化位数越高影响越小,故采用14位量化。

图1 各种窗函数设计的滤波

图2 三种方法设计的滤波器

图3 三种系数量化后滤波器

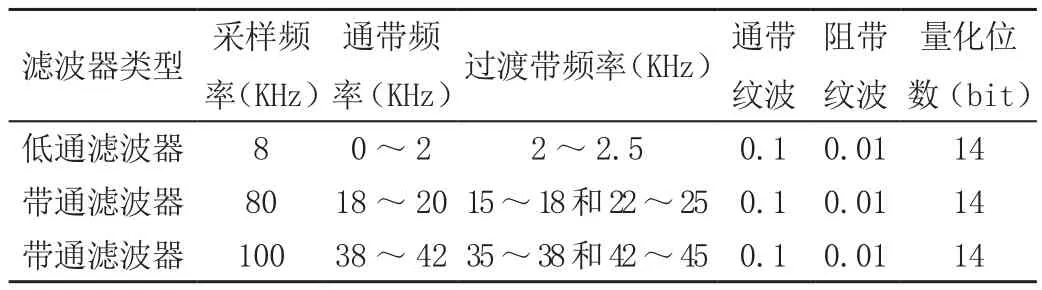

考虑到FPGA的逻辑资源以及实验的易实现性及精度等问题,滤波器参数选取如表1所示。首先采用kaiserord(fc,mag,dev,fs)函数获取满足要求的最小滤波器阶数,然后利用凯塞窗函数设计滤波器,将生成的滤器抽头系数分别写入txt文档中。文章设计实现了一个2KHz低通滤波器和两个20KHz、40KHz带通滤波器。

4.2 FIR滤波器的FPGA实现与仿真

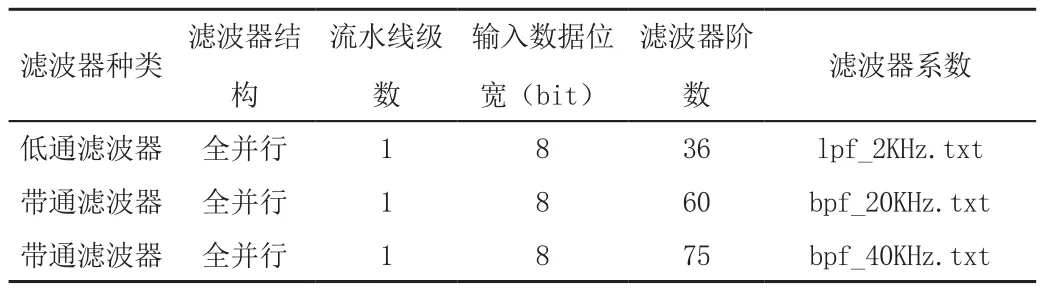

文章采用Altera EP4CE15F17C8型号FPGA 作为硬件核心,利用QuartusⅡ软件中的FIR IP核来实现FIR低通及带通滤波器。该IP核提供了4种不同的实现结构:全串行、全并行、多比特及多时钟周期结构,不同结构速度和所占的芯片资源不同,文章利用全并行分布式算法结构,所占资源较大但是速度最快。将上述3.1节MATLAB仿真得到的滤波器抽头系数分别导入IP核,生成低通及带通滤波器,FIR IP核相关参数如表2所示。

表1 FIR滤波器参数

表2 滤波器FIR IP核相关参数

5 结语

文章设计了可以分时输出不同频率正弦波的DDS发生器,利用键控法使得DDS发生器根据检测到的码元产生两种不同频率的正弦波,利用MATLAB仿真FIR滤波器分别求得了低通及带通滤波器的抽头系数,并导入FIR IP核,将MATLAB与FPGA结合使得FPGA实现了全并行分布式结构的FIR低通及带通滤波器。最后采用Verilog hdl语言实现了基于FPGA的2FSK非相干解调,将解调出的8bit数据通过串口发送到PC,通过Modelsim仿真给出了非相干解调各节点信号的波形,仿真及实验结果表明基于FPGA和MATLAB设计的2FSK调制解调器是正确的,具有较高的实用性和可靠性。

[1]罗杰.VerilogHDL与FPGA数字系统设计[M].北京:机械工业出版社,2015:1-2.

[2]应亚萍,许建凤.2FSK调制解调系统的FPGA设计与实现[J].浙江工业大学学报,2010,38(3):282-285.

[3]周志法,艾文,张尧琴.基于FPGA的2FSK数字信号调制解调[J].电子科技,2012,25(3):121-123.

[4]樊昌信,曹丽娜.通信原理[M].第7版.北京:国防工业出版社,2015:177-225.

[5]关进辉,姜恒.基于FPGA的相位连续的2FSK信号的设计与实现[J].现代电子技术,2015,36(9):79-81.

Design and implementation of 2FSK modem on FPGA and MATLAB

He Wei .

School of Electronic Engineering, Xi'an Shiyou University, Xi'an 710065, China.

This paper introduces the continuous phase 2FSK demodulation principle. Key method is used to design the DDS wave generator which can output different frequency sine wave by detecting pulse code. Designing FIR filter by the window function of MATLAB, the influence of different window functions and quantization bits on the frequency response curve of FIR filter is studied to calculate the coefficients of FIR filter and import FIR IP core, realizing the full parallel distributed structure low-pass and band-pass filter. Finally implement the 2FSK modulation and the non-coherent demodulation based on FPGA by using Verilog HDL language. By Modelsim simulation, the waveform of noncoherent demodulation is obtained. The simulation and experimental results show that the phase continuous 2FSK modem based on FPGA and MATLAB is correct and has high practicability and reliability.

FPGA;MATLAB;2FSK;FIR; Modulation; Demodulation

TN713 【文献标识码】A 【文章编号】1009-5624(2018)02-0078-03

贺炜(1992-),男,汉族,硕士研究生,主要研究方向:无线通信与导向钻井技术研究。