基于DDR3的相控阵面幅相补偿单元设计

洪伟 钱倩云

相控阵面各通道原始幅度和相位的一致性难以保证,必须进行幅相校正。本文提出了一种基于DDR3存储器的相控阵面幅相补偿单元设计,以FPGA作为控制核心,实现逻辑控制、读写控制、存储器控制等功能,详细介绍了硬件设计、软件流程设计和数据存储设计,给出了完整的设计方案。性能测试结果表明本设计具有快速查询、大容量存储的优点,设计同时兼顾小型化、易移植、方便扩展等需求。

【关键词】幅相补偿单元 DDR3 相控阵

相控阵面具有快速改变波束指向和波束形状的能力,在军事和通信等领域得到了广泛的应用。相控阵面要求每个通道信号的幅度和相位稳定、一致和可控,否则会对波束形成产生不利的影响,但在实际系统中,由于元器件性能的差异、设备加工装配精度的差异以及设备工作频率和环境的差异,导致了相控阵面各通道原始幅度和相位的一致性难以保证,因此相控阵面必须进行幅相校正,并用校正数据对波控码进行修正,相控阵面的波控系统用修正后的波控码进行布相。大型宽带相控阵面工作频带宽、工作模式多,幅相补偿数据量大,需要大容量高性能的幅相补偿单元。针对此应用,本文提出了一种基于DDR3的相控阵面幅相补偿单元设计。

1 设计方案

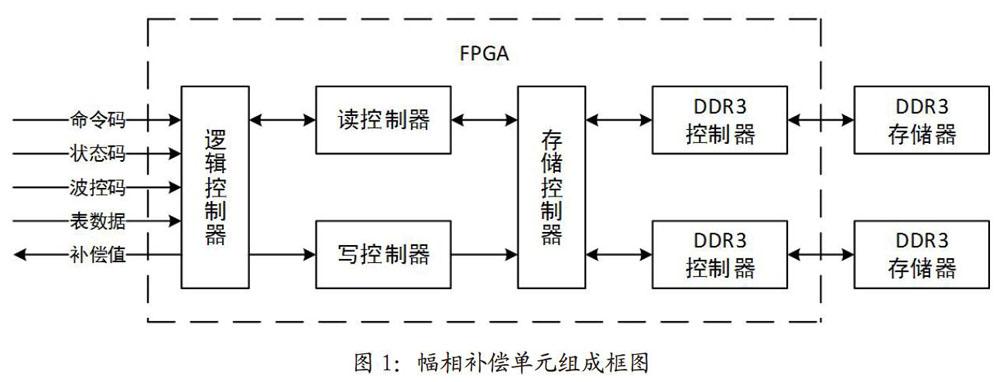

幅相补偿单元主要由逻辑控制器、读控制器、写控制器、存储控制器、DDR3控制器和DDR3存储器组成,幅相补偿单元组成框图如图1所示。

幅相补偿单元的控制器全部在FPGA中实现。逻辑控制器根据幅相补偿单元的输入信号产生控制逻辑,启动读写操作,同时实现幅相补偿单元外部数据与内部数据的交互。读控制器在逻辑控制器的控制下产生读命令、读地址和读控制时序并将读取的数据传递给逻辑控制器,幅相补偿单元的查询操作主要由读控制器完成。写控制器在逻辑控制器的控制下产生写命令、写地址和写控制时序并将经逻辑控制器输入的外部数据写入DDR3存储器,幅相补偿单元的初始化操作主要由写控制器完成。存储控制器在一组读、写控制器与多组DDR3控制器之间实现接口转换和数据缓存功能。DDR3控制器实现对DDR3存储器的底层操作。

DDR3存储器是一种大容量高速存储器件,有着非常高的读写速度,其数据接口一般为8位或者16位。DDR3存储器的读写操作是基于突发的,即从一个选定的地址单元开始,连续存取己设置长度的地址单元,该长度就是所谓的突发长度(Burst Length)。DDR3存储器提供的可编程的读或写的突发长度为4或8。由于DDR3存储器的预取为8位,所以不管突发长度设置为4还是8,一次操作的执行时间是相同的,因此实际操作突发长度设置为8,8位数据接口的器件一次读操作返回64位数据,16位数据接口的器件一次读操作返回128位数据。相控阵面幅相补偿单元按照通道顺序查询补偿值,一个通道一个状态的幅相补偿值通常不超过16位,所以8位数据接口的器件就可以满足幅相补偿单元设计需要并占用较少的资源,同样通过多片DDR3存储器拼接实现更大数据位宽从而提高存取带宽的常规方法并不能提高幅相补偿单元的性能,因此本设计使用多控制器独立工作的方式,每片8位DDR3存储器对应一个DDR3控制器,在提高存储容量的同时提高了性能。

2 工程设计

2.1 硬件设计

本设计FPGA选择赛灵思公司的XC7K325T,DDR3存储器选择镁光公司的MT41J512M8,整个电路工作频率高,时序要求复杂,必须多方面精心设计才能获得尽可能最佳的信号完整性和时序裕量以保证稳定可靠运行。DDR3存储器电路及其与FPGA的连接是硬件设计的重点,本文对其设计进行详细说明。

XC7K325T的IO Bank分为HR Bank和HP Bank兩种,HR Bank具有更宽的工作电压范围,HP Bank具有更高的工作性能,HRBank和HP Bank都可以用于连接DDR3存储器,但是为了获得更好的性能和设计裕量,本设计使用HP Bank连接DDR3存储器并且一片DDR3存储器独占一个HP Bank。时钟信号CK按照差分阻抗80Q布线并在终端并联80Q匹配电阻,数据信号DQS按照差分阻抗80Q布线,数据信号DQ[7:0]和DM按照单端40Q阻抗布线,地址和控制信号按照单端40Q阻抗布线并在终端串联40Ω匹配电阻并上拉至VTT。数据信号DQ[7:0]和DM参考DQS做等长设计,实际按照±3 0mil布线,地址和控制信号参考时钟信号CK做等长设计,实际按照±1OOmil布线,差分信号CK和DQS内部按照±1Omil等长布线。数据信号使用单独布线层布线,通过参考平面与其它信号隔离,时钟信号、地址和控制信号共用两个布线层布线。DDR3存储器电源分为VDDQ和VDD两组,电压均为1.5V,为了简化设计使用一组电源供电,但是每组分别滤波并在每个电源引脚使用O.1uF和O.O1uF电容组合滤波。FPGA IOBank电压与DDR3存储器电源电压保持一致并使用同一组电源供电,同样在电源引脚使用O.1uF和O.O1uF电容组合滤波。DDR3存储器电源电流随操作模式变化很大,在靠近FPGA一侧和DDR3存储器一侧各放置lOOuF大电容。FGPA的IO Bank和DDR3存储器需要的参考电压Vref通过VDDQ经过电阻分压得到并在每个Vref引脚使用O.luF和O.OluF电容组合滤波。

2.2 软件流程设计

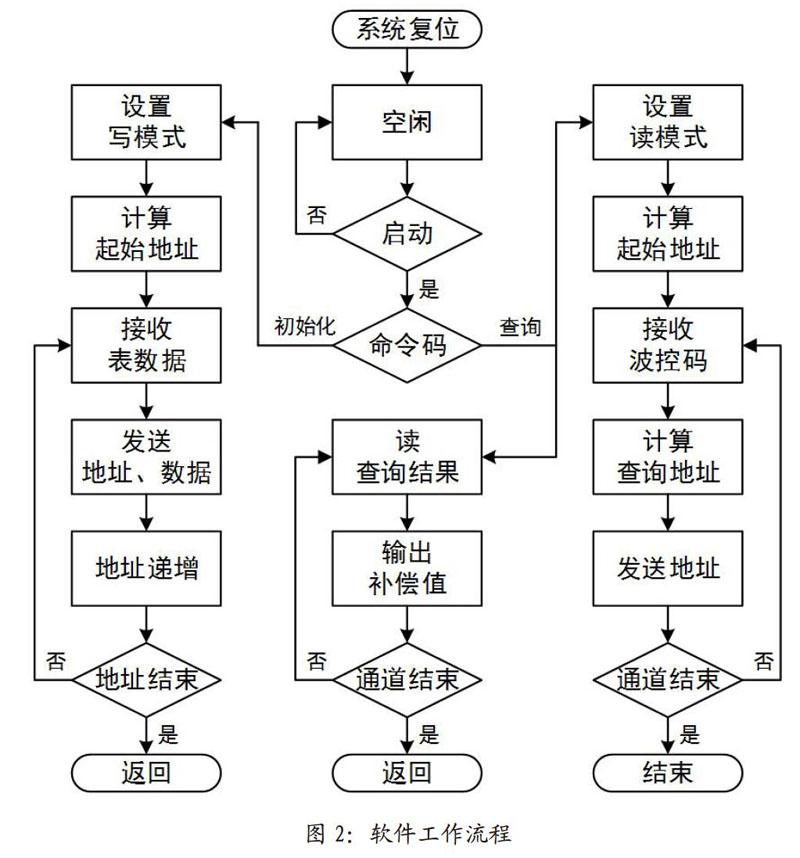

初始化操作和查询操作是幅相补偿单元的两个主要操作,初始化操作是将相控阵面通过测试并整理得到的补偿表数据写入幅相补偿单元,通常在加电后执行,查询操作是以相控阵面的工作状态和通道的原始波控码为地址读取补偿值,在工作时频繁执行。系统复位后幅相补偿单元处于空闲状态,通过设置命令码触发幅相补偿单元启动操作,幅相补偿单元软件工作流程如图2所示。

初始化命令启动初始化操作,逻辑控制器通过激活写控制器设置幅相补偿单元进入写模式,写控制器根据状态码计算补偿表起始地址,然后将接收到的表数据和当前地址一同发送给存储控制器,每发送64bit数据,地址递增8,如果地址超过当前补偿表预设空间则本次初始化操作结束,返回空闲状态,等待下一个命令,否则继续接收数据并写入存储器。查询命令启动查询操作,查询操作输入和输出部分独立运行。逻辑控制器通过激活读控制器设置幅相补偿单元进入读模式,读控制器根据状态码计算补偿表起始地址,然后接收1个通道的波控码并根据起始地址、状态码和波控码计算本次查询地址并将地址发送给存储控制器,如果所有通道查询地址都已经发送完则输入操作结束,等待输出操作完成。逻辑控制器在激活读控制器的同时启动输出操作,读取读控制器返回的查询结果并截取有效数据输出,如果所有通道补偿值都输出完则本次查询操作结束,返回空闲状态,等待下一个命令,否则继续读取查询结果并输出。

2.3 数据存储设计

DDR3存储器按照Bank、Row、Column的结构管理数据,每片DDR3存储器有8个Bank。应用模式不同,DDR3接口效率差异非常大。读取操作时先根据Bank地址和Row地址将一行数据全部读取到缓存中,然后根据Column地址选择欲读取数据输出,当连续两次读取数据在同- Bank的不同行时,需要先执行预冲操作,然后再执行读取操作,两次操作之间有较大延时,当连续两次读取数据在不同Bank中时,两次操作可以同时执行。因此,根据幅相补偿单元工作模式和补偿数据特点设计数据的存储结构,使幅相补偿单元始终工作于方式二,可以获得更高的效率。

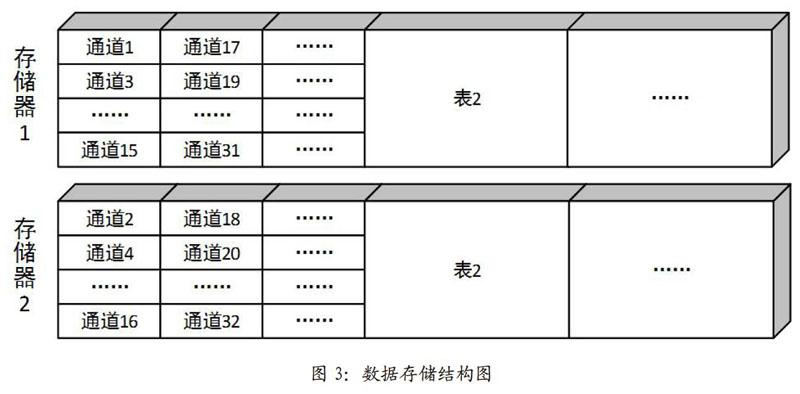

幅相补偿单元的数据存储结构分为表、通道和状态三级。表是按照相控阵面工作模式划分的,例如发射补偿表和接收补偿表,每个表又划分为若干个通道,每个通道占用一段连续的存储空间,用来存储相控阵面一个通道全部状态的校正数据,状态是最小的存储单元,每个状态对应一个补偿值,根据补偿表的不同,一个状态通常占用1个字节或2个字节存储空间。幅相补偿单元的数据存储结构如图3所示。

两片存储器构成了一个整的存储空间,该存储空间划分为若干个表,每个表同时占用两片存储器。表里的通道在两片存储器之间交替排列,序号为奇数的通道位于存储器1,序号为偶数的通道位于存储器2,查询操作时两片存储器交替工作,突破了DDR3存储器连续激活间隔时间的限制,提高了执行效率。同一个存储器里的通道按照Bank顺序排列,以存储器l为例,通道1的起始地址是第一个Bank的起始地址Ox00000000,通道3的起始地址是第二个bank的起始地址Ox04000000,以此类推,通道15的起始地址是最后一个Bank的起始OxlCOOOOOO,通道17又回到第一个Bank,排在通道1之后,起始地址为通道1起始地址加通道长度,以此类推,依次排列,直至最后一个通道,如此排列,存储器始终处于8个Bank轮流操作状态,减少了操作间隔时间,提高了操作速度。

3 性能测试

设计完成后通过时序仿真对设计性能进行了验证,以64个通道为例的时序验证如图4所示。CLK 200MHz是系统工作时钟,频率200MHz,VALID CMD_ ADDR Ml和VALID_ CMD_ ADDR M2分别是给DDR3控制器1和DDR3控制器2的地址和命令使能信号,高电平有效,每个正脉冲表示启动一个通道查询操作,VALID READ Ml和VALIDREAD M2分别是给DDR3控制器1和DDR3控制器2的读取使能信号,高电平有效,每个正脉冲表示完成一个通道查询操作。幅相补偿单元的所有控制器以200MHz系统时钟运行,两个DDR3控制器交替运行,單个DDR3控制器执行通道查询操作频率为100MHz,即每1Ons启动一次通道查询操作,操作完成初始延时为220ns,之后按照操作启动顺序每lOns完成一次操作,64个通道总的查询时间为540ns(220ns+320ns)。

4 结论

本文设计的相控阵面幅相补偿单元实现了对大容量幅相补偿数据的快速查询,具有小型、高速、容易移植和扩展方便的特点,可以灵活地与不同相控阵面的波控系统集成,满足阵面级或子阵级幅相补偿应用。

参考文献

[1]张光义,赵玉洁,相控阵雷达技术[M].北京:电子工业出版社,2006.

[2] JEDEC.DDR3存储器Specification [S].2012.JESD79-3F.

[3]殷晔,李丽斯,常路等,基于FPGA的DDR3存储控制的设计与验证[J],计算机测量与控制,2015,23 (03): 969-971.

[4]孟晓东.基于FPGA的DDR3控制器设计与验证[D],国防科学技术大学,2012.