高速增强型GaN HEMT栅驱动电路设计

黄伟 周德金 许媛 何宁业 胡一波 胡文新

摘要 增强型GaN HEMT器件的开关速度较现有硅基MOSFET有很大提高,导致硅基MOSFET栅驱动电路无法用于驱动增强型GaN HEMT器件。本文设计了一种适用于增强型GaN HEMT器件的新型栅驱动电路,进而实现高速开关速度。该驱动电路包括接口电路、死区产生电路、电平移位电路、输出驱动电路、欠压保护电路、过流和过热保护电路,Hspice软件仿真结果表明该栅驱动电路功能正确,性能良好,验证了设计有效性。

【关键词】增强型 GaN HEMT 驱动电路 栅驱动

1 引言

以硅材料为基础的传统电力电子功率器件己逐步逼近其理论极限,难以满足电力电子技术高频化和高功率密度化的发展需求。与传统的Si基功率器件相比,GaN功率器件展现了其在导通电阻和开关速度上的明显优势,可以使功率转换器实现更小体积、更高频率及更高效率,从而在汽车、通信、工业等领域中具有广阔的应用前景。而系统开关频率的提高,能有效地减小电路中电容、电感及变压器的尺寸,而高速的栅极驱动电路用于驱动GaN功率器件,使得整个功率转换器达到高效率且减小电路面积,节省成本,

增强型高电子迁移率晶体管(HEMT)是GaN功率器件面向电力电子领域应用的主要器件。GaN HEMT的主要优点有极低的门极电荷,极低的分布电容、超快的开关速度、超小的器件体积、优异的品质因数、超低的开关损耗和很低的器件发热。在同样的耐压条件下,其与Si基MOSFET相比主要有:导通电阻和器件体积小、开关速度快、电流密度大和功率密度高的特点。GaN HEMTs的这些特点保证了其未来具有非常广阔的前景与市场。但是也存在一些需要特别注意的因素:阈值电压低;栅源电压上限低;可反向导通。

上述特别因素的存在,使得GaN器件的驱动使用时需要特别考虑,导致目前传统的用于硅基MOSFET的驱动电路不能直接适用于增强型GaN HEMT器件。GaN功率器件通常用在高频开关频率下(MHz以上),尤其是开关频率达到IOMHz之后,传统栅极驱动较大的延时(几十纳秒)就会占开关周期比例过大,甚至导致逻辑错误,进而限制了开关频率无法升高。本论文设计了一种适用于GaN HEMT器件的栅极驱动电路,详细给出了电路结构和核心电路具体实现,并给出了核心电路和总体电路的仿真验证结果。

2 驱动电路结构

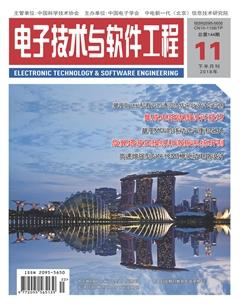

如图1所示即为本文设计的适用于增强型GaN HEMT的栅驱动电路,其电路功能模块包括用于输入电平转换的2路接口电路H和L,用于产生死区保护时间的死区产生电路,高压侧进行低压转高压电平变换的电平移位电路,低压端延迟补偿的低端延迟匹配电路,两路输出驱动电路H和L,用于对整体电路状态进行监控和保护的欠压封锁电路H和L、过流和过热保护电路。

H端和L端两路5V的输入方波信号经过电平移位和延迟补偿处理后被转换成相位相匹配的2路驱动信号,L端的O~5V驱动信号和H端以vs为参考的幅值为5V的驱动信号,然后进入高压和低压驱动模块的输出级驱动电路。特别之处在于,电平移位电路、驱动电路H和欠压封锁电路H构成的H端驱动模块,在版图设计和工艺加工是必须做在一个具有浮动电位的高压阱中。由于H端控制信号经过电平位移电路后,相比于L端信号产生了一定的延迟,因此须在L端通路上加入延迟匹配电路,进行延迟补偿。

3 核心电路实现及仿真

3.1 接口电路

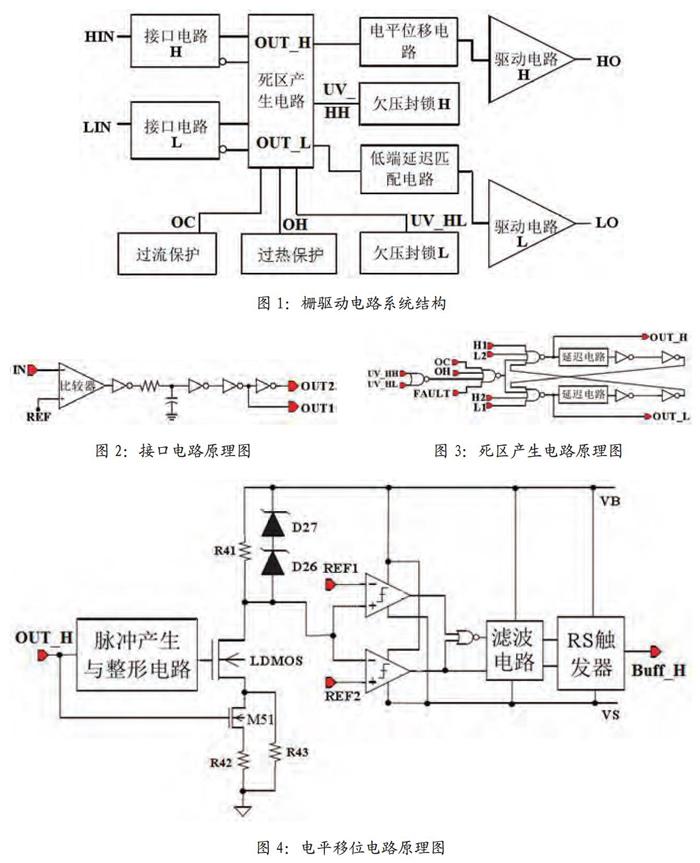

图2为本文接口电路的原理图。输入端口IN接收来自芯片外部输入的PWM脉冲控制信号,该PWM脉冲信号被输入到输入波形整理比较器的负端,与正端的参考电压进行比较。当输入电压大于基准电压时,比较器输出低电位,经过低通滤波电阻与低通滤波电容组成的滤波网络,输出信号OUTI与IN同相,OUT2与IN反相。本文设计的逻辑控制电路电源电压为5V,所以OUTI与OUT2的幅值均为5V。本文的接口电路H和L均采用图2所示电路实现。

3.2 死区产生电路

图3为本文死区产生电路的具体实现。逻辑信号H1、L2、H2和L1为两个接口电路的输出信号。FAULT信号是系统控制信号,OC为过流保护电路的输出,OH是过热保护电路的输出,UV HH是欠压封锁电路H的输出,UV HL是欠压封锁电路L的输出。当FAULT、信号为高,或者电路出现过热、过流或者电源电压发生欠压时,就会触发死区电路的输出为恒定的低电平,控制后续电路停止工作,直至触发信号恢复正常。所设计的死区时间的大小由延遲电路决定,可以采用反相器和RC网络。

3.3 电平移位电路

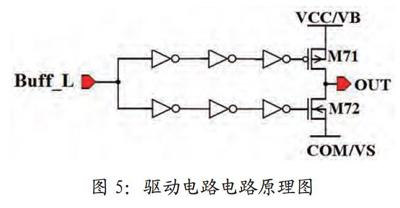

图4为本文电平移位电路的具体实现。其实现的功能是将0~5V的数字逻辑电平转换为以高压VB和VS为摆幅基准的高压数字逻辑电平,为此电路中必须适用高压LDMOS器件。图4所示电路的工作原理如下:输入端的脉冲产生和整形电路将输入信号OUT H转化为窄脉冲信号,此时方波信号的逻辑电平仍然为0~5。当OUT H为低时,M51管关断,LDMOS的栅极为高电平时,LDMOS开启,LDMOS漏端电位为较VB低的VH; LDMOS栅极为低电平时,LDMOS漏极电位为VB。当OUT H为高时,M51管开启,LDMOS的栅极为高时,LDMOS开启,LDMOS漏极电位为较VB低的VL当LDMOS的栅极为低时,LDMOS关断。比较器将LDMOS漏极分别与基准电压进行比较,输出两路脉冲信号,通过或非门进行逻辑运算和滤波,再通过RS触发器整形为一路方波信号。与输入方波信号相比,此时的低电平电压从0提高到了VB,输出方波信号的幅值为VB~VS之间。

3.4 驱动电路

驱动电路用以减小输出阻抗,同时增强输出驱动能力。图5为本文驱动电路的一种具体实现原理图。输出级驱动电路由反相器链,输出驱动管M71和M72组成。2个输出驱动管决定了电路的驱动电流和输出电阻。正常工作时,输出驱动管M71管和M72管交叉导通,相互之间导通时间间隔受死区时间保护;当电路出现过热、过流或者电源电压发生欠压时,输出驱动管将会被关闭。

3.5 电路仿真

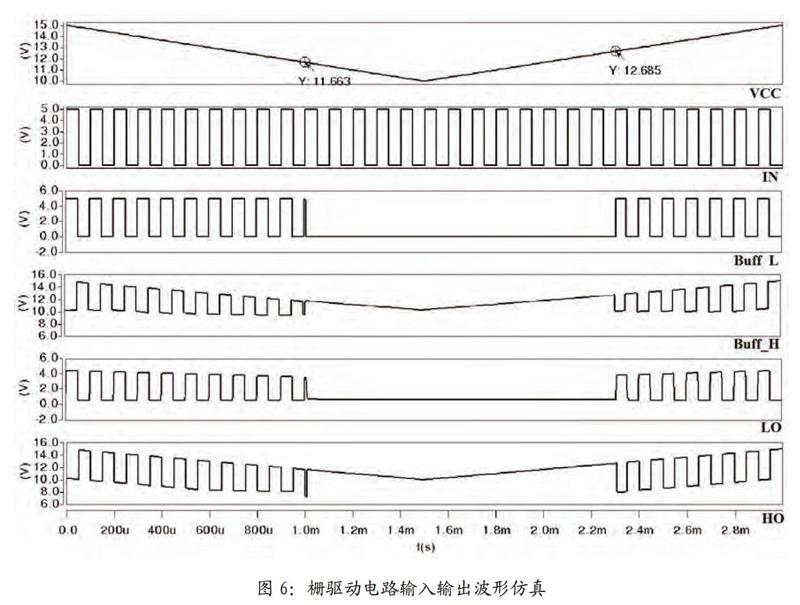

本文栅驱动电路将输入0~5V方波信号经过电平移位和延迟补偿处理后转换成相位相匹配的2路具有死区保护的相位相反方波信号,然后进入输出驱动电路转换为2路低电平不同,但摆幅相同,并且驱动能力增强了的输出信号HO和LO。图6为采用Hspice软件和上华BCD工艺对所设计栅驱动电路进行晶体管级仿真得到的的输入输出曲线,输出高压部分的H端电源电压VB为15V,VS采用IOV电压,L端电源电压VCC为5V。由于增强型GaN HEMT器件的栅驱动电压为0~SV,因此本文设计的H端正常输出的HO输出摆幅为10V~15V,L端正常输出的LO输出摆幅为0- 5V。本文中设计的栅驱动电路集成了欠压锁定保护功能,当欠压保护模块检测到VB电压偏低,并判断发生欠压时,提供给驱动级电路的Buff H和Buff L电平应该为1和0,当VB电压回升至正常电压时,死区产生电路会重新开启电路,恢复工作状态。从图6中给出的瞬态仿真结果可以看出,电路正常工作时,电平转换和逻辑关系完全正确。当VB电压降低到11.9V并触发欠压保护电路产生保护信号时,BuffH和Buff L电平被锁定,输出HO和LO信号也被锁定;当VB电压回升至12.68V以上电压时,电路恢复正常工作状态。仿真结果可以看出,电路功能完全正确,符合设计要求。

4 结论

采用上华BCD工艺设计了一种用于增强型GaN HEMT器件的栅驱动电路,给出了详细的电路结构和具体实现电路,仿真表明电路功能正确,满足设计要求。

参考文献

[1]张波,邓小川,陈万军等.宽禁带功率半导体器件技术[J],电子科技大学学报,2009, 38 (05): P618-623

[2]王树奇,吉才,刘树林.GaN组合開关电路及其驱动技术研究[J].西安科技大学学报,2016,36 (06):P882-887

[3]张弘,郑介鑫,郭建平.GaN功率开关器件驱动技术的研究与发展[J].电力电子技术,2017,51 (08):P71-73

[4]何亮,郑介鑫.GaN功率开关器件的产业发展动态[J].电力电子技术,2017,51 (08):P44-48

[5]任小永.David Reusch,季澍等.氮化镓功率晶体管三电平驱动技术[J],电工技术学报,2013,28 (05):P202-206.