“计算机组成原理”实验CPU设计方法研究

王力生, 余智铭, 张冬冬

(同济大学 电子与信息工程学院, 上海 201800)

“计算机组成原理”是计算机专业基础课程,其课程内容与计算机多门专业课程联系紧密,学生对其内容的理解直接或间接地影响到对其他专业课程的学习,并关系到学生对计算机系统的整体认识[1-5]。

在教授这门课程时加入CPU设计实验可以帮助学生理解计算机的组成结构[6],但是,由于CPU设计实验本身具有较高的难度,致使许多学生不能很好地完成课程实验。主要问题在于学生设计CPU时,数据通路设计不清[7]、信号传输错误﹑各部件连接混乱等。针对这些实验教学问题[8],本文提出了一种帮助学生更好地设计出单周期CPU的方法[9]。

1 设计方法

本文所设计的CPU是基于MIPS32构架,由31条指令集组成。使用的设计语言为Verilog,采用的集成工具为Xilinx公司的Vivado。31条指令分别为[9]:

R型指令:add,addu,sub,subu,and,or,xor,nor,slt,sltu,sll,srl,sra,sllv,srlv,srav,jr;

I型指令:addi,addiu,andi,ori,xori,lw,sw,beq,bne,slti,sltiu,lui;

J型指令:j,jal。

本文所提出的CPU设计思路由以下步骤组成。

1.1 根据指令功能及格式设计CPU数据通路

根据指令功能和格式列出完成指令功能所需的部件,用部件关系表将每个部件的数据来源列出,根据关系表用连线将每个部件连接起来,设计该指令的数据通路[10]。每条指令的数据通路单独设计完后,再将所有数据通路合并成总的数据通路。

1.2 根据指令功能和数据通路设计CU

(1) 绘制指令流程图。根据初步设计好的数据通路,把每一条机器指令分解为一系列微操作,并排列为有先后次序、互相衔接的指令流程图。

(2) 编排指令操作时间表。依据各条机器指令的操作流程图,编排指令取指到执行的操作时间表。

(3) 进行微操作综合。按照所有机器指令的操作时间表,把相同的微操作综合起来,得到每个微操作的逻辑表达式。

(4) 画出控制器CU逻辑电路。根据各微操作的逻辑表达式设计CPU控制单元。

2 设计举例

由于31条指令集中的一些指令的数据通路和指令流程具有相似性,只是在指令拓展之后,需要加上相应的数据选择器,以确保数据能正确传输。因此在本文中,仅以部分具有代表性的指令进行分析设计,起到以小见大的作用。

2.1 根据指令功能及格式设计CPU数据通路

取R类型的Addu指令、I类型的lw指令、J类型的j指令进行分析:

2.1.1 Addu指令格式

Addu指令功能:rd←rs+rt , PC←NPC(PC+4)

该指令所涉及到的部件有PC,NPC(完成PC+4),IMEM(指令存储器),RegFile以及ALU。各部件之间数据输入输出关系如表1所示。

表1 Addu指令部件数据输入输出关系

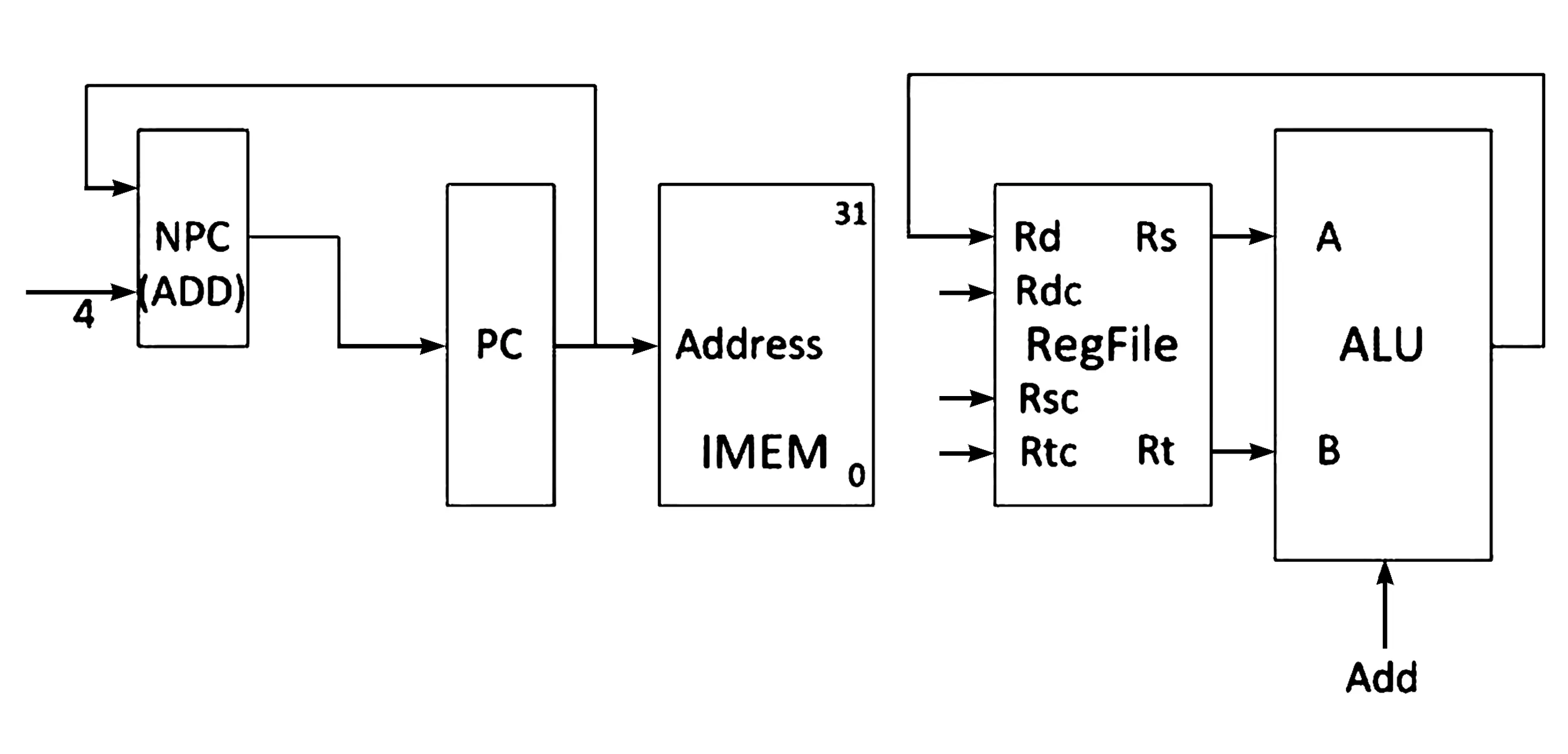

通过对指令功能的分析和数据的传输关系,可以画出如图1所示的Addu指令数据通路:

图1 Addu指令数据通路

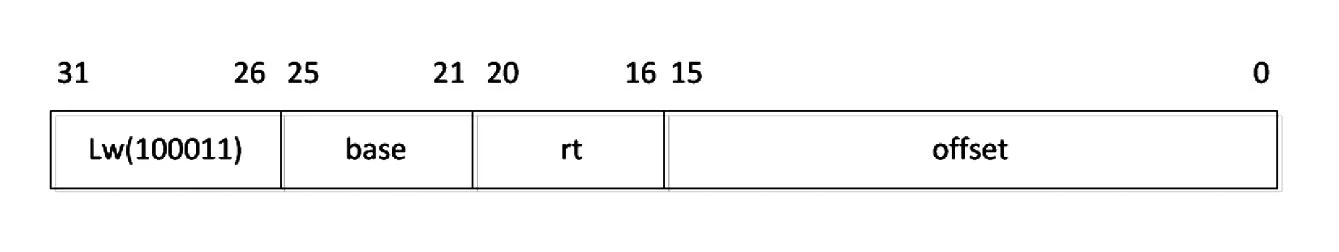

2.1.2 Lw指令格式

lw指令功能:rt ← memory[base+offset],PC←NPC(PC+4)

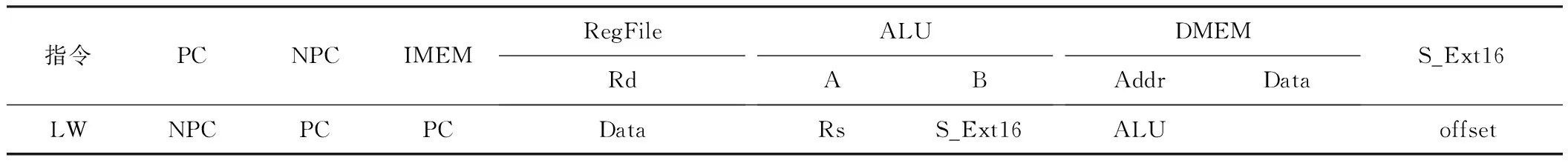

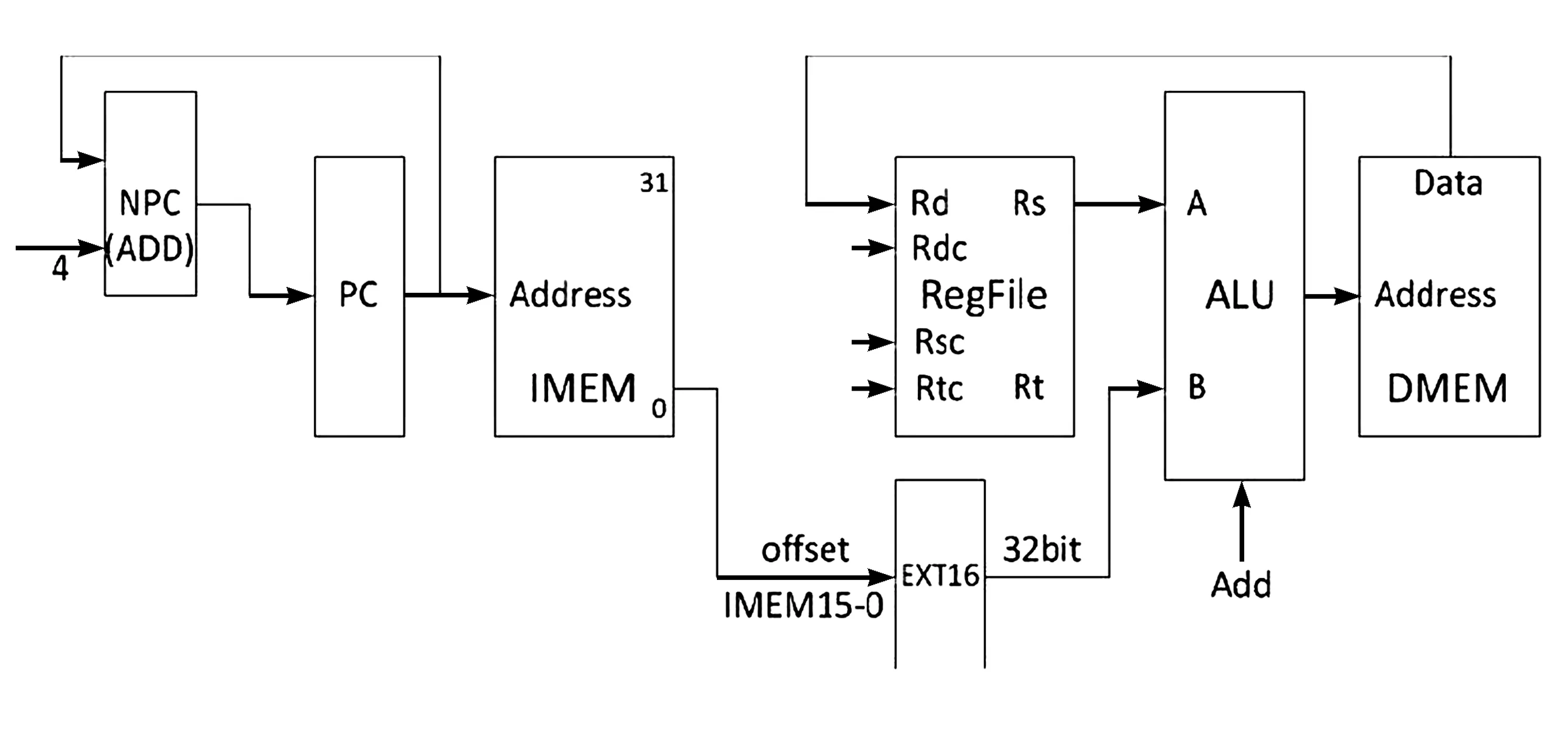

该指令所涉及的部件有PC,NPC(完成PC+4),IMEM(指令存储器)、RegFile、ALU、S_Ext16(将16位二进制符号扩展到32位)和DMEM(数据存储器),部件之间数据输入输出关系如表2所示,数据通路如图2所示。

表2 Lw指令部件数据输入输出关系

图2 Lw指令数据通路

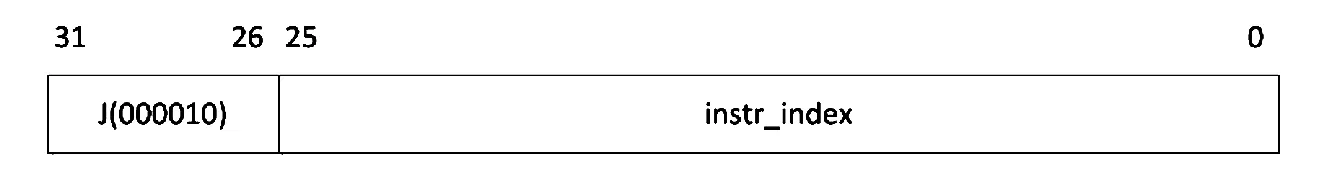

2.1.3 J指令格式

J指令功能:该指令无条件跳转到一个绝对地址,instr_index长度26位,在左移2位后为28位,再与PC的最高4位(PC31-28)并接成32位转移地址。

该指令所涉及的部件有PC、NPC(完成PC+4)、IMEM(指令存储器)和 ||(并接器),部件之间数据输入输出关系如表3所示,数据通路如图3所示。

表3 J指令部件数据输入输出关系

图3 J指令数据通路

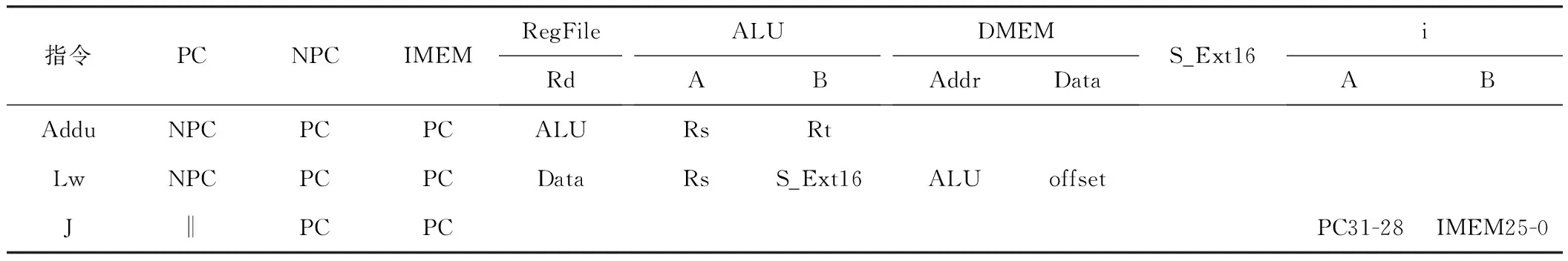

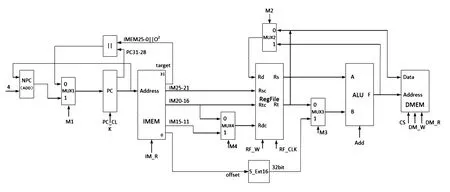

然后合并3条指令的数据通路,先将3条指令的部件关系表合并,如表4所示。某个部件有来自不同部件的输入就用多路选择器,合并的数据通路如图4所示。

表4 3条指令部件数据输入输出关系

图4 3条指令数据通路

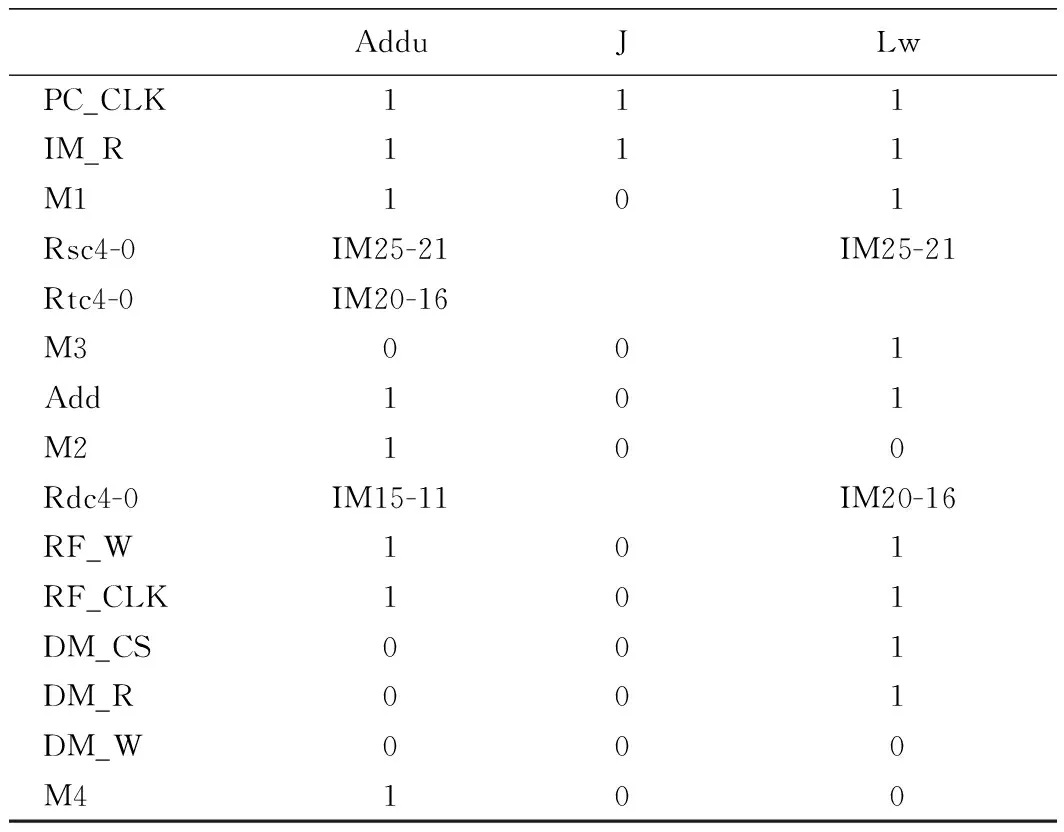

2.2 根据指令功能和数据通路设计CU

2.2.1 绘制指令流程图

获得指令的数据通路图后,可根据指令的运行流程,绘制出指令流程图。在指令流程图中,应标明每一步所需要的信号,这样有助于理清各个信号的作用阶段。图5给出了Addu,Lw以及J指令的指令流程图。

图5 Addu、Lw、J指令流程图

2.2.2 编排指令操作时间表

获得数据通路图和指令流程图后,将所需要的所有信号和寄存器列出,再根据每条指令需要的信号,编排指令操作时间表(假设所有控制信号高电平有效),如表5所示。从表中看到Rdc4-0来自2个输入,所以加1个多路选择器MUX4。3条指令完整的数据通路如图6所示。

表5 指令操作时间表

2.2.3 进行综合微操作

根据第三步(2.2.2节)的操作时间表,可将相同的微操作综合起来,得到每个微操作的逻辑表达式。Addu,Lw,J这3条指令的微操作综合逻辑表达式结果为:

PC_CLK=CLK;

IM_R=1;

M1=Addu+Lw

Rsc4-0= IM25-21;

Rtc4-0= IM20-16;

M3=Lw

Add=Addu+Lw;

M2=Addu

Rdc4-0= IM15-11(Addu)+ IM20-16(Lw);

RF_W=Addu+Lw;

RF_CLK=(Addu+Lw)CLK;

DM_CS=Lw;

DM_R=Lw;

DM_W=0。

M4=Addu

图6 三条指令完整数据通路

2.2.4 画出CPU的CU逻辑电路

根据微操作逻辑表达式可以画出对应的逻辑电路图(逻辑图省略)。

3 CPU验证

通过前述的设计流程,得到了一个CPU的基本框架。通过Verilog语言实现CPU设计,并使用ModelSim仿真工具进行验证CPU的正确性并下板。

3.1 前仿真测试

3.1.1 单条指令功能验证

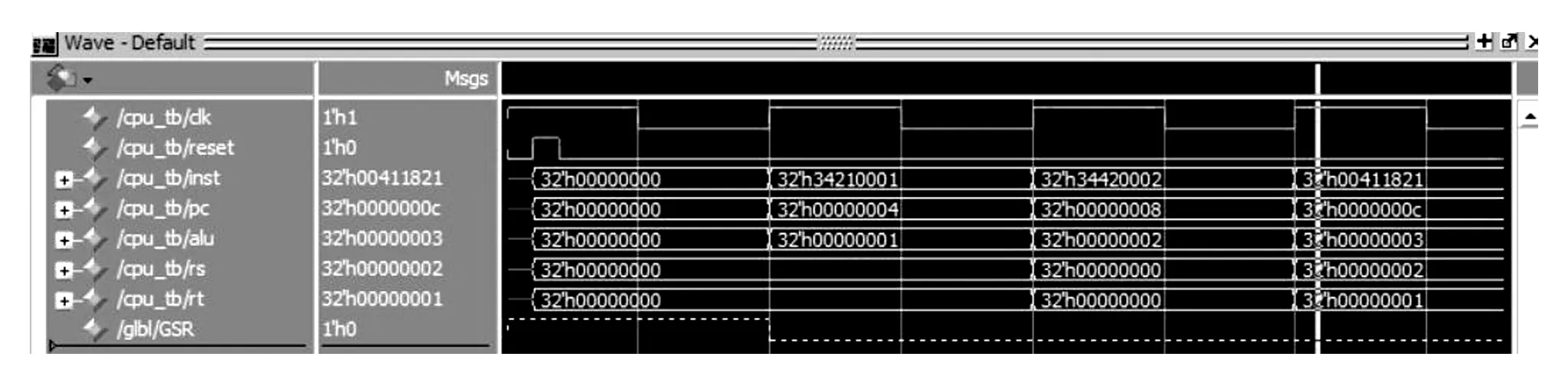

在此步骤中,需要对设计好的CPU进行每条指令功能的验证。将汇编语言编写每一条指令的测试代码,导入CPU的指令存储器,在ModelSim下仿真运行,通过输出波形判断指令执行是否正确。以下举一个简单的例子来说明:

sll $0, $0, 0

ori $1, 0x00000001

ori $2, 0x00000002

addu $3, $2, $1

此汇编指令用于测试Addu指令(假设所用到的Sll指令和Ori指令已经测试通过)。将该指令放入CPU中运行,并使用ModelSim进行仿真后,结果如图7所示,通过输出波形判断指令执行是否正确。

图7 单条指令测试波形

3.1.2 指令边界数据验证

在单指令验证都正确的情况下,还需要对各指令的边界数据进行测试,对CPU进行指令的完备性测试[10]。例如,对Addu指令进行测试时,选取边界数据:0x00000000,0xffffffff,0x0000ffff,0xffff0000,0x0f0f0f0f,0xf0f0f0f0,0x55555555,0xaaaaaaaa等。

多个测试单元可以作为多个测试程序执行,也可以放在一个测试程序中顺序执行。然后将这些指令放入CPU中运行,并用ModelSim仿真,观察波形验证结果的正确性。

3.1.3 随机指令序列验证

在此步骤中,可以自行编写一些符合MIPS规范的指令序列。为了方便结果验证与比较,可先将这些指令序列放入MIPS仿真工具中运行[11],如MARS,获得仿真结果后,再将指令序列放入CPU中运行,将其运行结果与MIPS仿真器中运行的结果进行比较,从而验证CPU功能的正确性。

3.1.4 程序验证

在完成了上面3步验证后,就可以运行一个有意义的程序,观察其运行结果,检测自己的CPU是否正确运行。例如可以使用类似快速排序和斐波拉契数列的程序来验证。

3.2 后仿真测试

时序仿真不同于功能仿真,时序仿真使用布局布线后器件给出的模块和连线的延时信息,在最坏的情况下对电路的行为作出实际的评价[12]。两者的差别在于时序仿真加载到仿真器的设计,包括基于实际布局布线设计的最坏情况的布局布线延时,并且在仿真结果波形图中,时序仿真后的信号加载了时延,而功能仿真没有。

后仿真分为2个步骤,先做指令序列测试,再做程序测试。但是要注意initial块不可综合,后仿真和下板时需要使用ip核初始化iram。如在后仿真出现时序问题时,先采取降低CPU主频的方法来解决,如果不行的话,就必须分析问题所在,修改或优化CPU数据通路或部件。

3.3 下板验证

当仿真验证都通过后,便可使用Vivado工具生成bitstream文件,进行下板验证。使用的开发板为XILINX公司的NEXYS4板。下板前,根据需要设计的功能,在Vivado工程中添加相应的外设代码,N4板可以提供led和7端数码管等外设功能。之后再编写相应的汇编代码通过CPU对外设进行控制,从而验证下板CPU的设计是否正确。

4 结语

本文提出了一种教学用的CPU设计过程,通过对指令功能的分析,设计数据通路图,再到使用集成开发工具编写CPU设计代码,最后进行仿真验证和下

板。这一过程从简单到复杂,从理论到实践,循序渐进,逐步提高。学生通过完成CPU的设计过程,不仅巩固了课本上的知识,还拓展了工程实践视野。本文所提出的实验设计方法,已经在我校数届学生中进行了应用,通过对学生的问卷调查和实验结果的验收统计,学生CPU设计成功率从最开始的不到30%,逐渐提升到了50%,现今已经达到了76%以上。而设计CPU的累计时长,也从最初的34 h以上,下降到如今的25 h左右,取得了良好的效果。

参考文献(References)

[1] 邹惠,王建东. 以CPU设计为核心的“计算机组成原理”课程教学改革探讨[J]. 福建电脑,2016(3):84-85.

[2] 袁春风,陈贵海,黄宜华,等. “计算机组织与系统结构”课程的教学现状和改革思路[J].计算机教育,2009(16):153-156.

[3] 朱凌云. 对计算机组成原理教学的思考[J]. 计算机教育,2011(10):37-39.

[4] 邹惠,王建东,刘坤起,等. “计算机组成原理”课程教学探讨[J]. 工业和信息化教育,2014(12):45-48.

[5] 周刚,师维,陈润,等.计算机组成原理实验创新性改革探索与实践[J].实验技术与管理,2016,33(11):26-29.

[6] 徐爱萍,张玉萍,涂国庆. 基于VHDL之CPU设计与实践[J]. 实验室研究与探索,2014,33(5):120-124.

[7] 黄明,陈龙. 基于MIPS指令的CPU逻辑电路设计[J]. 科技展望,2014(18):100-101.

[8] 王力生,王煜. 计算机组成原理实验教学方法改进[J]. 电脑知识与技术,2014(28):6704-6706

[9] MIPS Technologies, MIPS32TM Architecture For Programmers, Volume I[M]. Introduction to the MIPS32TM Architecture,Revision 0.95,2001.

[10] MIPS Technologies, Inc. MIPS32TMArchitecture For Programmers Volume II[M]. The MIPSTMInstruction Set, 2003.

[11] Lu S, Li G, Wang Y. CPU Design for Computer Integrated Experiment[J]. FECS12, 2012(8):594-600.

[12] 戚新宇. 基于FPGA设计的功能仿真和时序仿真[J]. 航空电子技术,2005,36(3):51-54.