基于软件无线电的通信系统实验平台研制(2)

——片上系统

戴伏生(哈尔滨工业大学(威海) 信息与电气工程学院,山东 威海 264209)

0 引 言

基于类似Unix操作系统,但可自由免费使用的开源无线电软件(GNU’s not Unix Radio,GNU Radio)研制的无线通信系统实验平台,由硬件系统和软件系统组成。硬件系统是指实验平台的物理资源,如现场可编程门阵列(Field Programmable Gate Array,FPGA)、时钟管理器、D/A和A/D、射频接口、网络接口、各种外设接口及电源等。软件系统是指为使用实验平台所配套的管理驱动及应用工具软件,如实验平台的用户硬件驱动配置(User Hardware Driver,UHD)、GNU Radio等软件。实验平台采用了开放化和软件化设计理念,无线电外设平台的管理系统及信息处理等功能模块,全部采用软件驱动配置FPGA的方法构建。在安全模式启动下为实验平台配置了一个精简的片上系统(System on Programmable Chip,SoPC),通过以太网接口实现与上位机通信,该模式不包含用户定制的功能。UHD是为实验平台配置出具有适变功能的完整片上系统。只有将包含用户各种定制功能的UHD镜像文件载入到主板M25P64 Flash中,才能发挥实验平台用户规划的应有作用。

1 硬件驱动的下载与配置原理

1.1 多重启动配置存储方式

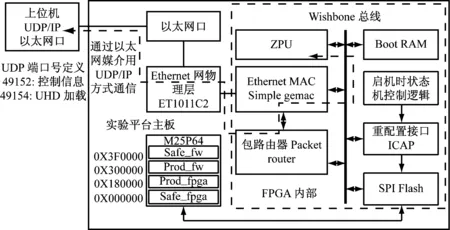

实验平台采用的FPGA是XC3SD3400A,它拥有专用的多重逻辑配置模块及其接口内部配置访问端口(Internal Configration Acces Port,ICAP)[1]。通过控制ICAP接口可以实现对配置存储器的读/写。为了实现多重配置把M25P64 Flash分为4个区存储镜像文件,安全模式启动配置镜像文件占据的2个存储区,考虑能兼容和利用公开的UHD资源[2],构建镜像文件存储区域分配方式,如图1所示。

从0X000000起始地址放置的镜像文件Safe_fpga,是静态安全配置FPGA实体逻辑功能单元,是用Verilog HDL描述的精简片上系统各功能模块镜像文件。从0X3F0000地址起始放置的储镜像文件Safe_fw,是最小处理器(Zylin CPU,ZPU)[3]使用的且受保护的安全程序代码,主要是引导程序、UDP/IP通信及管理程序。

用户硬件设备驱动配置UHD镜像文件占据剩余的2个存储区。从0X180000地址起始放置的镜像文件Prod_fpga,是用户硬件驱动配置FPGA实体逻辑功能单元,是硬件语言描述编译后的映射比特码,包含实验平台需FPGA实现的用户功能全部实体逻辑模块。起始地址0X300000放置的镜像文件Prod_fw,是处理器ZPU执行的用户工作程序代码,包含实验平台管理、通信、接口控制及射频端口控制等。

图1 实验平台中M25P64多重配置镜像文件存储分区情况

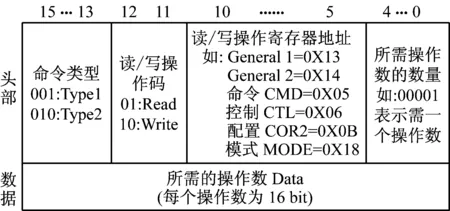

1.2 硬件驱动UHD的下载

若没有从上位机给加载存储M25P64 Flash硬件驱动UHD配置镜像文件,或者开机配置过程中检测安全启动开关控制引脚为低电平时,则只能按照安全模式启动并通知上位机下载配置镜像文件。安全模式启动时,首先从M25P64 Flash的0X000000地址开始读Safe_fpga镜像文件,对FPGA进行逻辑电路系统的配置,然后利用状态机逻辑电路控制内部配置访问端口(Internal Configuration Access Port,ICAP),从M25P64 Flash的0X3F0000地址开始读取Safe_fw镜像文件,把安全模式可执行程序代码配置到Boot RAM中。为了能实现硬件驱动UHD镜像文件的下载,安全模式下实验平台与上位机通信所配置的系统如图2所示。

图2 安全模式下实验平台与上位机通信系统

安全配置之后片上系统开始工作,ZPU便能够实现对系统的控制,所有工作均由ZPU主导,其时钟频率配置为50 MHz,该时钟是由时钟管理器送给FPGA的100 MHz输入,经FPGA内部锁相电路2分频后产生的。图中的包路由器Packet_router逻辑功能模块是用轻量级IPv4协议(Light Weight IP,LWIP)实现的[4,5],所有数据包经由Packet_router发往FPGA中的目的模块。ZPU中运行是LWIP中轻量级UDP/IP协议,其默认的IP地址是192.168.10.2。在与上位机通信前ZPU及片上系统,同上位机之间进行以太网的协议和速率协商与匹配,且注册两个DUP端口号49152和49154与上位机通信。编号49152的UDP端口为控制信息通信端口号;编号49154的UDP端口号,用来实现对实验平台硬件驱动UHD配置进行固件镜像及升级的通信。

由于ZPU是Wishbone总线的主控制器[6-8],所以在上、下位机之间的通信时,路由器模块Packet router与ZPU之间的操作,需要进行Wishbone总线的资源属性设置。上位机给下位机传送数据称为总线“设置资源属性”,反之则称为总线“读取资源属性”。总线“设置资源属性”时,ZPU将路由器模块Packet router设置为写ZPU方式,Packet router对来自以太网的数据包头进行UDP端口识别,当端口号为49152或49154时,把数据送到Wishbone总线。Wishbone总线再把数据传给ZPU,ZPU进行UDP数据解析,进而控制Wishbone总线下的从设备。总线“读取资源属性”时,ZPU将路由器模块设置为读ZPU方式。路由器读取ZPU中的资源信息时,再把数据加上相同的端口号49152或49154包头后,再把数据包通过以太接口发送给上位机。

硬件驱动UHD下载是通过UDP端口49154进行的。当路由器模块Packet router收到UDP端口49154送来的数据时,通过Wishbone总线送给ZPU。ZPU对数据头进行解析,分析是Prod_fpga还是Prod_fw,以及数据大小。再通过Wishbone总线对SPI Flash进行设置,然后把数据写入M25P64 Flash的相应存储单元,最后,ZPU再通过UDP端口号49154向上位机返回应答任务完成情况的信息。至此,便完成了硬件驱动UHD配置镜像文件下载。新下载到M25P64 Flash的UHD硬件驱动Prod_fpga和Prod_fw配置镜像文件,需重启系统后才能使用。

2 UHD配置的片上系统

2.1 实验平台多重启动配置

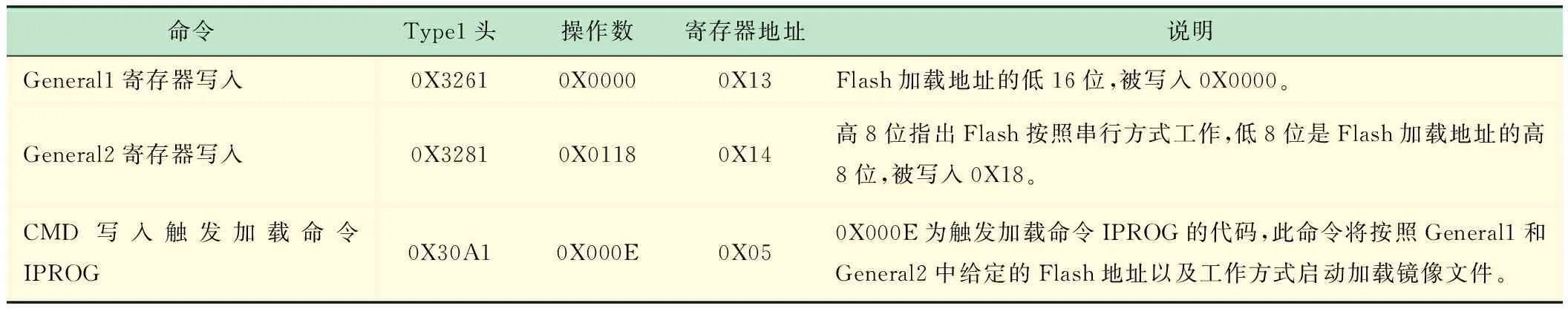

实验平台启动多重配置分为两大模块顺序进行,第一大模块先检测与加载Prod_fpga硬件驱动镜像文件,后检测与加载Prod_fw程序代码固件镜像文件。加载方法是ZPU通过给ICAP写控制字方式启动加载。操作ICAP方法是:首先,按照加载要求对ICAP中模式寄存器MODE REG以及控制寄存器CTL、配置选项寄存器COR2等,进行参数设置。然后,按照常用的Type1命令格式,对ICAP相应的寄存器按照一定顺序进行赋值。Type1命令格式包含头Header和数据Data两部分,如图3所示,实验平台操作ICAP关键命令见表1[4-6]。

图3 对ICAP操作的Type1命令格式

表1 实验平台重配置操作ICAP的Type1格式关键命令

为了利于软件升级,实验平台总是从安全模式开始配置和启动。安全工作模式下,ZPU先将SPI Flash进行初始化设置,进而检测M25P64 Flash中是否存在有效硬件驱动Prod_fpga文件,如果检测到则加载,否则通过以太网把未检测到有效硬件驱动文件通报上位机,并要求上位机下载该文件。检测方法是从M25P64 Flash的0X180000地址起始读取,每次读取16 byte,共读取64 byte。若64 byte为连续的0XAA和0X99,则返回1,表示检测到Prod_fpga,否则返回0。正确检测到存在Prod_fpga后,启动对Prod_fpga镜像文件的加载。

镜像文件的加载时,首先先给ICAP的General1寄存器写入Flash加载地址的低16 bit,操作码为“0X3261 0X0000”。然后再给ICAP的General2寄存器按照Type1命令格式写入SPI操作码及Flash加载地址的高8位,操作码为“0X3281 0X0118”。此时,General2和General1两个寄存器中命令的含义是:从热启动地址WBSTAR为0X180000开始读取Flash内容。最后给ICAP的命令寄存器CMD写入触发加载命令IPROG,操作码为“0X30A1 0X000E”,便从起始地址0X180000读取M25P64 Flash中的配置信息,对FPGA进行重构。

加载Prod_fpga镜像文件重构完成逻辑电路后,继续检测M25P64 Flash中是否存在有效的ZPU程序代码固件firmware,即检测Prod_fw程序代码固件镜像文件。如果检测到则进行加载,否则通过以太网把未检测到程序代码固件信息传给上位机,并要求下载程序代码固件镜像文件。对程序代码固件文件Prod_fw的检测,方法是从M25P64 Flash的0X300000地址起始读取4个byte,并判断是否为连续4个0X0B,若正确则返回1,否则返回0。正确检测到存在Prod_fw后,ZPU通过给ICAP写控制字方式启动对Prod_fw的加载。Prod_fw程序代码固件将被加载到系统存储器Sys RAM中。加载完成后将触发系统控制模块System_control,ZPU系统按照Sys RAM中程序进行重启。之后实验平台提供的通用功能或用户定制功能就能正常使用了。

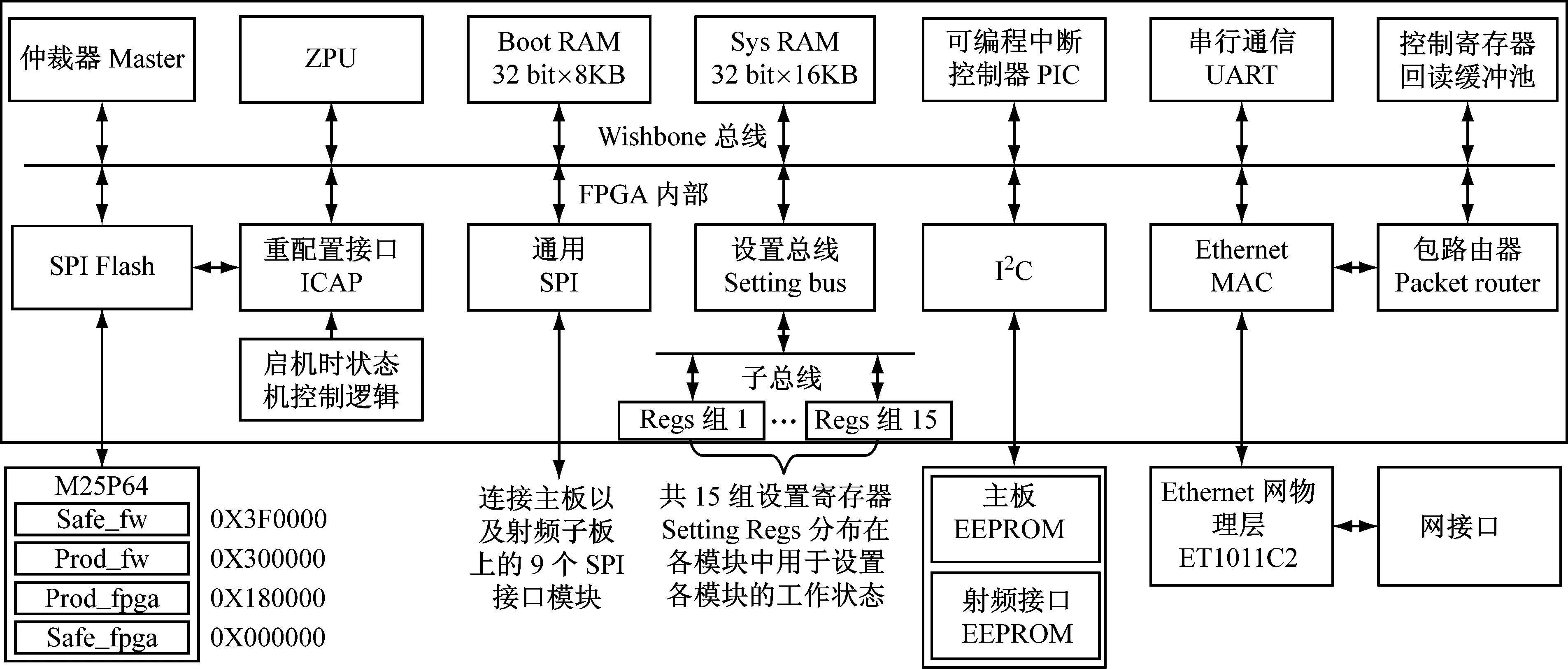

2.2 UHD配置的片上系统

硬件设备驱动UHD配置镜像文件建立的片上系统SoPC部分如图4所示。需要说明的是,在安全模式启动下片上系统就已经配置处理器ZPU、Wishbone总线及总线控制器[9-11]、挂接在Wishbone总线上的专用SPI接口SPI Flash、双端口哈佛型引导程序存储器Boot RAM、内部配置访问端口ICAP和相应的状态机逻辑控制器、可编程中断控制器(Programmable Interrupt Controller,PIC)、数据包路由器Packet router、通用可编程I/O接口(General Purpose Input Output,GPIO)回读缓冲、简化的以太网数据链路媒体层Ethernet MAC等模块。片上系统中的Sys RAM、通用SPI、I2C、设置总线Setting bus及其15个寄存器组、通用可编程I/O接口GPIO回读缓冲等逻辑功能模块,是由硬件设备驱动UHD重配置而完善的。需说明的是:为了使实验平台具有极大的灵活性,在任何情况下都可以重新进行硬件驱动UHD的下载,或者是UHD的升级。

3 UHD配置的功能模块寻址方法

3.1 Wishbone总线功能模块寻址方法

ZPU是实验平台的主控制器,访问各功能模块需要按照一定方式寻址,而挂接在Wishbone总线上的功能模块之下,很多还存在子功能单元,为了使ZPU能够方便地访问到子功能单元,并考虑软件无线电无线设备的VITA-49规范建议,实验平台采用的是地址和掩码方式进行寻址,Wishbone总线挂接的各功能模块地址和掩码如表2所示。

图4 硬件驱动UHD建立的SoPC

挂接在Wishbone总线上的功能模块是按照地址段方式划分与寻址,是通过匹配地址总线的高8位地址方式,使ZPU可以选中功能模块。具体工作原理是:把Wishbone总线上的16 bit地址被分为高8 bit和低8 bit两部分,把高8 bit地址同模块8 bit掩码进行按位“与”运算后,再同模块高8 bit地址按位“异或”运算,若逻辑运算结果为0,则作为片选信号,表明该功能模块的地址段与Wishbone总线给出的地址相匹配,进而接受ZPU的操作。如系统存储器Sys RAM模块地址段为0X0000~0XC000,设置总线Settings bus模块地址段为0X7000~0X7FFF。若要操作到功能模块中的具体子单元,还需Wishbone地址线中的低位地址参加选择。

3.2 子功能单元寻址方法

挂接在Wishbone总线上的功能模块几乎都存在子功能单元,一些子功能单元作用比较单一,如Sys RAM的子功能单元就是存储数据;而一些子功能单元作用比较复杂,涉及到硬件的工作状态,但是不论子功能单元作用如何,其寻址方式相似。Setting bus上挂载了相当多对实时性要求不高的低速设置寄存器组(Setting Regs,SR),如表3所示。

表2 挂接Wishbone总线各功能模块地址和掩码

表3 设置寄存器SR组和组中子单元寄存器数量及子单元的子起始地址

这些寄存器组控制着实验平台系统大部分的工作状态,且Setting bus又承担低速控制总线的作用。因此,为了能说明问题,将以设置总线Setting bus为例介绍子功能单元寻址方法。需要说明的是:实验平台设置总线Setting bus只挂载了低速设置寄存器,而高速设置寄存器并不挂载在Setting bus上,也不需要通过ZPU解析。有关高速设置寄存器问题将在后面另中介绍,此处不再赘述。

当Wishbone地址总线上的地址信号处于0X7000~0X7FFF段时,Setting bus模块被选中,Setting bus模块把Wishbone地址的第9~2 bit连续取出8 bit信号,作为选择挂接Setting bus在子功能单元基组地址的8 bit信号。例如,若要选择设置寄存器SR_GPIO中的SR_GPIO_0,它是设置射频收发为空闲状态的寄存器,又称ATR0寄存器[2],这时只要Wishbone地址总线上给出的地址码为0X72E0,就可以访问该寄存器。在上位机常常以基组地址和偏移量方式指出寻址的寄存器,如寻址DDC_chain0通道模块的设置寄存器,可以用SR_RX_DSP0+0、SR_RX_DSP0+1、SR_RX_DSP0+2、SR_RX_DSP0+3形式寻址,实际地址码为0X72E0、0X72E4、0X72E8、0X72EC,对应可改变DDC_chain0模块中的中心相位、尺度、(半带通1使能+半带通2使能+梳状滤波抽取率)、(选择实数处理+I/Q交叉处理)等参数。

需要注意的是:Setting bus模块把Wishbone地址的第9~2 bit连续取出,作为子功能单元基组BASE地址的8 bit信号,原因是ZPU为8 bit操作命令码,而32 bit长存储器RAM被分为4个区,每个区字长8 bit,一个32 bit长存储器共保存4个ZPU操作命令码,ZPU的程序指针PC利用最低2 bit地址作为取指4个区的定位,以确保连续获得操作命令码。而对于像访问寄存器操作,一次就可进行32 bit存储操作,并不是8 bit操作。因此为了区分Wishbone地址线是ZPU操作,还是对寄存器操作,在对寄存器操作时回避使用最低2 bit地址信号。

4 结 语

所研制的无线电通信系统教学实验平台,采用了开放化和软件化的设计理念,这就需要将硬件的驱动配置镜像文件载入主板配置文件存储器,才能构建出完整功能的无线电片上系统。对硬件设备驱动镜像文件存储方式,多重启动配置工作原理,片上系统组成,挂接在内部总线上的功能模块及其子模块寻址特点与方法等内容,进行了系统介绍。可以看出用软件构建出的无线电工作系统结构呈现层次化和模块化特点。理解实验平台的驱动配置方法,掌握所构建的软件无线电系统结构,不仅有助于对实验平台工作原理的全面理解,而且为进一步灵活地控制实验平台奠定了必要的基础。虽然加载硬件设备驱动镜像文件后并借助GNU Radio正常使用实验平台不存在什么问题,但是若要想充分发挥实验平台提供的资源,尤其是想开发出具有个性化创造性的软件无线电应用,还需要掌握整个系统的控制方式。笔者将继续撰文,对实验平台的系统控制过程及其工作原理进行阐述。

参考文献(References):

[1] FPGA用户手册. XtremeDSP DSP48A for Spartan-3A DSP FPGAs[DB/OL]. http://www.xilinx.com/support/documentation/ user_guides/ug431.pdf.

[2] USRP硬件驱动程序和USRP手册[EB/OL]. http://files.ettus.com/manual.

[3] Zylin CPU资料[EB/OL]. https://github.com/zylin/zpu.

[4] Ethernet MAC资料[EB/OL]. http://www.xilinx.com/support/documentation/ip_documentation/tri_mode_eth_mac/v5_5/pg051-tri-mode-eth-mac.pdf.

[5] Adam D. Design and Implementation of the LWIP TCP/IP Stack[S]. Swedish Institute of Computer Science, 2001.

[6] Wishbone总线资料[EB/OL]. http://opencores.org/cdn/downloads/wbspec_b4.pdf.

[7] 陆洪毅, 戴 葵, 王志英. 基于WISHBONE的SoC接口设计[J]. 计算机工程与科学, 2003, 25(5): 90-92.

[8] 宋廷强, 刘川来, 周 艳. SoC设计中WISHBONE片上总线的设计与开发[J]. 青岛科技大学学报, 24(5): 439-442.

[9] 邹 晨, 周 波, 李 鹏,等. FPGA重配置技术[J]. 航空计算技术, 2012, 42(6):114-117.

[10] 李 平, 吴 晓, 山 寿. 基于SPI FLASH的FPGA多重配置[J]. 现代电子技术, 2013,36(22):127-130.

[11] 刘 钊, 杜永锋, 许知博. 基于Xilinx-Spartan6 FPGA的Multi Boot设计的实现[J]. 电子科技, 2012, 25(3): 28-31.