一种BCD码数/模转换器的设计

华猛 黄伟军 刘传洋 吴晨辉

摘 要: 提出一种8421BCD码输入的CMOS数/模转换器。数/模转换器输入采用8421BCD码并行数字码输入方式,输出采用模拟电压输出的方式,内部电阻网络根据8421BCD码特点进行特殊设计;锁存电路采用时钟控制,极大地抑制毛刺干扰。电路设计是基于0.35 μm CMOS工艺,经HSpice软件和Cadence软件仿真表明,电路工作在3.3 V电压下,8421BCD码数/模转换器的积分非线性误差(INL)最大为-0.48 LSB和微分非线性误差(DNL)最大为-0.39 LSB,优值(FOM)最大为3.96,电路功耗为0.97 mW。

关键词: 8421BCD码; 数/模转换器; CMOS; 内部电阻网络; 时钟控制; HSpice

中图分类号: TN366?34; TP432 文献标识码: A 文章编号: 1004?373X(2018)16?0026?05

Abstract: A digital?to?analog converter of 8421BCD code input is proposed. For the digital?to?analog converter,the parallel digital code 8421BCD code is used as the input mode,analog voltage output is used as the output mode,and the internal resistance network is specially designed according to the characteristics of the 8421BCD code. Clock control is adopted for the latch circuit to greatly restrain glitch impulses. The circuit design is based on the 0.35 μm CMOS process. The results of the HSpice and Cadence software simulation show that the circuit works at 3.3 V voltage,the maximum integral non?linear (INL) error and differential non?linear (DNL) error of the 8421BCD digital?to?analog converter are –0.48 LSB and –0.39 LSB,the maximum figure of merit (FOM) is 3.96,and the power consumption of the circuit is 0.97 mW.

Keywords: 8421BCD code; digital?to?analog converter; CMOS; internal resistance network; clock control; HSpice

随着电子技术的飞速发展,数字信号的使用越来越广泛[1?2]。然而,自然界信号都是模拟信号,机器却只能识别和发出数字信号,所以数/模转换器在混合电路系统中起到关键作用,是连接数字信号与模拟信号的桥梁。当今电子时代有多种多样的数/模转换器[3],根据内部结构可分为加权电阻网络DAC(Digital?to?Analog Converter)、R?2R倒T型电阻网络DAC[4?5]、双极性采样电容DAC[6?7]和单值电流型网络DAC等。比较经典的R?2R结构DAC,具有使用电阻种类少且数量少、结构简单、工作速度快等特点[8]。但是现有的这些数/模转换器结构都是采用二进制输入的方式,然而在人们已经习惯了十进制数的使用,二进制位权由低到高依次为1,2,4,8,16,32,64,128 ……,这不便开发者解读。8421BCD(Binary Coded Decimal)码是人与机器的一个纽带。8421BCD码是将每一位的十进制数都用4位二进制数表示,且这4位二进制的位权依次是8,4,2,1。BCD码已经广泛用于各个领域,在计算机领域的应用中,既可保存数值的精确度,又可减少电脑做浮点运算时所耗费的时间。所以将BCD码应用到DAC中是新的方向[9],不仅灵活简便,还保留了二进制码 0和1低误码率的优点。

二进制数转化为十进制数的方法有多种,主要分为软件转化和硬件电路转化[10?11]。软件的实现方式又分DAA(Decimal Adjust after Addition)调节指令法和算法转换法、查表法等,但是软件转化效率较低,占用资源多,耗时长[12?13]。硬件转化法不占用内存资源但是却存在硬件响应慢、成本大等问题。针对二进制的使用不便和当前所存在的数/模转换器的不足,设计了BCD码数/模转换器,既能保留十进制的简便性又可以直接控制数/模转换电路。

1 BCD码数/模转换器内部电路设计

8421BCD码的数/模转换器是指输入8421BCD码,控制内部数/模混合电路,输出对应的模拟信号,系统整体结构如图1所示。数字信号以BCD码的形式并行输入,由锁存电路进行锁存,进而控制开关电路,形成不同阻抗的电阻网络,最后形成对应的模拟输出。

1.1 最小BCD码阻抗单元

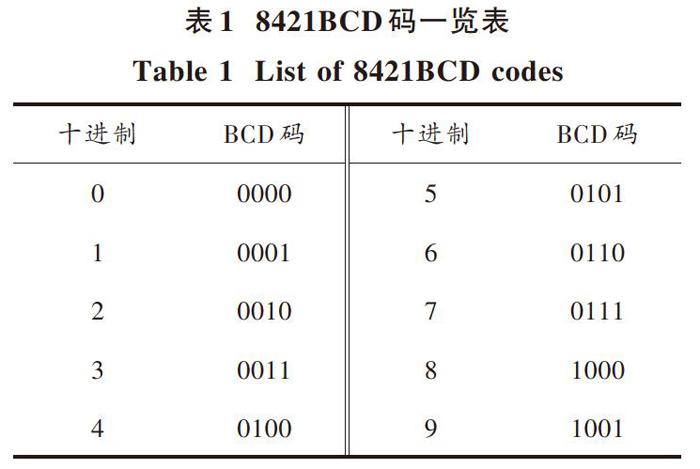

8421BCD码是人们比较熟悉的十进制数的二进制编码表示形式,十进制数的每一位都用四位二进制数表示,见表1,这不仅保留了十进制的简便性还增加了对逻辑电路的灵活控制。图2是最简单的BCD码数/模转换器,也是最小的BCD码数/模转化单元。图中d3,d2,d1,d0分别对应电子开关S3,S2,S1,S0。

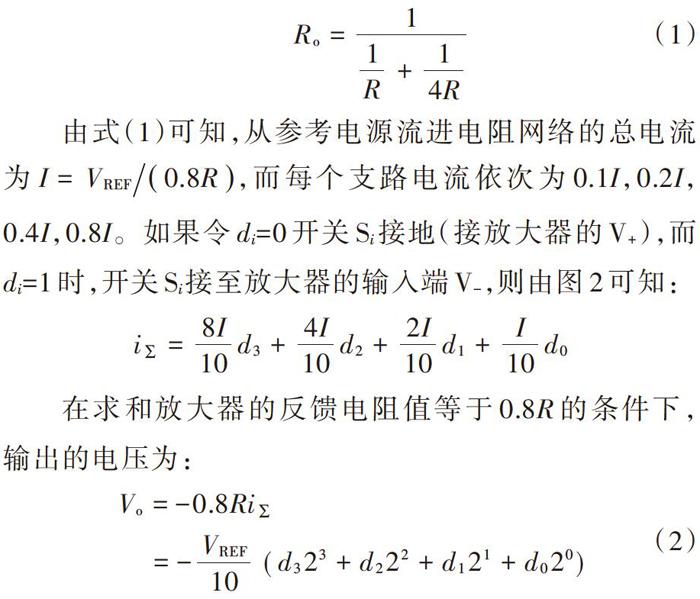

通过表1的8421BCD码一览表,观察得知当最高位为逻辑正时,有且仅有最低位可以为逻辑正,所以对应图2,当d3为1时,开关打到上面选通最大分流值,d2,d1只能为0;此时开关选通到地,电路中电流值为零。开关S3既可以控制最大分流支路,又避免输入的不是BCD码而导致模拟输出过大的错误。根据虚短虚断可知,求和放大器反相输入端V-的电位始终接近于零,所以无论S2,S1,S0导通到任何一端,都相当于连接到了“地”电位上。由此可得等效电路如图3所示。

图3中AA端口的等效电阻为R,串联上一个3R电阻,总电阻为4R; BB和CC端口的等效电阻都是为R;与DD端口的电阻相等。所以不论S3打到哪个支路,流进AA端口的电流与流进DD端口、CC端口的电流比为1∶4∶4。

分析图3等效电路,可计算出VREF与地之间的阻抗为:

1.2 3位BCD码数/模转换电路

文中设计3位BCD码数/模转换器,电路图如图4所示,输入BCD码为(d11d10d9d8_d7d6d5d4_d3d2d1d0)BCD;每4位是一个BCD码,用一级电路实现,当多位BCD码时,由式(1)可知后级电阻网络的总阻抗为0.8R,为保证多级扩展,需要在每级之间加一个1.2R匹配电阻。整个3位BCD码数/模转化器电路中,电阻网络只有4种阻值的电阻,且只有26个电阻,与经典的12位R?2R倒T形电阻网络数/模转换器相比,电阻数量仅多两个。因为输入是十进制数,所以同等模拟开关数量下,精度相对经典的倒T形电阻网络模/数转换器稍差,但是用法简便。在本电路设计中求和放大器的反馈电阻为0.8R,数/模转换器输出的模拟电压的计算公式为:

由式(3)可得,输出的模拟电压与输入的数字量成正比,满足BCD码输入的要求。

1.3 CMOS开关电路分析

开关电路采用的是CMOS开关电路。CMOS开关电路不仅制作成本低,而且占用面积小。图5是CMOS开关电路,Q8,Q9构成一个传输门,Q10,Q11构成一个传输门。由di控制前级CMOS电路驱动两个传输门,当di为高电平时选通Select1到COM,为低电平时选通Select2到COM端。

1.4 控制锁存电路

控制锁存电路主要是将输入的逻辑信号存储起来,使其BCD码数/模转换稳定输出,减小毛刺干扰。控制锁存电路主要由两级反相器和两个传输门组成,并且传输门由CP时钟信号控制,实现对输入数字信号的锁存。如图6所示是控制锁存电路图。

图6中两传输门由CP时钟信号控制,当CP为低电平时,传输门导通,Vin可以传输到Vout,反之,CP为高电平时,传输门关闭,Vin无法传输到Vout。整个系统都由同一个时钟控制,保证信号的同步性,极大地抑制电路由时延产生的毛刺现象。

2 仿真及结果分析

本设计采用HSpice软件作为电路模拟仿真及结果分析的软件工具。HSpice使电路级性能分析变得容易,具有良好的收敛性和精确的模型。HSpice不仅可以对集成电路进行交流分析、直流分析、瞬态分析,还可以对电路的性能进行多参数优化,具有多重仿真的AvanWaves 交互式波形图分析等功能,是目前集成电路设计中比较简便、快捷、效果显著的一款模拟仿真软件。

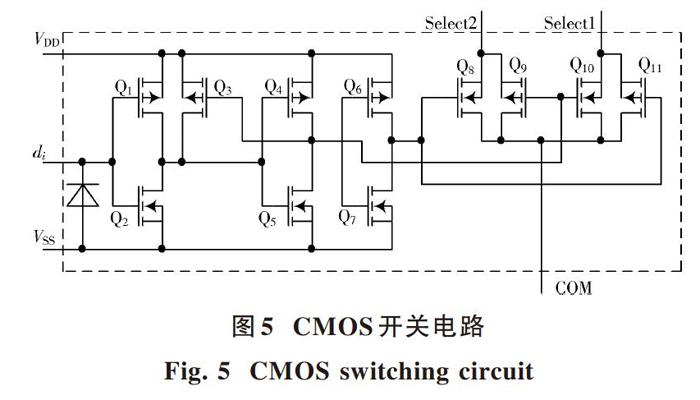

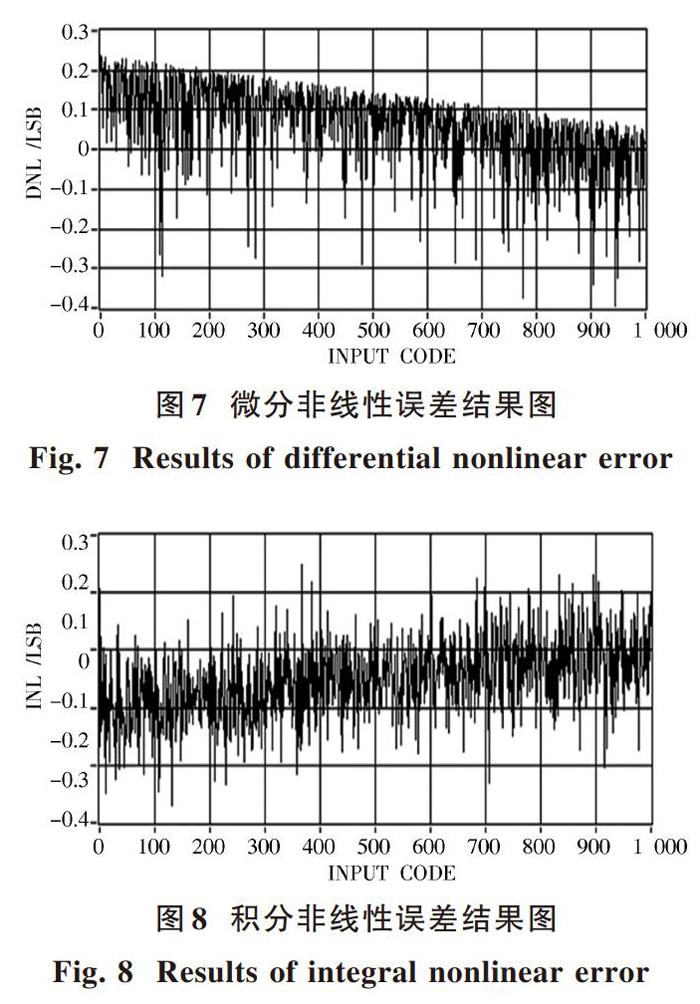

软件仿真主要分析了数/模转换器非常重要的性能。参数指标:微分非线性误差DNL和积分非线性误差INL。微分非线性误差又称为差分非线性误差,是指数/模转换器相邻刻度之间最大差值,体现数/模转换器的精度高低。积分非线性误差是输出值偏离线性理论值的最大距离,主要体现出数/模转化器的线性度的优劣。图7是用HSpice软件仿真的微分非线性误差结果图,微分非线性误差最大为-0.39 LSB。图8是积分非线性误差结果图,积分误差最大是-0.48 LSB。

圖9是电路采用0.35 μm CMOS工艺[14?16],根据Layout的设计规则,使用Cadence软件做的3位BCD的DAC的版图设计,版图面积大约为0.093 mm2,符合版图设计面积小的原则。

表2是本文设计的BCD码DAC与近年所提出DAC的性能对比表,其中,优值(FOM)表示数/模转换器在功耗、面积和分辨率之间的关系。FOM是衡量数/模转换器优劣的重要参数,单位为J·bit-1·mm2,公式为:

由表2可得,本文设计的BCD码数/模转换器在缩小面积和功耗控制上具有一定优势。

3 结 论

本文设计一种性能良好的BCD码数/模转换器,并采用HSpice模拟仿真电路进行仿真测试。仿真结果表明设计的BCD码数/模转换器正常工作的微分非线性误差小于0.39 LSB,积分非线性误差小于0.48 LSB,版图面积大约0.093 mm2,供电为3.3 V时,转换时钟频率为2 MSPs的情况下,功耗为0.97 mW,优值为3.96 J·bit-1·mm2。所设计的数/模转换器内部阻抗网络使用电阻少,电阻种类少,降低了制作难度。版图面积较小,功耗性能好,并且编码输入3位8421BCD码,充分发挥了8421BCD码的操作简便的优势。总体上效果良好,设计满足要求。

参考文献

[1] XIE L,SU J,LIU J,et al. Energy?efficient capacitor?splitting DAC scheme with high accuracy for SAR ADCs [J]. Electronics letters,2015,51(6): 460?462.

[2] SEO D. A heterogeneous 16?bit DAC using a replica compensation [J]. IEEE transactions on circuits and systems I: regular papers,2008,55(6): 1455?1463.

[3] 蔡舟,张涛.一种不同缩放類型组合的低功耗DAC[J].微电子学,2016,46(6):726?730.

CAI Zhou, ZHANG Tao. A low power DAC with different scaling types of combination [J]. Microelectronics,2016,46(6): 726?730.

[4] MARCHE D,SAVARIA Y. Modeling R?2R segmented?ladder DACs [J]. IEEE transactions on circuits and systems I: regular papers,2010,57(1): 31?43.

[5] MARCHE D,SAVARIA Y,GAGNON Y. An improved switch compensation technique for inverted R?2R ladder DACs [J]. IEEE transactions on circuits & systems I: regular papers,2009,56(6): 1115?1124.

[6] 黄兴发,赵建明,邹铮贤.一种10 bit电流型DAC电流源晶体管的抗失配设计[J].现代电子技术,2006,29(8):110?112.

HUANG Xingfa,ZHAO Jianming,ZOU Zhengxian. A mismatching tolerant switching scheme for a 10?bit current?steering DAC [J]. Modern electronics technique, 2006, 29(8): 110?112.

[7] GADDAM R S,LEE K S,KWON C K. A 10?bit dual?plate sampling DAC with capacitor reuse on?chip reference voltage generator [J]. Microelectronics journal,2013,44(6): 511?518.

[8] 李娅,万辉.一种新颖的R?2R电阻网络[J].微电子学,2014,44(6):727?730.

LI Ya, WAN Hui. A new R?2R resistor network [J]. Microelectronics, 2014, 44(6): 727?730.

[9] 宋立双.对8421BCD码D/A转换器的进一步认识[J].电测与仪表,1997(9):54.

SONG Lishuang. A further understanding of the 8421BCD code D/A converter [J]. Electrical measurement & instrumentation,1997(9): 54.

[10] 陈龙,樊晓桠.BCD码和二进制码转换的硬件实现[J].微电子学与计算机,2005,22(4):42?44.

CHEN Long,FAN Xiaoya. Hardware converter between binary and BCD [J]. Microelectronics & computer, 2005, 22(4): 42?44.

[11] JUANG T B,CHIU Y M. Fast binary to BCD converters for decimal communications using new recoding circuits [C]// Proceedings of International Symposium on Integrated Circuits. Singapore: IEEE,2015: 188?191.

[12] BHATTACHARYA J,GUPTA A,SINGH A. A high performance binary TO BCD converter for decimal multiplication [C]// Proceedings of International Symposium on VLSI Design Automation and Test. Taiwan: IEEE,2010: 315?318.

[13] AL?KHALEEL O,AL?QUDAH Z,Al?KHALEEL M,et al. Fast and compact binary?to?BCD conversion circuits for decimal multiplication [C]// Proceedings of IEEE 29th International Conference on Computer Design. Amherst: IEEE,2011: 226?231.

[14] BAEK S Y,LEE J K,RYU S T. An 88?dB Max?SFDR 12?bit SAR ADC with speed?enhanced ADEC and dual registers [J]. IEEE transactions on circuits & systems II: express briefs,2013,60(9): 562?566.

[15] GADDAM R S,LEE K S,KWON C K. A 10?bit dual?plate sampling DAC with capacitor reuse on?chip reference voltage generator [J]. Microelectronics journal,2013,44(6): 511?518.

[16] LIOU C Y,HSIEH C C. A 2.4?to?5.2 fJ/conversion?step 10b 0.5?to?4 MS/s SAR ADC with charge?average switching DAC in 90 nm CMOS [C]// Proceedings of IEEE International Solid?State Circuits Conference Digest of Technical Papers. San Francisco: IEEE,2013: 280?281.