一种低漏电电源钳位电路的设计与研究

刘瑞雪

(郑州外国语新枫杨学校,河南 郑州 450000)

0 引言

随着科技的发展,晶体管的特征尺寸越来越低,如今,10nm的芯片已经开始在手机端使用了,集成了30亿颗的晶体管。然而,尺寸越小,晶体管的栅氧化层越薄,抗静电冲击的能力就越低。每年因为静电放电(Electro-Static Discharge,ESD)原因,导致芯片损坏的金额高达500亿美元。如图1所示,当人体通过摩擦,积累了一定量的静电荷,当人体触碰芯片时,电荷从人体转移到芯片上。若没有进行静电的导流,那么静电流最终会从芯片的某个引脚进,从某个引脚出,即静电流贯穿整个芯片内部。通常,人体积累的静电荷可以达到数千伏特,短时间内在芯片引脚上,引发的静电流可高达数安培,足以将芯片的栅氧化层击穿,造成芯片永久的失效。因此,研究学者引入了电源钳位电路,目的是为了在静电冲击到来时,让静电电流从电源钳位电路这条路径进行泄放,避免了电流流向芯片内部,从而减缓芯片受静电冲击的影响。此外,为了节省高昂的版图面积,通常采用晶体管来充当电容,即MOS电容。然而,受工艺影响,传统MOS电容的栅氧化层的泄漏电流较大。因此,本文将探究导致MOS电容漏电的原因,并通过电路的设计,克服MOS电容的栅氧泄漏电流。

1 传统电源钳位电路的设计

传统结电源钳位电路通常分为探测单元与触发泄放单元,如图2所示。本文,探测单元由电阻和MOS电容构成,可以调节探测单元等效的时间常数值来区分电源正常上电和静电冲击事件。通常,电源正常上电情况下,电压脉冲的上升时间为ms数量级,而静电冲击下,电压脉冲的上升时间则较快,为ns数量级。因此,我们可以设计探测单元等效的RC时间常数为us数量级,即可探测出静电事件是否发生。此外,反相器和大尺寸的NMOS晶体管构成了触发泄放单元。

在静电冲击到来时,MOS电容来不及充电,此时节点A呈现低电平,通过一级反相器作用,Vg节点为高电平(即NMOS管的栅极为高电平),晶体管开启,从而形成一条低阻的泄放通道,进行电流的泄放。

当正常上电情况下,由于电源脉冲上升时间比RC时间常数大,因此,MOS电容能够被及时充满电荷,其电压与电源电压同步增长。因此,节点A一直维持在高电平,经过一级反相器,Vg节点被晶体管Mn1下拉至低电平,此时晶体管Mbig处于关闭状态,不会影响芯片的正常工作。然而,实际中,由于受工艺的影响,由晶体管构成的MOS电容,将会导致一定的栅氧泄漏电流,MOS将造成部分电压差,因此节点A的幅值不会等于电源电压,因此Vg无法被严格下拉到低电平,从而造成Mbig亚阈值漏电,由于Mbig晶体管尺寸较大,因此,亚阈值漏电较大,通常达到uA数量级,远不能被人们所接受。

图1 静电放电冲击芯片电流流向示意图

2 新型低漏电电源钳位电路的设计

通过查询文献,了解到MOS电容泄漏电流主要由栅极与衬底的电压差决定。本文进行了如图3所示的仿真验证。如仿真所示,中芯国际65nm 1.0V的NMOS管(W=35um,L=25um)构成的MOS电容,其两端压差小于0.3V,栅氧化层的漏电几乎可以忽略不计。随着,压差的上升(大于0.3V),泄漏电流呈现较大幅度的上升,在1.0V压差下,达到了24.5uA的泄漏电流。因此,减少MOS电容泄漏电流最有效的办法是控制其两端的压差低于0.3V。

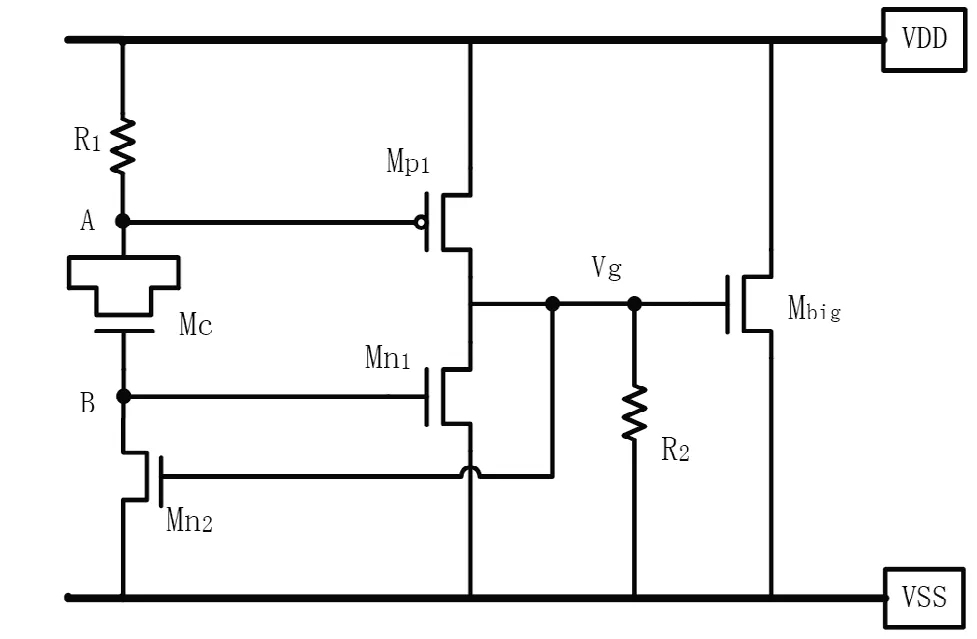

基于上述的分析,本文设计了一款新型低漏电电源钳位电路,如图4所示。下面详细分析其工作原理。

在静电冲击下,由于MOS电容来不及充电,因此节点A处于高电平,Vg节点一方面被晶体管Mp1上拉至高电平,一方面被电阻R2下拉至低电平,由于Mp1的上拉能力更强,因此Vg处于高电平,此时Mbig泄放晶体管开启,开始静电流的泄放。同时,反馈管Mn2也开启,将节点B下拉至低电平,晶体管Mn1处于关闭状态。在整个静电冲击过程中,泄放晶体管Mbig一直维持在开启状态,保证了芯片不会受静电流的冲击。此外,在静电冲击事件结束时候,Mbig栅极将会被电阻R2下拉至低电平,从而保证在静电冲击完成后,电源钳位电路恢复到最初的状态,即Mbig管处于严格关闭状态。

图2 传统MOS电容构成的电源钳位保护电路

图3 MOS电容泄漏电流随两级压差的变化情况

图4 新型低漏电电源钳位电路

在正常上电下,一方面,节点A跟随电源电压同步增长,一方面由于电阻R2的下拉作用,使得Mn2处于关闭状态,MOS电容持续累积电荷。因此,节点A处于高电平,此时Mp1关闭,Vg节点无法被上拉至高电平,因此,Vg节点主要由R2下拉所控制,处于低电平。同时,由于Mn2无法将B节点下拉至低电平,因此慢慢累积电荷的MOS电容使得B节点为高电平,此时,Mn1晶体管开启,Vg进一步被下拉至低电平。整个回路处于一个正反馈状态,Vg节点电压越来越低,B节点电压越来越高。因此,稳定下,节点A与节点B的电压差将达到极小值,因此MOS电容的泄漏电流将会得到极大的改善,同时,泄放晶体管Mbig的栅端达到了极小值,大大减小了在正常工作下的亚阈值漏电电流。

3 Hspice仿真结果

采用Hspice分别对传统电源钳位电路和新型电源钳位电路进行仿真,两个电路的参数情况见表1。

表1 传统和新型电源钳位电路仿真参数表

图5 传统和新型电源钳位电路在正常上电下各节点电压情况

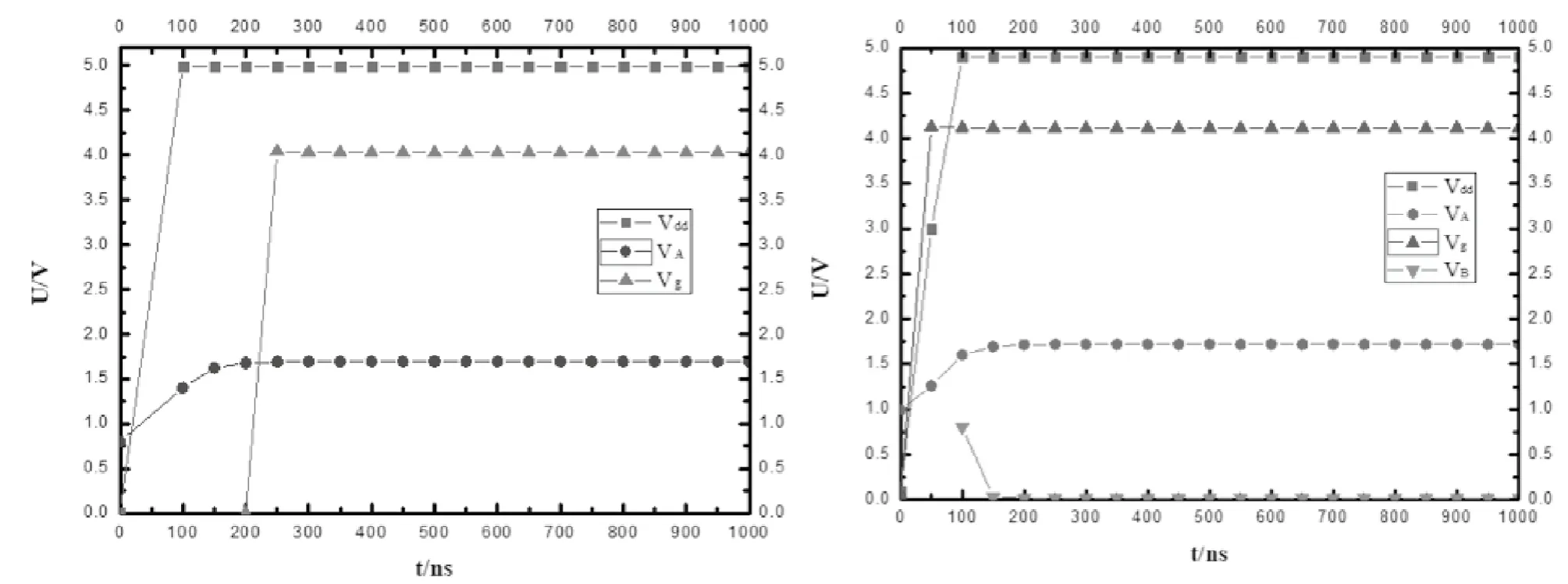

3.1 正常上电仿真

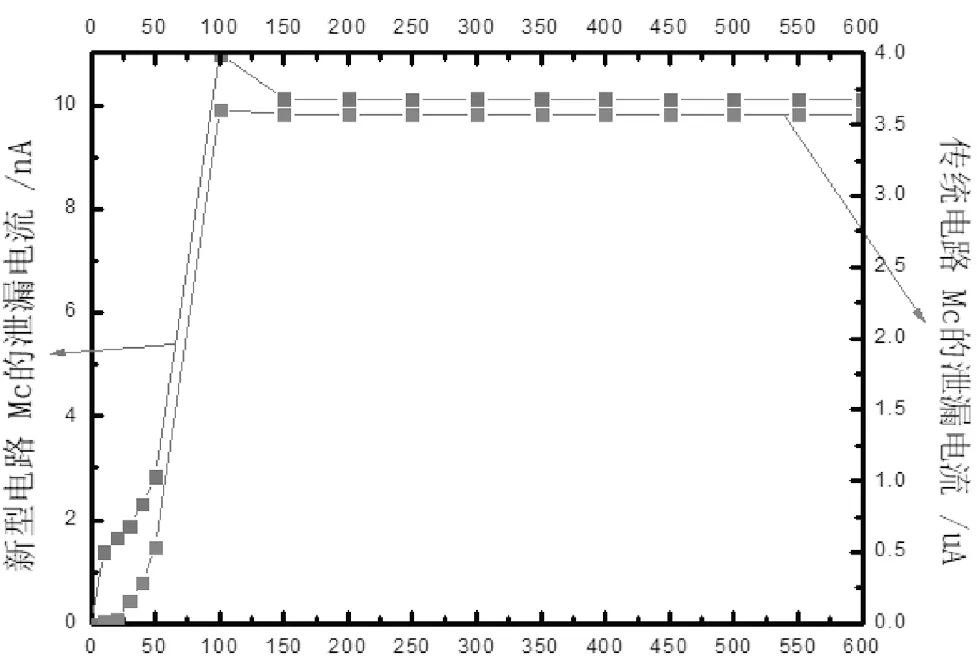

采用上升时间为0.1ms,幅值为1V的电压脉冲来模型电源正常上电事件。如图5所示,左图为传统电源钳位电路,右图为新型低漏电电源钳位电路。实验结果与理论分析一致,即在正常上电情况下,整个过程中,两个电路Mbig的栅极Vg节点均处于低电平,泄放晶体管处于关闭状态。区别在于,传统电源钳位电路,MOS管的下级板为0V,上级板为A节点的电压,压差约为0.8V,MOS电容的漏电电流达到3.61μA,如图6所示。而,新型低漏电电路,由于引进了反馈晶体管Mn2,从而抬高了MOS电容的下极板的电压,即为节点B的电压0.79V,上级板的电压为A节点的电压,为1.0v,MOS电容两端的压差仅为0.21V。根据图7所示,MOS电容的泄漏电流仅为9.98nA。

图6 传统和新型电源钳位电路MOS电容的泄漏电流情况

3.2 静电冲击仿真

采用上升时间为10ns,幅值为5V的电压脉冲模拟静电冲击事件。如图7所示,左图为传统电源钳位电路,右图为新型低漏电电源钳位电路。从图中可以看出,整个静电冲击过程中,两个电路泄放晶体管Mbig的栅极电压Vg均大于4.0V,处于高电平状态,保证了泄放晶体管维持在开启状态,进行静电荷的泄放。此外,所提出的新型泄漏电流,Vg节点电压还略高于传统电路,因此,相同时间下,新型电路Mbig泄放的静电荷会更多。

图7 传统和新型电源钳位电路在静电冲击下各节点电压情况

结语

本文提出的新型低漏电电源钳位电路克服了传统MOS电容受工艺影响导致的栅氧泄漏电流,根据hspice仿真结果显示,MOS电容的泄漏电流仅为9.98Na。因此,本文提出的新型电路对芯片静电保护低漏电方向的设计提供了一种了良好的思路。