一种带有加解密功能的数据摆渡模块设计

,,,

(南京南瑞集团公司,南京 211100)

引 言

在两个不同安全防护等级网络之间交换数据最常用的方法是使用网络隔离装置对数据以非网络传输的方式进行数据传输。传统网络隔离装置的基本结构是两个完全独立的主机系统加一个数据摆渡模块。为了进一步增加数据摆渡的安全性,目前新兴的网络隔离装置的基本结构在传统网络隔离装置的基础上增强了加解密功能,首先对数据进行加解密处理,再对数据进行摆渡。网络隔离装置中数据加解密的性能和数据摆渡的性能直接决定了整个系统的性能。

现有的数据摆渡模块一般有电子开关、单向FIFO、光纤和使用协处理器(FPGA等)摆渡数据4种方式,目前应用最广泛的是使用协处理器的方式。对数据的加密功能则主要有在主机系统上通过软件实现数据加密、分离的加解密模块这两种方式。

软件实现的加密方式在安全性方面有隐患,且加解密性能对主机系统的性能有很大的依赖性。分离的加解密模块一般做成一块独立的加密卡,加密卡上的核心器件主要包括协处理器和密码芯片等,一般通过PCI/PCIe接口和主机进行数据交换,通过密码芯片对数据进行加解密处理。

分离的加密模块提高了系统的安全性,但与传统的网络隔离装置相比,增加了分离加密模块的隔离装置,在数据摆渡之前首先要将数据通过PCI/PCIe接口写入到加解密模块进行加解密处理,加解密完成后的数据返回到主机系统,主机系统再将加解密完成后的数据写入到摆渡模块进行数据摆渡,在性能上打了折扣,同时还要额外占用主机系统的一个PCI/PCIe接口和CPU资源,增加了硬件成本。

本文以XILINX公司的XC7A100T系列 FPGA为硬件平台,利用FPGA的并行性[1]特点,设计了一款带有加解密功能的高速数据摆渡模块,在保证系统安全性的基础上,提高了数据加解密和传输的性能,同时降低了整个系统的硬件成本。

1 硬件方案设计

如图1所示,本设计选用了两片XILINX公司的XC7A100T FPGA芯片作为数据处理核心,数据摆渡模块与主板之间采用PCIe接口通信。XC7A100T FPGA芯片该最多支持一个PCIe x4 Lane核,每个Lane线速为5 Gbps。

为了提高数据传输速率,降低摆渡模块PCB硬件设计的难度,摆渡模块的两块FPGA之间通过FPGA I/O口自带的SERDES资源实现的高速串行接口进行数据通信,与传统的并行接口相比,利用FPGA内部SERDES资源实现的高速串行接口具有速度快、传输距离远、占用芯片引脚少的优点。此外还利用FPGA的并行性特点,采用流水线的方式处理数据包,进一步提高了数据处理的速度。

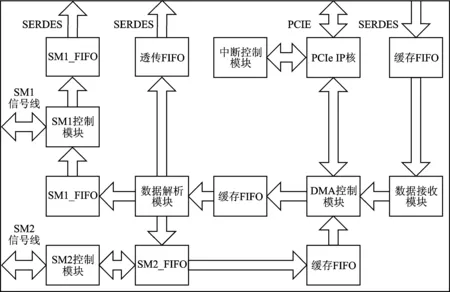

图2 摆渡模块FPGA逻辑架构框图

为了满足网络隔离装置对数据加解密性能的要求,本文设计的数据摆渡模块选用了北京宏思电子技术有限责任公司公司的SSX30-D密码芯片以及北京华大信安科技有限公司的IS32U320A密码芯片作为数据加解密处理及身份认证、密钥协商的核心模块。

SSX30-D为高性能分组密码算法芯片,实现了SM1(原名SCB2)密码算法,性能最高为1.4 Gbps,在摆渡模块中主要用作数据的加解密处理, IS32U320A芯片提供多种硬件协处理器及其配套安全算法库,支持 RSA、SM2、SM3、SM4等密码算法,在数据摆渡模块中主要用作密钥协商和身份认证。数据摆渡模块硬件系统示意图如图1所示。

图1 数据摆渡模块硬件系统示意图

在硬件电路设计上,FPGA芯片XC7A100T具有BGA484封装,扇出的信号较多,此外还需要1 V、1.2 V、1.8 V、3.3 V等多种电平标准,PCIe接口的差分对走线对PCIe信号的完整性要求较高。基于以上因素,本文设计的数据摆渡模块采用了8层PCB板设计方案,从顶层到底层依次为信号层1、地平面1、信号层2、地平面2、信号层3、电源层1、电源层2、信号层4;同时对PCIE的差分对信号以及SSX30-D的数据总线做了等长处理。

2 数据摆渡模块程序设计

2.1 FPGA内逻辑电路设计

本设计使用XILINX公司的Vivado软件开发摆渡模块FPGA器件的逻辑程序,FPGA内逻辑程序设计主要包括:PCIe IP核的定制设计、DMA控制器的设计、数据解析模块的设计、SSX30-D密码芯片控制模块的设计、IS32U320A密码芯片控制模块的设计、数据接收模块的设计、中断控制模块的设计等,FPGA内逻辑架构框图如图2所示。

在PCIe数据通信中,有两种数据传输方式: DMA(Direct Memory Access)和PIO(Programmed Input-Output)[3]。在DMA模式下,数据传送不是由CPU负责处理,而是由一个特殊的处理器DMA控制器来完成,因此占用极少的CPU资源。在PIO模式下,数据传送由CPU执行I/O端口指令来按照字节或更大的数据单位来处理,占用大量的CPU资源,数据传输速度也大大低于DMA模式[4]。

本设计采用两者相结合的方式,在DMA控制器中兼容了PIO控制器,通过PIO控制器将主机系统内存中DMA[2]读写的起始地址写入PCIe BAR空间, DMA控制器根据BAR空间中的地址主机系统内存中的数据读入到FPGA中的FIFO中缓存,再将FPGA处理完成的数据写入到主机系统内存中。

方:您在从事分编工作数年后又改换为情报检索服务工作,并且发表了不少相关研究成果。您能简要介绍一下其中发生转变的情况吗?

数据解析模块主要将FIFO中缓存的数据进行解析,并根据包头字段定义的格式将数据包分别写入到不同的下级FIFO中缓存,下级FIFO主要包括明文透传FIFO、SM1缓存FIFO、SM2缓存FIFO三种,明文透传FIFO中缓存的数据包直接通过FPGA内的SERDES接口传输到另外一块FPGA;SM1缓存FIFO中缓存的数据包在SSX30-D密码芯片控制模块的控制下,写入到SSX30-D密码芯片进行加解密处理,处理完成后的数据包再通过FPGA内的SERDES接口传输到另外一块FPGA;SM2缓存FIFO中的数据包在IS32U320A密码芯片控制模块下写入到IS32U320A芯片内部进行处理,处理完成后的数据返回到FPGA并通过DMA控制器写入到主机系统内存中。

数据接收模块主要负责接收另外一块FPGA传输过来的数据,并写入到接收FIFO中缓存,DMA控制器读取接收FIFO中的数据并通过PCIe接口写入到主机系统内存中。

中断控制模块主要负责发送中断到主机系统,通知主机系统读取数据,PCIe设备的中断方式主要有传统中断、MSI中断两种方式[5]。传统中断为电平触发,MSI中断为边沿触发,一个PCIe设备最多支持4个传统中断,MSI中断方式最多可以达到32个。本设计使用MSI中断方式,并能根据主机系统的CPU核个数动态调整中断数目,在每个CPU的核上绑定一个MSI中断,使得CPU资源的使用更加均匀。

2.2 数据摆渡模块驱动程序设计

网络隔离装置的系统一般为Linux,数据摆渡模块的Linux驱动程序的核心是DMA部分的设计。本设计的DMA部分在借鉴了PCIe网卡的驱动架构基础上设计了更适合自己的一套DMA架构。首先在驱动程序的初始化模块(probe)中申请两块DMA缓存区,一块作为发送描述符缓存区,一块作为接收描述符缓存区。两块缓存区中分别存放了数百个DMA描述符,并分别为每个描述符申请对应的数据DMA缓存区。描述符的结构体定义如下:

struct dma_desc {

u32 sa; //数据缓存区对应的源地址

u32 da; //数据缓存区对应的目的地址

u32 length; //数据缓存区中的数据长度

u32 status; //描述符的状态

u32 next; //下一个描述符的地址

};

DMA分为两个过程:数据从系统内存搬运到FPGA和数据从FPGA搬运到系统内存。数据从系统内存搬运到FPGA过程如下:用户首先将数据写入到发送描述符对应的数据缓存区,并将数据的长度写入描述符的length变量中,通过PIO模式将描述符的起始地址写入到数据摆渡模块FPGA内的PCIe BAR空间中。FPGA内的DMA控制器根据BAR空间中描述符的起始地址启动DMA,将描述符读入到FPGA,再根据描述符中的内容,将描述符对应的数据缓存区中的数据读入到FPGA,最后通过DMA更新主机系统中描述符中的status状态值。用户通过status状态值可确定DMA过程是否结束。

数据从FPGA搬运到系统内存的过程与之有所区别,驱动在加载时,将接收描述符缓存区的地址通过PIO模式写入到BAR空间,FPGA中有数据待传输到主机系统时,DMA控制器首先根据BAR空间中接收描述符的地址将描述符读入到FPGA,并根据描述符中的内容将数据传输到主机系统中描述符对应的数据缓存区,并更新描述符中的status状态值。最后通过中断通知主机,主机接收到中断后,通过描述符中的status状态值判别哪些描述符对应的数据缓存区有数据可读,将数据读走后恢复描述符中的status状态值。

3 实验测试

3.1 实验环境

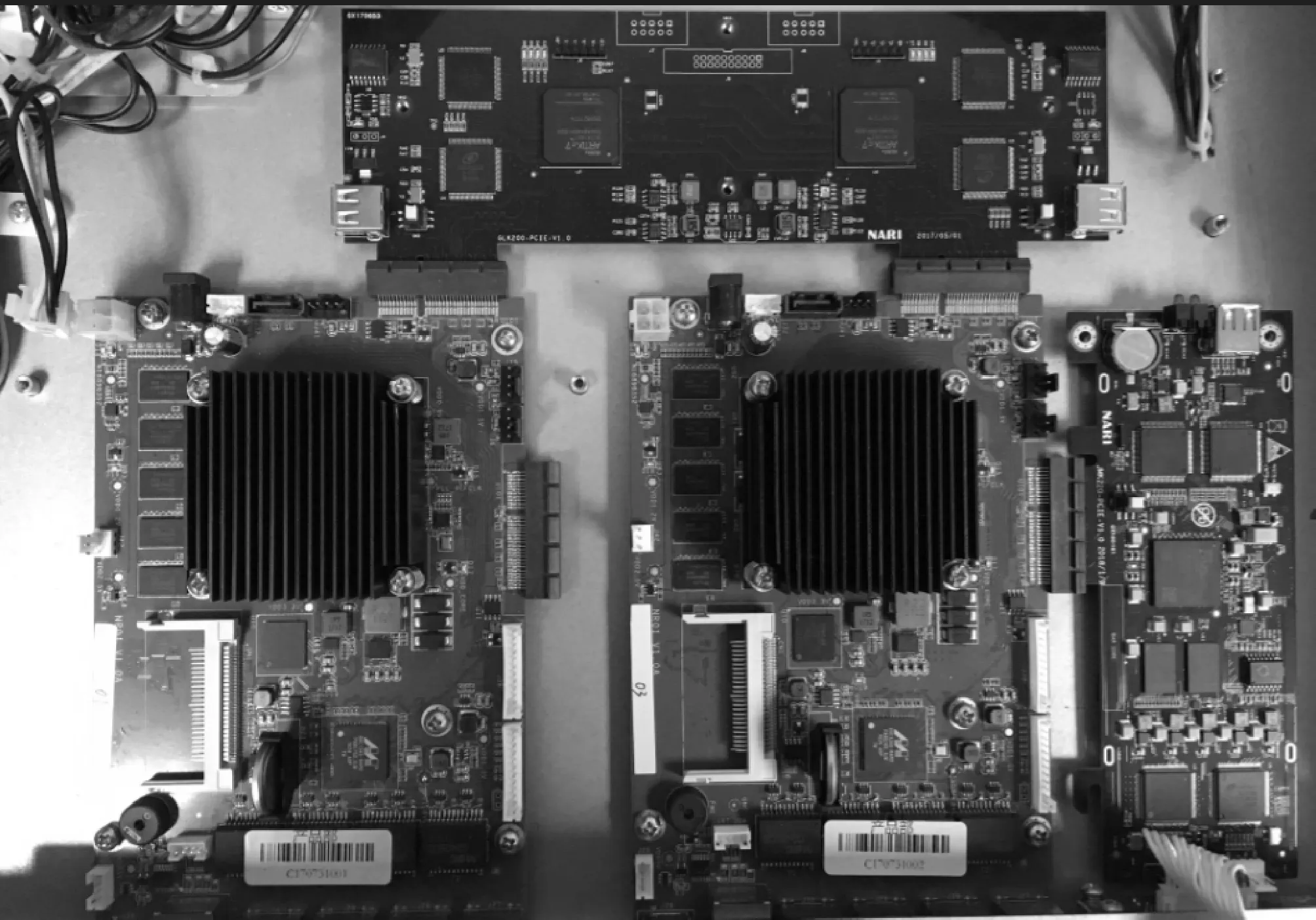

为了突出实验效果,对安装了本摆渡模块的网络隔离装置和安装了分离的数据加密模块的网络隔离装置分别进行测试。安装本设计方案的网络隔离装置实物图如图3所示。安装分离的加解密模块的网络隔离装置如图4所示。两台装置系统主板软硬件相同,CPU为Cavium Octeon III系列,主频为2.4 GHz,操作系统为Linux,内核版本3.10。

图3 安装了本方案的网络隔离装置

图4 安装了分离加密模块的网络隔离装置

3.2 数据测试

本摆渡模块支持两种数据摆渡方式:明文透传和密文传输。明文透传模式是指数据从一侧的主机系统传输到摆渡模块上的FPGA后不进行任何处理,直接通过SERDES接口传输到另外一块FPGA进而传输到另一侧的主机系统。密文传输是指首先对报文进行加解密处理,再通过摆渡模块传输到另一侧的主机系统。

明文透传数据时,单独安装分离加密模块的网络隔离装置与应用本方案的网络隔离装置在数据传输路径上相同。密文传输模式时,单独安装分离加密模块的网络隔离装置首先要将数据写入加密模块进行加解密处理,处理完成后返回主机系统,再写入到摆渡模块进行传输。

应用本方案的网络隔离装置首先将数据写入摆渡模块,经过加解密处理后,直接进行传输,省去了数据返回主机及重新写入摆渡模块的过程。经过测试,两种方案的明文透传性能一致,为1.5 Gbps;密文传输时,采用本方案的网络隔离装置传输速度为1.2 Gbps,采用分离加密模块的网络隔离装置传输速度为800 Mbps。应用本设计的网络隔离装置在密文传输模式时,数据传输速度有明显优势,且能节省硬件资源,提高CPU的资源利用率。

结 语

聂云杰、王元强(硕士),朱孟江、赵华(本科):主要研究方向为电力系统嵌入式设计。