千兆UDP/IP协议栈FPGA实现及其在高速成像系统中的应用

郑天宇 尹达一

摘 要: 在FPGA中设计并实现了传输速率为1 000 Mbit/s的以太网UDP/IP协议栈,并将其应用在图像采集系统完成图像传输。UDP/IP协议栈分为MAC层和UDP层,MAC层完成基本以太网帧的收发,UDP层完成顶层用户数据封装。协议栈完全兼容IEEE 802.3ab千兆以太网标准,具有显式流量控制功能,解决了FPGA千兆以太网硬核媒体访问控制器移植弹性低,资源消耗大的难题。仿真与实验结果表明,协议栈资源占用率低,用户端数据率可达964 Mbit/s,在帧长度为1 472时丢包率为0%,对于1 000[×]1 000(pixel)面阵CMOS探测器帧频可达48 f/s,适用于嵌入式高速图像采集系统。

关键词: 千兆以太网; UDP/IP协议栈; 流量控制; 图像采集; FPGA; 高速成像

中图分类号: TN911.73?34; TP393.0; TP73 文献标识码: A 文章编号: 1004?373X(2018)18?0001?05

Implementation of gigabit UDP/IP protocol stack in FPGA and its

application in high?speed imaging system

ZHENG Tianyu1,2,3, YIN Dayi1,2

(1. Key Laboratory of Infrared Detection and Imaging Technology, Chinese Academy of Sciences, Shanghai 200083, China;

2. Shanghai Institute of Technical Physics, Chinese Academy of Sciences, Shanghai 200083, China;

3. University of Chinese Academy of Sciences, Beijing 100049, China)

Abstract: An Ethernet UDP/IP protocol stack with 1000 Mbit/s transmission rate was designed and implemented in FPGA, and applied in the image acquisition system to achieve image transmission. The UDP/IP protocol stack consists of the MAC layer and UDP layer. The MAC layer completes reception and sending of basic Ethernet frames, while the UDP layer completes encapsulation of top?level user data. The protocol stack is fully compatible with IEEE 802.3ab gigabit Ethernet standard, and has the function of explicit flow control, which can solve the difficulties of low transplant flexibility and large resource consumption of gigabit Ethernet hard core media access controller in FPGA. The simulation and experimental results show that the protocol stack has low resource occupation rate, data rate of 964 Mbps on the client side, packet loss rate of 0% when the frame length is 1 472, and frame frequency of 48 f/s for the 1 000×1 000 (pixel) area array CMOS detector, which is applicable for the embedded high?speed image acquisition system.

Keywords: gigabit Ethernet; UDP/IP protocol stack; flow control; image acquisition; FPGA; high?speed imaging

0 引 言

大面阵、高帧频的高速图像采集系统在科研领域、工业现场的应用日渐广泛,但巨大的数据量以及实时性需要较高的数据带宽使其应用受限[1]。传统的IEEE 1394,Camera link等接口因为功耗高、体积大等原因在手持设备或移动端的应用受到限制。千兆以太网是一种新型的以太网,具有高速、高效、高性能的特点,它不仅能够提供1Gbit/s的传输带宽,降低了系统整体的成本,还能够提高系统的扩展性[2]。近几年来通信系统中千兆以太网媒体访问控制器作为硬核集成在芯片中的应用不断发展,但硬核成本高和可移植性低的缺点限制了其使用[3]。

FPGA在嵌入式图像采集系统中应用广泛[4?5],内部可编程逻辑适用于多种接口[6]。本文在FPGA内设计了一种千兆以太网UDP/IP协议栈,以减少逻辑资源消耗为目的,同时增强了可移植性,较传统硬核具有较大优势,适用于数据量大的图像采集传输系统。

1 协议栈整体框架结构

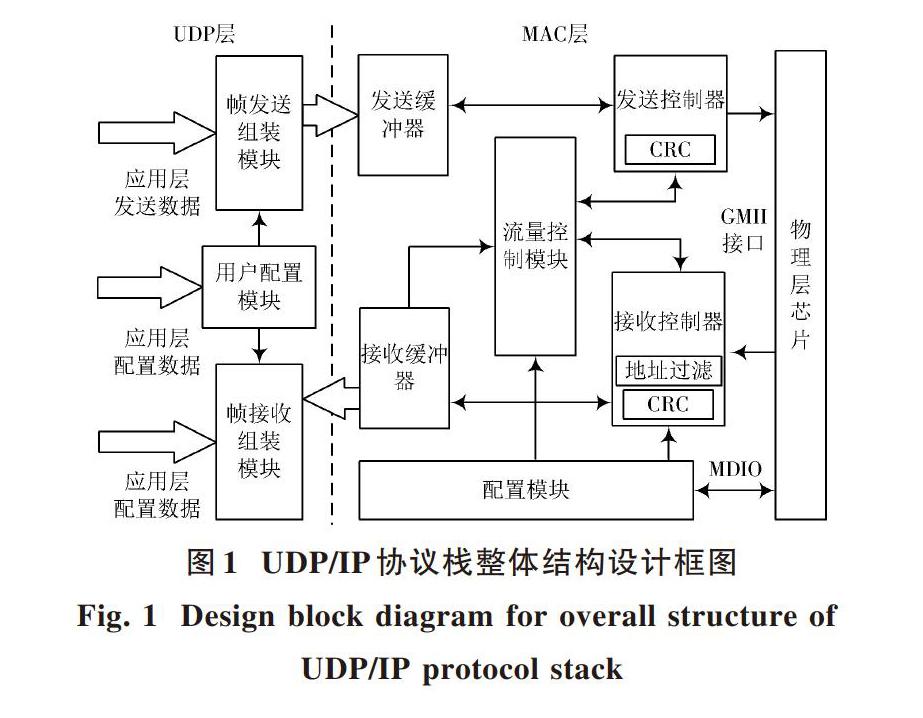

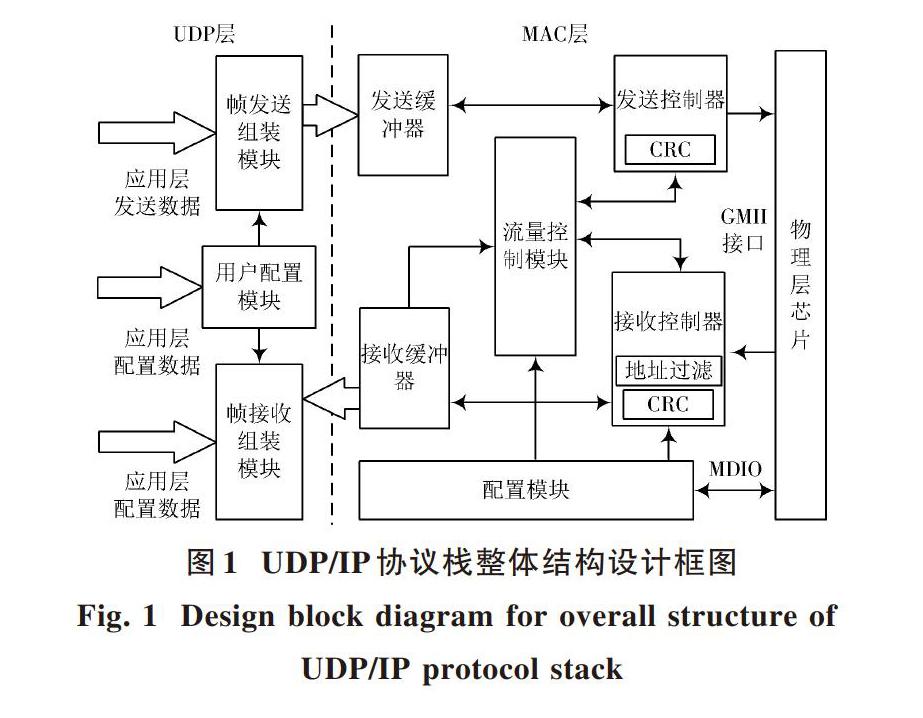

UDP,IP协议分别服务于TCP/IP参考模型的传输层与网络层,面向无连接、不可靠、数据报传输的协议[7],特别适用于高速图像采集系统。UDP/IP协议栈总体框图如图1所示,包含MAC层和UDP层两部分。

MAC层与物理层芯片直接连接,完成以太网基本帧的接收以及发送,具体包括发送、接收控制器,发送、接收缓冲器以及流量控制模块;UDP层为顶层用户提供数据接口,负责数据组装及配置。UDP层与MAC层通过缓冲器互联。

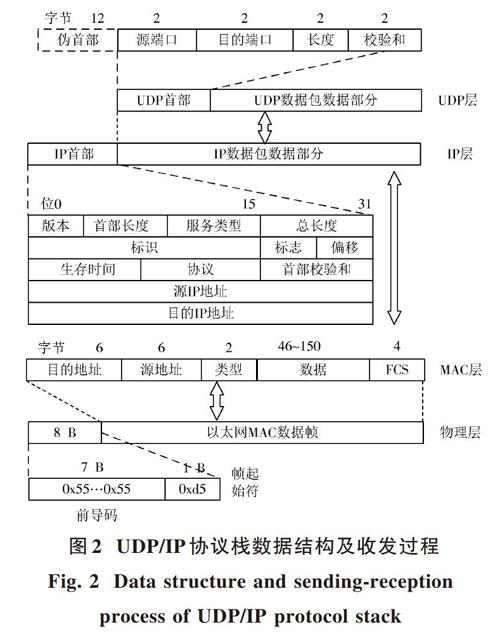

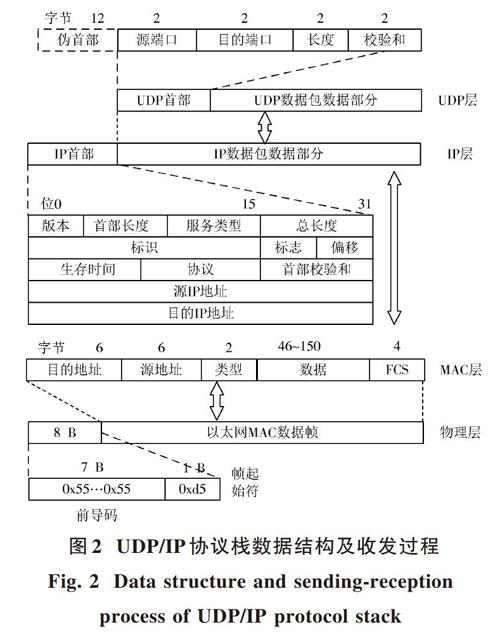

两站点之间通过以太网收发数据时,数据按照一定协议格式封装,然后以比特流的形式在信道中传输。数据打包传输过程如图2所示。用户数据从应用程序产生,然后传递给传输层,在传输层针对不同的传输协议加上不同的传输层协议首部,此处加UDP头。然后传给网络层,在此加IP头。最后传给网络接口层,封装为基本以太网帧。帧发送为自上向下过程,帧接收过程与之相反。

2 各模块实现

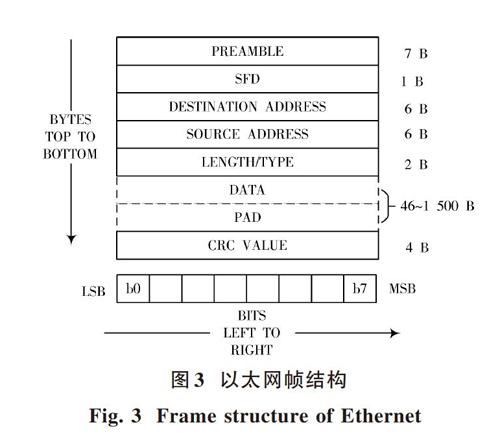

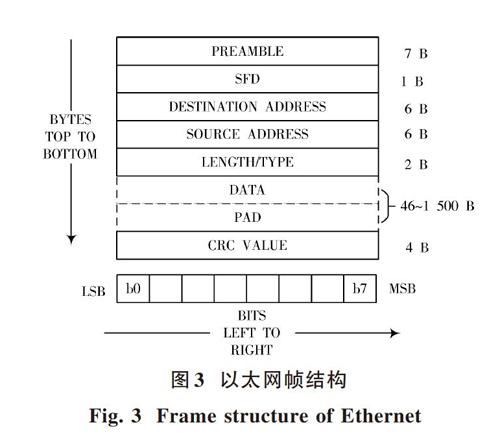

以太网数据在信道中以数据帧的形式传递,底层MAC帧格式如图3所示。以太网帧包含前导码(PREAMBLE)、帧起始符(SFD)、帧目的地址(DESTINATION ADDRESS)、帧源地址(SOURCE ADDRESS)、帧长度/类型(LENGTH/TYPE)、数据及填充(DATA&PAD;)、帧CRC校验值(CRC VALUE)。按照从上到下的顺序发送字节,每个字节按LSB到MSB的顺序发送。其中,前导码包含7个字节的0x55,用来完成物理层同步;帧起始符是1个字节的0xd5,表示一帧的开始;帧目的地址(DESTINATION ADDRESS)、帧源地址(SOURCE ADDRESS)各包含6个字节,代表该帧所要到达的目的MAC地址和发送站点的MAC地址;帧长度/类型包含2个字节,当其值小于1 536时表示帧长度;数据及填充字段为46~1 518 B的帧数据;帧CRC校验值是从帧目的地址字段到填充字段的校验和,以太网中使用CRC?32校验和[8]。

IEEE 802.3规定千兆以太网具有半双工和全双工两种通信模式。半双工通信方式为了解决媒体随机接入控制中的信道冲突采用载波监听多点接入(CSMA),每个站点在发送数据包前首先监听信道状态,确定无其他站点数据通信时才发起该次通信[9]。随着技术的进步以及交换机的应用,全双工通信方式得以普及,优点是无需对信道进行监听,可直接收发数据,通信时需要流量控制。因为图像数据为点对点通信,所以本文设计的UDP/IP协议栈工作在全双工模式。

全双工模式为了避免流量过大,通信站点间使用PAUSE帧请求暂停数据传输一段时间。PAUSE帧结构类似于普通以太网数据帧,具有相同结构的前导码、帧起始符、帧目的地址、帧源地址、以及幀CRC校验,不同的地方在于帧长度/类型字段为PAUSE帧特有的标识符:32h88080001,数据段为两字节的暂停时间参数,单位为512 bit单位传输时间。

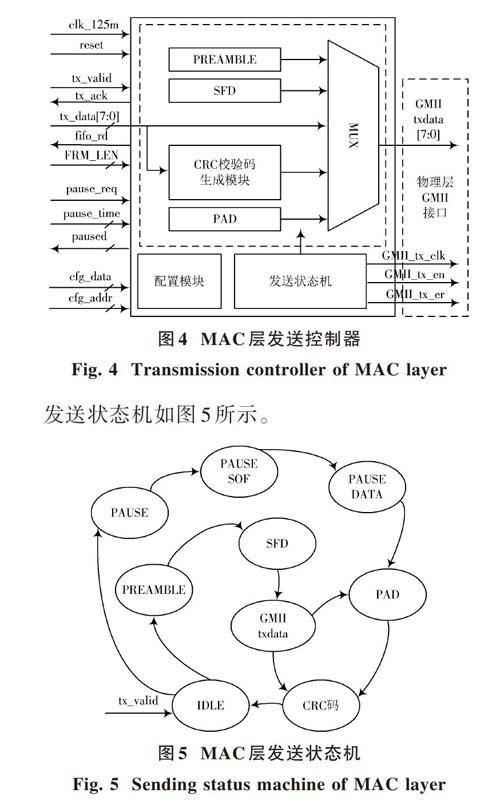

发送控制器如图4所示,配置模块接收用户配置,包括源地址、目的地址。发送状态机控制多路选择器完成整帧发送,GMII_tx_en有效时在GMII_tx_clk的上升沿将数据送入GMII接口,千兆以太网GMII接口的数据位宽为8 bit,时钟频率为125 MHz。同时发送状态机接收PAUSE帧请求信号,在线路中数据量较大,站点难以有效接收时向发送方发送PAUSE帧。

复位后处于IDLE状态。当发送缓冲器要满时,tx_valid有效。此时若pause_req为0,即无暂停请求,则进入PREAMBLE状态,连续7个时钟周期发送字节码8h55作为前导码。下一时钟周期进入SFD状态发送帧起始符8hd5,此时发送缓冲器fifo_rd有效。接下来进入GMII_data状态发送以太网用户数据,数据的长度为FRM_LEN,数据来自于发送缓冲器。最后发送4 B CRC校验码。

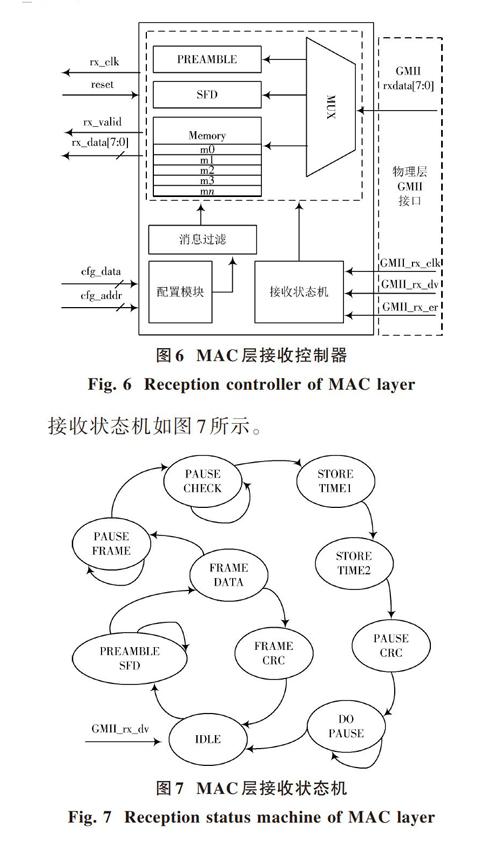

接收控制器如图6所示,配置模块接收用户配置需要过滤的帧信息。接收状态机负责控制数据接收过程,接收到的数据帧拆解掉前导码、帧起始符后将有效数据存入Memory,接收并校验完成后发送接收有效信号rx_valid。

复位后处于IDLE状态。GMII_rx_dv信号来自于物理层芯片,当其有效时,表示接收到以太网帧,接下来8个时钟周期开始接收PREAMBLE和SFD,然后进入FRAME DATA状态接收以太网数据并使能数据校验,接收到目的地址后通过消息过滤模块进行消息匹配,过滤出想要接收的消息。如果为PAUSE帧则进入PAUSE FRAME状态,如果为正常帧,当FRAME CRC状态确认以太网帧有效时,进入IDLE状态。对于PAUSE帧,在PAUSE FRAME状态持续5个时钟周期,接收完源MAC地址后进入PAUSE CHECK状态依次校验PAUSE帧的长度/类型、暂停标志,校验成功后进入STORE TIME1和STORE TIME2状态保存暂停时间。校验完成后进入DO PAUSE状态,在该状态进入一个空循环,循环周期计数值由接收到的暂停时间决定。

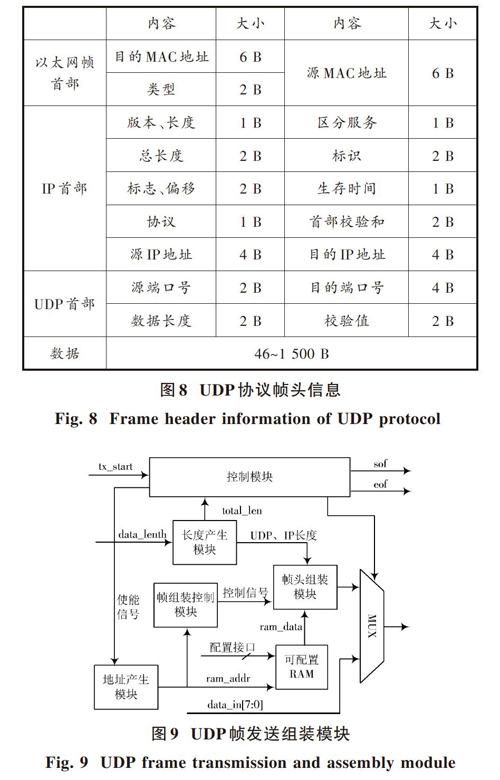

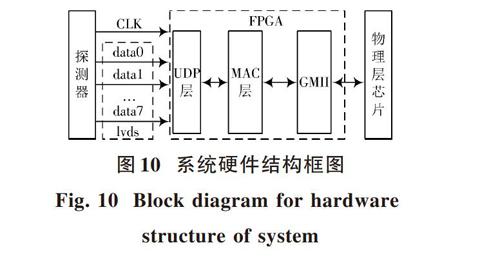

UDP/IP帧结构包括帧头信息和数据两部分,帧头信息预先存储在可配置RAM中,可由用户修改,帧头各字段的内容及占据的数据位宽如图8所示。UDP帧发送组装模块如图9所示,其由控制模块、地址产生模块、帧组装控制模块、长度产生模块、帧头组装模块和可配置RAM组成。该组装模块主要完成UDP/IP帧头信息的产生与数据封装。工作流程为:当tx_start有效时产生使能信号和sof信号。地址生成模块中的计数器累加,可配置RAM中的UDP帧头信号输出,此时缺少头长和校验部分。IP,UDP头长信息可由长度产生模块得到,分别为data_lenth+28和data_lenth+8,帧组装控制模块输出控制信号将头长度信息和RAM中存储的其他信息相结合,最终在控制模块的作用下由多路选择器先输出帧头信息,后输出数据。输出完毕后eof信号有效。

3 系统硬件框图

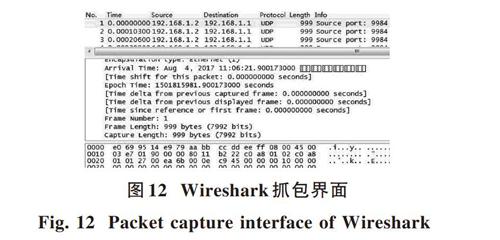

系统硬件结构框图如图10所示。其由1 000[×]1 000 CMOS探测器组件、FPGA以及千兆以太网物理层芯片组成。探测器ADC量化位数为12 bit,像素码值通过8路LVDS信号传至FPGA,FPGA将数据打包发送到UDP应用层,通过UDP/IP协议栈将数据发送到上位机。上位机接收数据显示并保存,同时可发送积分时间、开窗区域等指令至FPGA。

4 实验验证及成像

实验验证系统由探测器板和信息处理板组成如图11所示,二者通过软板互联,UDP/IP协议栈在信息处理板FPGA内实现。

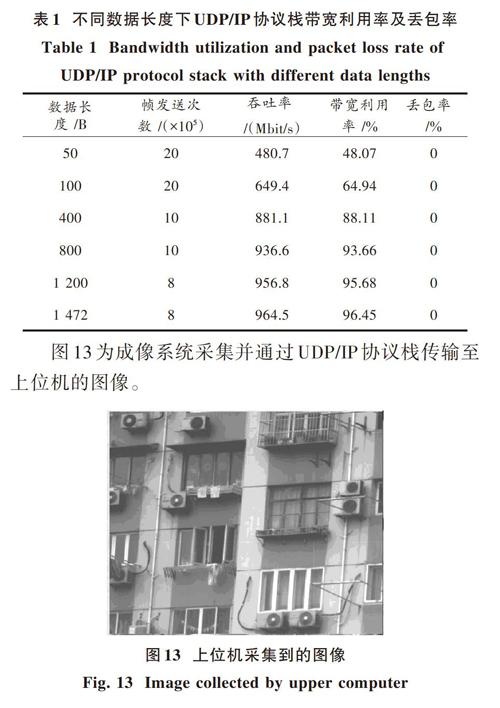

为了验证硬件设计的正确性,发送固定已知格式的数据帧至上位机,在上位机利用Wireshark网络抓包分析工具抓取数据,并分析其正确性。图12为Wireshark某次抓取界面,由抓取结果分析可知,数据帧符合UDP协议,源地址为192.168.1.2,目的地址为192.168.1.1,帧长度为999,与FPGA中配置的帧头信息及数据长度完全一致。

其中UDP帧头长度固定为42,数据长度越大,有效数据在一帧中占得比重越大,带宽利用率越高。丢包率是衡量UDP通信协议的一个重要标准,考核方法为:定义UDP帧数据段中一个32 bit字段为帧计数,FPGA中UDP帧组装时每发送完一帧该计数值加1,上位机接收完一定量数据帧后统计该计数值是否连续递增;若帧之间出现非连续状态,通过两帧之间该字段的差值得到丢失帧数,最后统计总丢失帧数后计算丢包率。

5 结 论

本文详细分析了IEEE 802.3ab以太网标准协议,在FPGA内实现了面向高速图像数据传输的UDP/IP协议栈。经测试,协议栈数据传输速率高、系统稳定、丢包率低,满足大面阵图像采集系统的要求。本文创新点有:

1) 完整地实现了一种IEEE 802.3ab以太网UDP/IP协议栈,具有用户可配置及显式流量控制功能。

2) UDP/IP协议栈完全由硬件描述语言设计完成,资源占用率低、可移植性高,属性修改灵活,可缩短开发周期,同时降低系统成本。

3) UDP/IP协议栈成功应用在大面阵探测器高速图像采集系统中,经实际测试,数据传输丢包率低,系统运行稳定、可靠。

本文实现的UDP/IP协议栈可为嵌入式图像采集传输系统提供参考。

参考文献

[1] 俞鹏炜,任勇,冯鹏,等.基于FPGA的千兆以太网CMOS图像数据传输系统设计[J].国外电子测量技术,2016,35(11):76?81.

YU Pengwei, REN Yong, FENG Peng, et al. Design of gigabit Ethernet CMOS image data transmission system based on FPGA [J]. Foreign electronic measurement technology, 2016, 35(11): 76?81.

[2] 沈淦松.基于FPGA的千兆以太网相机的传输系统研究[D].成都:电子科技大学,2013.

SHEN Gansong. Research on FPGA based gigabit Ethernet camera transmission system [D]. Chengdu: University of Electronic Science and Technology of China, 2013.

[3] 朱保琨,刘广文.千兆以太网通信端口FPGA设计与实现[J].计算机工程与设计,2016,37(9):2292?2298.

ZHU Baokun, LIU Guangwen. Design and implementation of gigabit Ethernet communication port based on FPGA [J]. Computer engineering and design, 2016, 37(9): 2292?2298.

[4] 吕星宇.嵌入式计算机智能图像信息处理系统设计与实现[J].现代电子技术,2016,39(21):83?86.

L? Xingyu. Design and implementation of embedded computer intelligent image information processing system [J]. Modern electronics technique, 2016, 39(21): 83?86.

[5] 李鹏.嵌入式系统中千兆以太网的设计与实现[J].现代电子技术,2014,37(12):4?7.

LI Peng. Design and realization of gigabit Ethernet in embedded system [J]. Modern electronics technique, 2014, 37(12): 4?7.

[6] 毛群.基于DSP和FPGA的信号处理模块及其IP核设计技术研究[D].杭州:浙江大学,2016.

MAO Qun. Research on signal processing module and IP core design technology based on DSP and FPGA [D]. Hangzhou: Zhejiang University, 2016.

[7] 张威.基于FPGA的高速以太网接口设计和实现[D].成都:电子科技大学,2016.

ZHANG Wei. Design and implementation of Ethernet high?speed interface based on FPGA [D]. Chengdu: University of Electronic Science and Technology of China, 2016.

[8] 吴琼,刘建国,黄庆超,等.基于以太网帧结构的AES加解密算法的实现[J].光通信技术,2016,40(11):16?19.

WU Qiong, LIU Jianguo, HUANG Qingchao, et al. Implementation of AES cipher and decipher algorithm based on Ethernet frame structure [J]. Optical communication technology, 2016, 40(11): 16?19.

[9] 孙海超,陈春宁,田睿,等.基于以太网的高速图像传输的研究与实现[J].计算机技术与发展,2014,24(3):187?189.

SUN Haichao, CHEN Chunning, TIAN Rui, et al. Research and implementation of high?speed image transmission based on Ethernet [J]. Computer technology and development, 2014, 24(3): 187?189.

[10] 江丽.基于Matlab空间域算法的图像增强技术的研究与应用[J].电子设计工程,2016,24(22):131?133.

JIANG Li. The research and application of the image enhancement techniques in the spatial domain based on Matlab [J]. Electronic design engineering, 2016, 24(22): 131?133.