基于Multisim的大容量N进制计数器的仿真设计

王长江

(四川职业技术学院 电子电气工程系,四川 遂宁 629000)

0 引言

计数器不仅可以用来计数,而且还可以用来实现定时、分频、测量和控制等功能,例如,计算机的时序发生器、分频器、指令计数器等。在集成计数器中,常用的二进制和十进制计数器的进制一般都是固定的,如74LS190为10进制,74LS193为16进制。在实际中应用中,如数字钟电路中,却需要24进制和60进制计数器,因此,这就要利用现有的固定进制计数器来设计需要的N进制计数器。

Multisim是美国国家仪器(National Instruments,NI)公司推出的一款电路仿真分析与设计软件,该软件能够激发电子设计爱好者的设计灵感,广泛用于电子技术教学、设计和科研中。下面以集成同步十进制可逆计数器74LS192为基础,基于Multisim软件实现大容量N进制计数器的设计与仿真。

1 74LS192逻辑功能

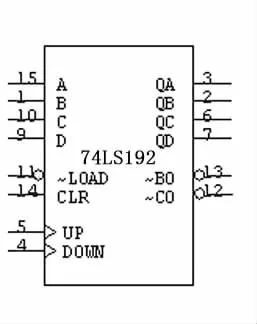

74LS192是双时钟输入的同步十进制可逆计数器,其逻辑符号如图1所示。图中,UP为加计数时钟输入端,DOWN为减计数时钟输入端,CLR为清零端(高电平有效),~LOAD为预置数端(低电平有效),~CO为进位输出端(1001状态后负脉冲输出),~BO为借位输出端(0000状态后负脉冲输出),A~D为并行数据输入端,QA~QD为计数器状态输出端(计数状态为0000~1001)。

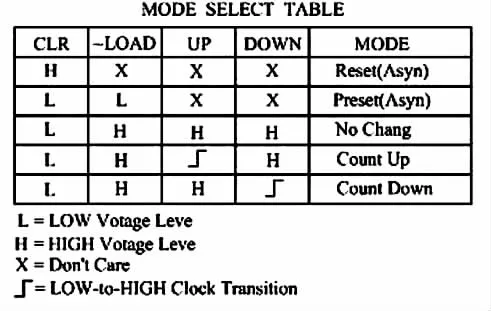

74LS192的逻辑功能如图2所示,表明它具有如下主要的逻辑功能:

(1)异步清零。当CLR=1时,计数器立即清零,即 QDQCQBQA=0000。

(2)异步置数。当~LOAD=0,且CLR=0时,将A~D并行输入端的输入数据置入计数器,即QAQBQCQD=ABCD。

(3) 加法计数 。当 CLR=0,~LOAD=1,且DOWN=1时,UP端输入计数脉冲,计数器实现十进制递加计数。

(4)减法计数。当CLR=0,~LOAD=1,且 UP=1时,DOWN端输入计数脉冲,计数器实现十进制递减计数。

图1 逻辑符号

图2 逻辑功能

2 电路仿真设计

设现有M进制计数器,要设计一个N进制计数器。如果N小于M,需要用一片M进制计数器就可以实现N进制计数器的设计;如果N大于M,需要用多片M进制计数器来实现大容量N进制计数器的设计。

2.1 级联法设计

级联法是指先将大容量计数器模N分解为多个因数相乘(每个因数小于单片计数器模的最大值),即 N=N1·N2·N3…Nn,再用 n片计数器分别组成模值为N1、N2、…、Nn的计数器,最后采用串联进位或并行进位方式级联起来从而实现N进制计数器。

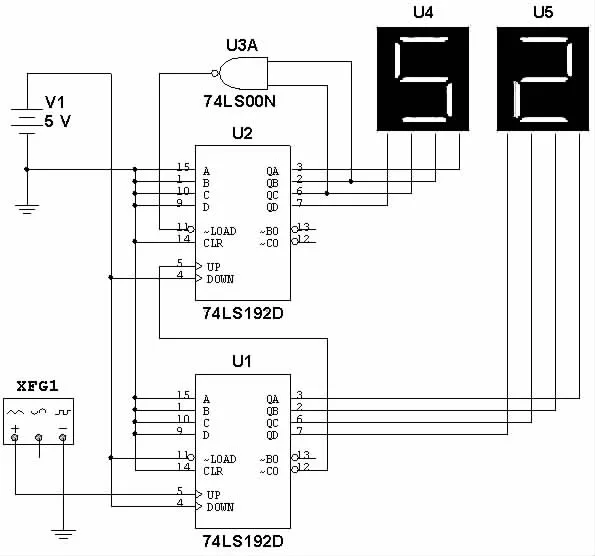

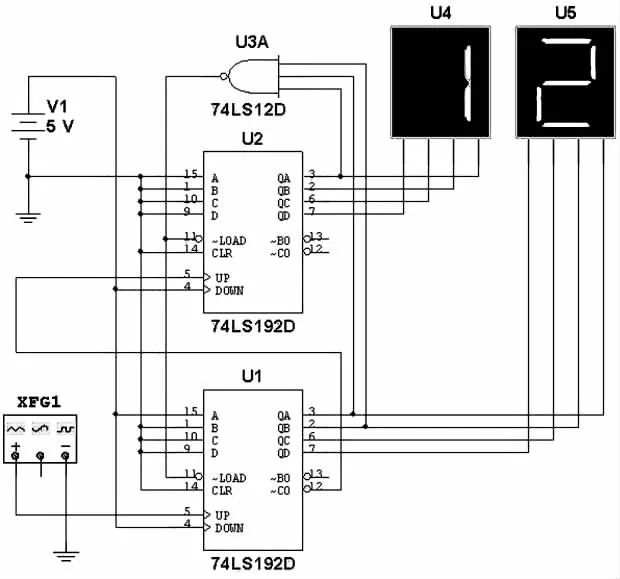

例如,用两片74LS192设计一个60进制加法计数器。

要设计的60进制计数器模N=6×10,个位片U1组成十进制计数器(第一片低位);十位片U2组成6进制计数器(第二片高位),采用串行进位级联方式将两片级联起来,即将低位片计数器U1进位端~CO的输出信号作为高位片计数器U2的计数输入脉冲。当十位片计数器U2计到6时,异步置数端~LOAD=0,计数器被置数到0,从而实现了60进制计数。

根据上述设计原理,利用Multisim 11软件创建的设计仿真电路如图3所示。运行仿真开关,观察到计数器从0开始计数,计到59时开始循环,实现60进制加法计数功能。

图3 60进制计数器仿真电路

2.2 整体清零法设计

整体清零法是指先将多片M进制计数器级联成大于N进制计数器,然后利用计数器的输出状态SN(同步清零为SN-1)译码输出产生清零信号,同时加到多片计数器的清零端,使多片计数器同时清零,从而实现N进制计数器。

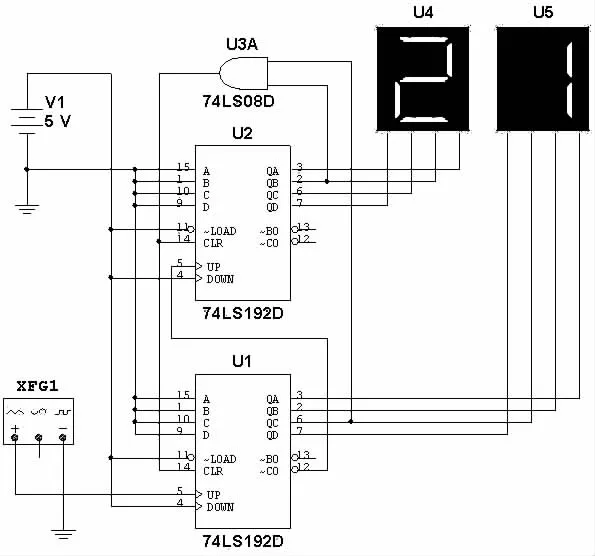

例如,用两片74LS192设计一个24进制加法计数器。

现在需要设计24进制计数器,应先将两片74LS192用串行进位方式级联构成100进制计数器;再将100进制计数器采用整体清零法构成24进制计数器。

24进制计数器对应的二进制代码

反馈置零函数

计数器状态S24经非门输出的高电平信号同时送到两片计数器的清零端,使两片计数器同时清零,从而实现24进制计数。

根据以上设计原理,利用Multisim 11软件创建的设计仿真电路如图4所示。运行仿真开关,观察计数器从0到23计数,计到23时开始循环计数,实现24进制加法计数器功能。

图4 24进制加法计数器仿真电路

2.3 整体置数法设计

整体置数法是指先将多片M进制计数器级联成大于N进制计数器,然后根据设计选定的N进制计数器状态,确定计数器预置数状态,计数器从预置数状态开始计数,计满N个状态后译码产生置数信号,同时加到多片计数器的置数端,使计数器返回到预置数状态,跳过剩余的不用状态,从而实现N进制计数器。

例如,用两片74LS192设计一个殊12进制加法计数器。

在数字钟里,对时位的计数序列是1、2、…11,12、1、…是12进制的,且无0数。当计数器计数到13时,计数状态QU2DQU2CQU2BQU2AQU1DQU1CQU1BQU1A=001001001产生置数信号,使计数器返回到计1,从而实现1-12计数。所以,计数器预置数状态00000001,即十位片U2直接置0000,个位片U1直接置0001,计数器的反馈置数函数为

根据上述设计原理,利用Multisim 11软件创建的设计仿真电路如图5所示。运行仿真开关,观察计数器从1到12计数,当计到13时回到1,开始循环计数,实现12进制加法计数器功能。

图5 特殊12进制加法计数器仿真电路

在此设计案例中,置数信号~LOAD=0由计数器状态经过译码产生,有时也可以由进位输出端~CO(加计数)或借位输出端~BO(减计数)输出信号产生。

例如,用两片74LS192设计一个30递减计数器。

需设计30递减计数器,应先将两片74LS192级联构成100进制递减计数器;再将100进制递减计数器构成30递减计数器。

计数器从30开始递减计数,预设置数应为30,相应的计数状态为00110000,即个位片U1置数0000,十位片U2置数0011。个位计数器U1(从9减计数到0时),~BO端(发出低电平信号,平时为高电平)发出一个负脉冲作为十位计数器U2减计数时钟信号,十位计数器U2减1计数;当十位计数器U2和个位计数器U1都处于全0时,十位计数器U2的~BO=~LOAD=0,计数器完成置数作用,此后~BO=~LOAD=1,计数器在减计数脉冲作用下,进入下一轮30递减计数。

根据此设计原理,利用Multisim 11软件创建的设计仿真电路如图6所示。运行仿真开关,观察计数器从30到00递减计数,当计到00时计数器置30,重新开始减计数,实现30倒计数功能。

图6 30进制递减计数器仿真电路

3 结束语

大容量N进制计数器的设计可以采用级联法、整体清零法和整体置数法。Multisim软件具有直观的图形界面、庞大的元器件库、丰富的测试仪器和完备的分析工具,它能够激发电子设计爱好者的设计灵感,是现代电子电路设计的有效方法。基于Multisim实现大容量N进制计数器的设计与仿真,操作简单,搭接电路方便,仿真结果清晰表明设计的计数器能够实现所要求的N进制计数功能。