基于Hi3521A的多路视频监控系统设计

,

(华北电力大学 控制与计算机工程学院,保定 071000)

引 言

视频监控系统能够应用在许多领域,无论是安全防范、网络直播还是视频会议,都能看到它的影子。与文字、语音等形式相比,视频监控系统更加直观、方便,信息内容更加丰富。随着嵌入式技术的发展和进步,视频监控系统也得到了快速的发展,从原来的模拟视频监控发展到现在的嵌入式视频监控,并得到了广泛的应用,成为视频监控领域的一个应用热点。本文设计了以嵌入式Linux操作系统和Hi3521A硬件平台为核心的多路视频监控系统。

1 系统总体设计

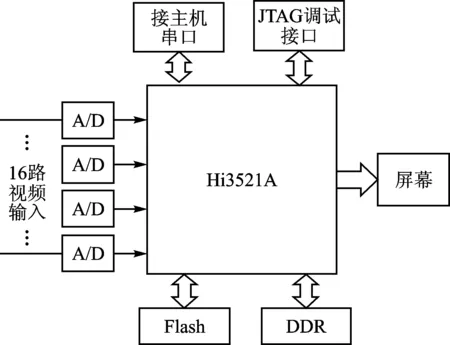

为实现多路视频的采集和传输,获得视频的实时数据是一个重要环节[1]。本系统采用Hi3521A芯片作为核心芯片,并对其外围设备进行扩展。Hi3521A是华为公司生产的针对多路标清、高清录像产品应用研发的一款专业SoC芯片。海思Hi3521A芯片内置有ARM处理器以及H.264视频编解码引擎,还包含了丰富的外围接口,有极强的扩展能力。基于所选的芯片设计出的系统总体框图如图1所示。

图1 系统总体设计框图

其中A/D转换模块选择的是Nextchip公司生产的NVP6134C芯片,共使用了4个NVP6134C芯片,每个芯片可将4路模拟视频信号采样转换为数字视频信号。每个A/D芯片传输的视频流通过指定的通道传入Hi3521A芯片。

Flash模块用于存储Bootloader、启动环境变量、Linux内核、文件系统等数据,系统掉电后数据不会丢失。DDR为内存模块,用来控制应用程序的运行以及临时视频信息的存放。

WiFi模块选择的是RTL8211EG芯片,使用RGMII接口模式与主芯片Hi3521A相连。对其进行交叉编译,本系统可以通过无线网络进行数据传输。

系统上电工作时,首先视频采集端通过NVP6134C芯片将16路模拟摄像头采集到的视频流进行A/D采样,转换为数字视频信号;其次主芯片的VI端接收转换完成的视频流,并对数据进行裁剪、缩放等预处理;再次对视频流进行H.264编码;最后将视频输出到屏幕显示。

2 硬件实现

本文的多路视频采集系统是基于Hi3521A及其外围设备来进行开发的,需要完成视频图像的采集、处理及传输等功能,它采用了以下几个功能模块来设计:系统时钟及复位模块、视频采集模块、存储模块、电源模块[2]。

2.1 系统时钟及复位模块

通过Hi3521A芯片内部的反馈电路与外部的24 MHz晶体振荡电路一起构成系统时钟电路。同时,Hi3521A芯片内置RTC,要使其正常工作,单板还需要给RTC提供时钟电路。

在系统运行过程中,可能会因为各种干扰使系统出现异常,不能正常工作,这时设置复位电路就显得十分重要,它能使系统在出现异常时重新初始化系统,使系统重新工作。Hi3521A可通过判断POR_ENABLE引脚在上电时的状态来选择内部复位或外部复位。AB9引脚具备WDG_RSTN和SYS_RSTN_OUT两种功能。当Hi3521A芯片使用内部复位时,AB9引脚为SYS_RSTN_OUT功能;当Hi3521A芯片使用外部复位时,AB9引脚为WDG_RSTN功能。系统时钟和复位设计电路如图2所示。

图2 系统时钟和复位设计电路

2.2 视频采集模块

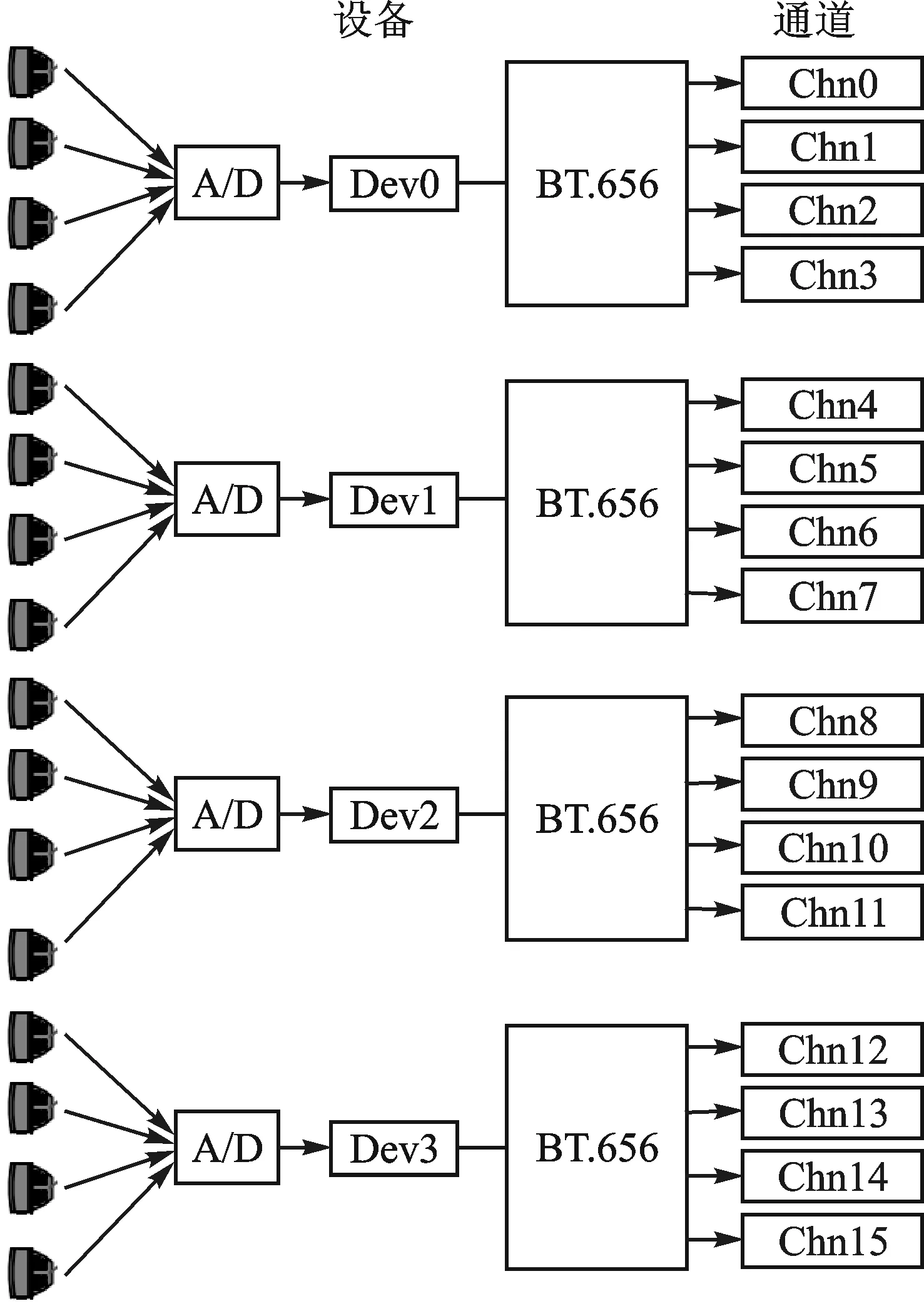

在本系统中,主芯片Hi3521A的视频输入端有4个VI设备,每个VI设备有4个VI视频物理通道,共包含16个VI视频物理通道。为了实现对16路视频的采集,使用了4个A/D转换器,每个A/D转换器对4路视频信号进行采样转换为数字视频信号,此时数字视频信号采用的是YUV格式,采样格式为4:2:2,即量度信道采样率为色度信道的两倍。Hi3521A通过BT.656对时序进行解析,并将解析后的视频数据传入物理通道。输入设备解析后得到的视频数据通过视频的物理通道把视频数据输出到DDR。在真正将数据输出到DDR之前,它可以实现裁剪、遮挡、水平垂直缩小和水平垂直翻转等功能,其绑定关系如图3所示,其中,Dev为设备,Chn为通道。

图3 设备与通道绑定关系图

2.3 存储模块

存储模块包含ROM和RAM两个部分,其中ROM采用Flash方式存储。Flash闪存可以快速读取数据,并且系统掉电后数据不会丢失,因此用来存储Bootloader、启动环境变量、Linux内核、文件系统等数据。目前Flash主要有两种NOR Flash和NAND Flash,本系统同时使用了NOR Flash和NAND Flash两种芯片,由于用户不能直接运行NAND Flash上的代码,所以使用NOR Flash用来运行启动代码,由于NAND Flash是以一次读取一块形式进行的,一般一次读取512个字节,所以采用NAND Flash进行读取,这样在很大程度上节约了成本。

RAM使用的是DDR3芯片,用来加载ROM中的信息,并存储处理信息时产生的中间数据。在DDR3内存中,一部分是由操作系统管理的,叫做OS内存;另一部分是供媒体业务单独使用的内存,叫做MMZ内存。其中OS内存大小可以通过bootargs进行配置。

2.4 电源模块

本系统核心芯片Hi3521A需要多种不同的输入电压为其供电,其中内核所需电压值为1.1 V,CPU电压为1.25 V,I/O电压为3.3 V,DDR3 SDRAM电压为1.5 V。本系统的输入电压为12 V,系统的电源电路通过采用稳压芯片MP1494S和MP1495S来实现这4种不同电压的输出。

3 软件设计

系统硬件设计完成以后需要进行软件环境的开发和应用程序的设计。本系统主要包括主机端和目标板端的设计,核心芯片Hi3521A通过串口和网线与PC机相连,在PC机上安装一台虚拟机,且虚拟机使用Linux系统来对开发板进行开发。

3.1 系统软件层次结构

系统软件主要包括4个部分:Bootloader、Linux内核、Linux文件系统以及应用程序,层次结构如图4所示。

图4 系统软件层次结构图

嵌入式Linux操作系统内核的作用是对硬件进行管理,而应用程序是不直接作用于内核的,它必须通过操作系统提供的系统调用接口作用于内核,然后内核作用于硬件。

3.2 系统环境的搭建

系统分为主机端和目标板端,其中主机端开发环境的搭建需要建立Linux服务器、Windows软件开发和Hi3521A嵌入式开发平台三个部分的连接。在本系统中,Linux服务器和Windows工作台使用一台PC机,即在虚拟机下安装一个Linux操作系统,并将其连接在同一个局域网内。Linux服务器用来建立交叉编译环境与开发板进行交互,Windows工作台主要用于登录Linux服务器,完成Linux下的开发工作以及通过串口查看开发板的调试和运行信息。

本系统主要包括3个方面的设计:U-boot、Linux内核和根文件系统。具体步骤为:Linux开发环境的搭建、U-boot的移植、Linux内核的移植以及根文件系统的定制。使用Bootloader的版本为Ubuntu-12.04-x6-phoenix,使用Linux-3.10.y版本的内核,以及使用JFFS2制作镜像文件系统。

3.3 应用程序的运行

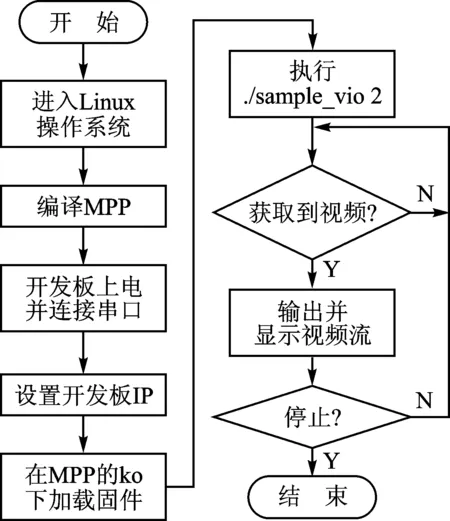

海思Hi3521A的SDK提供了多媒体软件平台(Media Process Platform,MPP),MPP提供的接口可用于视频应用软件快速开发。

首先在虚拟机中将MPP拷贝到SDK下的指定目录中,对MPP进行编译,即到mpp/sample下执行:make clean; make。开发板上电并设置开发板IP地址,到mpp的ko 下运行./load3521a-i,加载固件,最后到mpp/sample/vio下执行./sample_vio 2,即可在屏幕上显示摄像信息。具体步骤如图5所示。

图5 Hi3521A运行MPP流程图

系统采用像素为720P的AHD摄像头进行图像采集,HDMI接口连接屏幕输出,视频输出的结果如图6所示。

图6 视频输出结果

结 语