面向FPGA的故障注入测试技术研究*

王艳军,姜婷婷,张峻玮

(1.91404部队 软件测评中心,河北 秦皇岛 066001;2.江苏自动化研究所 信息技术部,江苏 连云港 222002)

近年来,集成电路已经融入我们的生活之中,如汽车、手机、热水器.军工方面集成电路被广泛应用于航天、船舶领域[1].集成电路的广泛应用要求其有较高的可靠性与实时约束性.可靠性评估常用的方法有两种:辐射测试和故障注入[2-5].辐射测试可以比较真实地模拟空间环境,但是成本高昂,并且实验周期较长[6].故障注入是一种评价重要的评估微处理器和寻找决定可靠性参数的方法.故障注入方法大致可以分为4类[7]:① 硬件故障注入;② 软件故障注入;③ 模拟故障注入;④ FPGA故障注入.相对于硬件故障注入与软件故障注入[8],模拟故障注入有更好的可观察性和可控制性,但模拟故障注入耗时高,FPGA故障注入既能保证不错的可控制性和可观察性,还可以加快故障注入测试.因此基于FPGA的故障注入具有重要的研究价值.

目前,基于FPGA的故障注入方法研究主要着眼于两个方面:基于配置技术的研究及基于仪表技术的研究.基于配置技术的FPGA故障注入主要是通过修改FPGA的配置数据,进行故障注入实验来达到故障注入的目的.例如王鹏等[9]根据FPGA配置帧的结构特点,对其进行分区测试,分析配置存储器中的敏感位,找到FPGA配置帧中最为敏感的区域,设计了故障注入测试系统,并进行了试验验证.基于仪表技术的FPGA故障注入技术主要是通过在原来电路上加上额外的电路进行故障注入.这两种方法都存在一定的问题.首先,基于配置技术的FPGA故障注入虽然注入过程可控制性和可观察性都很高,但FPGA需要进行重新配置,时间开销大.而基于仪表技术的FPGA故障注入虽然不需要增加时间开销,但需要增加额外的空间开销.为移除主机与FPGA间的交互时间,加速故障注入测评实验,本文提出一种面向FPGA的故障注入测试框架,实现面向FPGA的故障注入技术研究.

1 故障模型

人类的生活环境中充满了宇宙射线、太阳的粒子辐射、电磁辐射等[7].在辐射环境中,集成电路容易受到影响[10-13],发生单粒子效应.单粒子效应可以划分为单粒子翻转(single event upset,SEU)、单粒子闩锁(single event latch-up,SEL)等[14-15].为了注入SEU缺陷,在元电路中增加额外的电路,如图1所示,当设置FIS为高电平时,原输入信号数据进行反转,反转后的数值将被输入触发器中.这种方法的好处是在每次进行故障注入时不用进行中断处理,更符合实际应用需求.

2 故障注入测试架构

如图2所示,面向FPGA的故障注入测试架构主要包含3个模块.

① 故障注入管理模块:这个模块负责在需要进行故障注入时将FIS置1并触发观察模块.

② 观察模块:当观察模块被触发后,观察模块开始从观察点记录数据,该功能通过观察电路实现.

③ 结果分析模块:当观察模块记录到两组实验后开始触发结果分析模块.其中,第一组是无故障运行实验,第二组是故障注入实验.结果分析模块比较两个实验的观察结果,并报告测试结果.

2.1 故障注入管理

故障注入模块负责管理和执行故障注入测试实验.该模块在刚开始时设置故障注入定时器.设置定时器后,模块开始计数直到达到预定的故障注入时间.最后,决定是否进行故障注入(通过设置FIS来实现).在这里,交替运行故障注入实验和无故障运行(无故障注入)实验.无故障运行实验结果作为实验比较的基准.在实际操作时,也可以在几个时钟周期内进行无故障运行实验.设置相同的输入波形和时钟周期,运行故障注入实验.这样的好处是可以避免记录所有的故障、无故障数据.

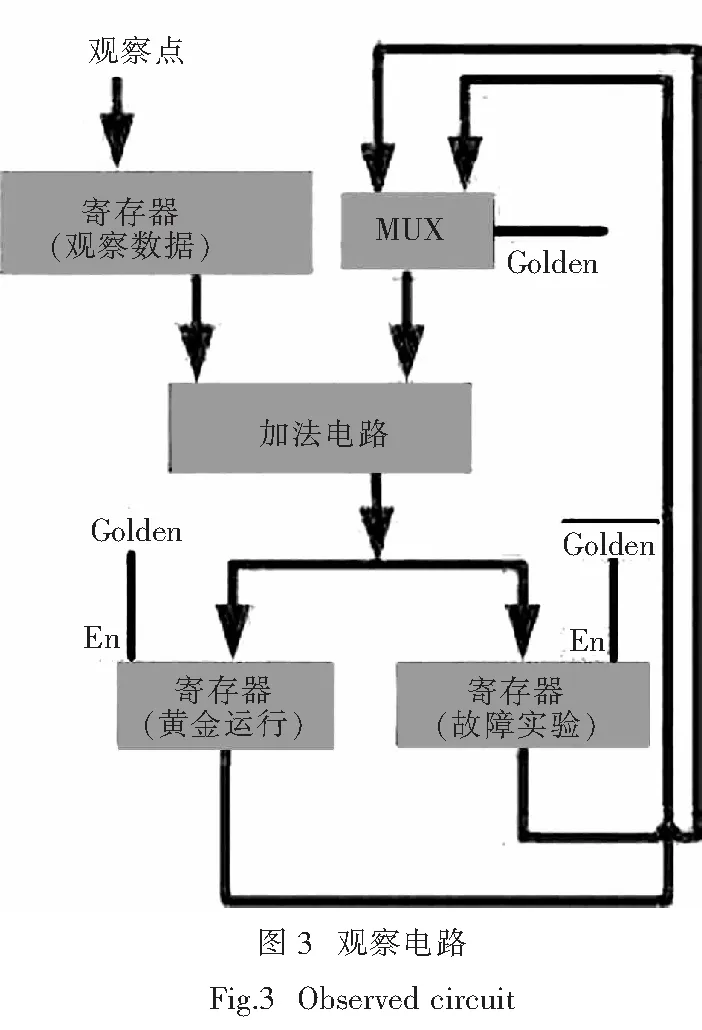

2.2 观察

当观察模块被触发后,模块开始从观察点记录数据,观察电路如图3所示.在实验中,无故障运行和故障实验交替运行,用无故障运行触发器来区分它们.无故障运行和故障运行实验一共会产生两种路径.用加法电路将新观察到的结果与原先观察到的结果相加.这里用加法器的原因是如果观察的数据与无故障运行结果不同,它会影响到加法结果,并且更容易产生两组不同的结果.

我们通常假设故障注入会维持几个时钟周期,这样我们仅需要记录这几个时钟周期的数据,便能大大加速故障注入实验.

2.3 结果分析

当观察模块记录到两组实验后开始触发结果分析模块.它仅比较无故障运行与故障寄存器,然后提取故障统计信息.它的工作主要是找出两组数据中的不同值,并进行统计.

3 故障注入过程

(1) 故障注入管理器设置定时器与无故障触发器.故障注入管理器首先检查无故障触发器,如果它为1,根据故障注入时间与实验时间为定时器设置新值.如果触发器为0,定时器保持在之前无故障运行时的数值.(2) 故障注入定时器开始进行定时,直到数值变为0.(3) 故障定时器变成0后,故障注入管理器开始检查无故障触发器,如果它是0,故障注入管理器将FIS置为1.(4)故障注入管理器触发观察模块,观察模块设置观察计时器并且开始记录观察值.观察计时器决定观察电路的观察时间.(5)如果观察时间变成0,检查无故障触发器为0还是为1.如果无故障触发器为1,观察模块将无故障触发器清空,执行过程将从步骤(1)重新开始.

4 结论

首先,通过几种故障注入方法的对比分析,强调了基于FPGA的故障注入方法研究的重要性;其次,提出了一种面向FPGA的故障注入测试框架架构,包括管理、观察及结果分析等模块;最后,对故障注入过程进行了详细介绍,并给出相关结论.在后续工作中,将进一步对该注入方法进行研究,将其扩展到其他领域,争取应用到复杂装备系统的故障注入研究.