系统中LATTICE FPGA在线升级方案

文/黄玮芳

1 引言

本设计提出了一种基于微处理器对FPGA动态配置的方案,通过串行将升级配置数据送入FPGA中来自动完成升级配置。此设计不仅使FPGA的升级速度更快、更方便,还减小了系统体积,节约了成本,解决了现场升级FPGA困难的难题。

2 设计概述

本设计使用motorola公司的MPC8270作为微处理器,对lattice公司的FPGA LFE2M20E进行控制来实现在线升级。

2.1 配置模式和配置方法

本设计的在线升级使用FGPA的Slave Serial模式,令FPGA作为从属器件,由微处理器MPC8270提供配置所需的时序和数据,完成配置数据的下载。

进行在线升级时,先将更新好的配置文件(.bit文件)以二进制形式从计算机下载到MPC8270的内存中去,再通过控制配置时序将配置数据串行发送到FPGA中进行配置。此配置方法不需要任何硬件动作和专业的软件,只需要使用CPU的8个I/O口,编一小段程序就可以实现FPGA的动态配置。

2.2 硬件实现

实现在线升级功能,硬件上需要将FPGA的8根信号线: CCLK、DI、DONE、INITN、PROGRAM、CFG0、CFG1、CFG2,分别连接到MPC8270的8个I/O口,其中CLK、DATA、FPGA_PROGRAM、FPGA_CFG0、FPGA_CFG1、FPGA_CFG2为输出态,STATUS、STATUS1为输入态。在升级前,需要对MPC8270的这8个I/O口进行输入输出配置。

2.3 升级过程

升级时,先将FPGA编译生成的.bit文件放入到CPU的内存中去,再将CFG0、CFG1、CFG2配置为1、0、1,随后CPU的FPGA_PROGRAM信号发一个大于8ns的低脉冲信号,通知FPGA开始编程,同时监测INITN和DONE信号。当FPGA接收到CPU发出的FPGA_PROGRAM低脉冲时,INITN会迅速输出一个低脉冲,同时将DONE拉低。当CPU监测到INITN的低脉冲和DONE由高变低后,知道FPGA已准备好接收升级数据,可以朝它发数据了,接着将CPU内存中的.bit文件通过DI脚串行发送到FPGA内,一个CCLK向DI内发送一个bit数据,当文件发送完毕后,由于配置文件中已经包含了FPGA初始化的一些代码,所以传输完配置文件后,FPGA就可以正常工作了,此时,FPGA会将DONE信号置高,表示升级已完成。

CPU检测到DONE信号变高后,完成在线升级。如果传输中出现了异常,DONE信号将一直为低,如保持低电平时间如果超出升级所需时间,结束升级并报错,此时,需要重新升级。

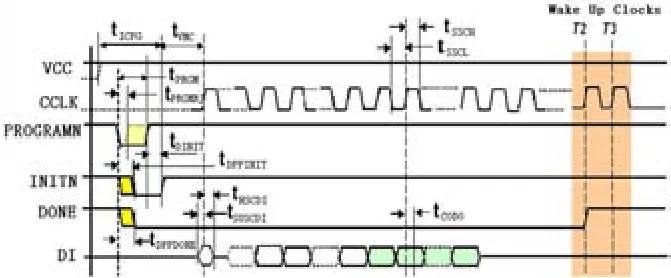

2.4 升级配置时序

升级配置时序图如图1所示。

整个升级过程要严格按照配置时序来进行。

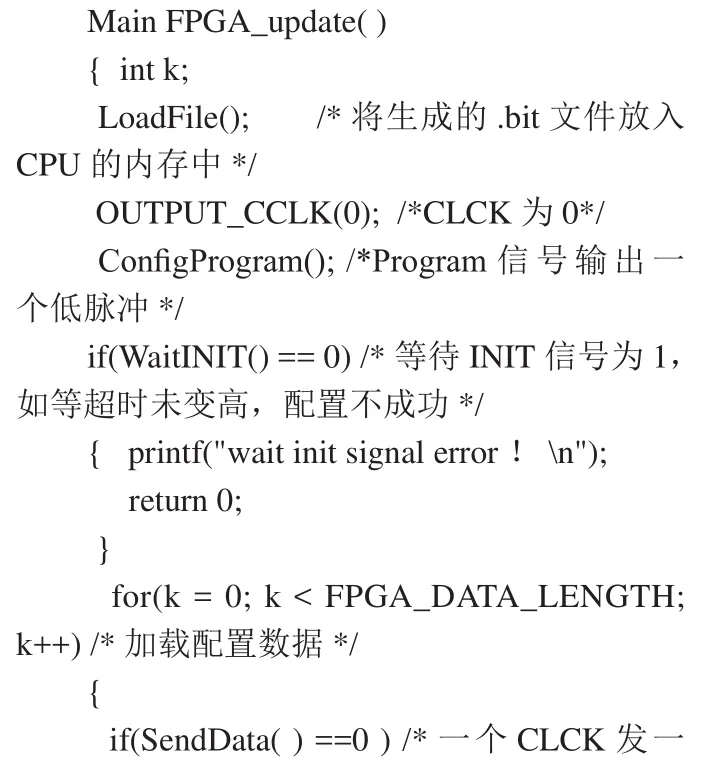

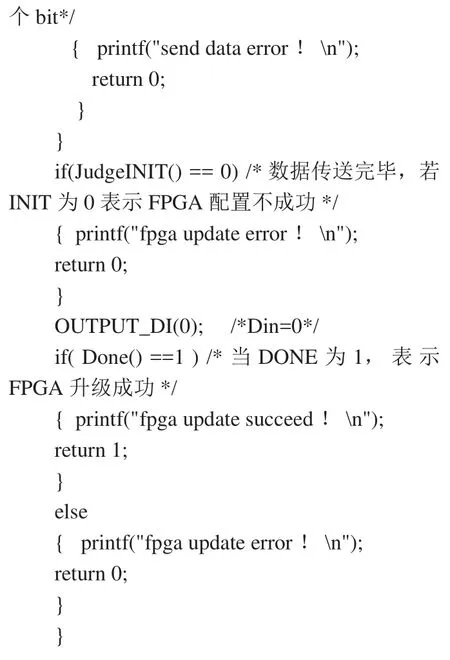

3 软件实现

软件部分是通过下载配置文件、配置端口和读取数据来完成升级的。先在PC机上发命令将升级配置文件(.bit文件)存在MPC8270的内存里,然后配置升级所需的端口,利用微处理器的I/O口产生配置时序,串行将升级配置数据送入FPGA中自动完成配置。升级主要程序如下:

图1:升级配置时序图

4 结束语

本文所描述的FPGA在线升级的设计已经在实际系统中得到了应用,取得了良好效果。本设计虽然是针对MPC8270和LATTICE的LFE2M20E来实现在线升级的,但对于应用LATTICE公司其它系列的FPGA和其他的微处理器,只要微处理器控制部分稍做改动即可加以应用。这一点在日益兴起的软件无线电系统中具有广阔的应用前景并能满足某些用户对于在线调试、更新和维护的需求。