10~15 GHz宽带捷变源设计

刘瑜现,薄淑华,任 程

(航天科工集团303所,北京 100074)

0 引言

频率合成器是产生1个或多个稳定频率的信号源。频率合成技术于20世纪30年代提出,它作为现代无线通信系统、雷达系统、电子对抗和精密测量仪器等领域的核心器件,发挥着十分重要的作用[1]。频率合成技术在国外发展较早。目前,国外的频率合成技术发展的比较成熟,在频率合成器的产品种类和技术指标上比国内技术好得多,相比之下,我国对频率合成技术的研究比较晚,技术较为落后。超宽带、快速锁定、低相位噪声、低杂散、小型化、全集成的频率合成器的设计始终是对现代电子系统的一个挑战[2]。

本文将通过研究锁相环原理,寻找提高锁相环频率源频率捷变时间的方法[3],设计一种输出频率在10~15 GHz的频带捷变频的锁相频率源。其主要方法是直接数字频率合成器(DDS)产生参考信号,固定相频比,利用DDS参考信号的跳频实现整个捷变源的跳频,由于DDS的快速跳频,捷变源的跳频时间主要取决于锁相环的锁定时间,因此减小锁相环路的频率锁定时间是重点研究内容。

1 提高锁相环锁定时间方法

锁相环由鉴相器、环路滤波器和压控振荡器组成。鉴相器是相位比较装置,用来比较输入信号ui(t)与压控振荡器输出信号uo(t)的相位,它的输出电压ud(t)是对应这2个信号相位差的函数;环路滤波器的作用是滤除ud(t)中的高频分量及噪声,以保证环路所要求的性能;压控振荡器指输出频率与输入控制电压有对应关系的振荡电路,频率是输入信号电压的函数的振荡器VCO,压控振荡器受环路滤波器输出电压uc(t)的控制,使振荡频率向输入信号的频率靠拢,直至二者的频率相同,使得VCO输出信号的相位和输入信号的相位保持某种特定的关系,达到相位锁定的目的[4]。

以采用二阶环路滤波器的三阶锁相环为例,其频率锁定的时间为:

(1)

式中,ωn为环路自然谐振角谐振频率;ξ为阻尼因子;Δftol为最终锁定频差;f1为初始频率;f2为进入锁定带频率。

由式(1)可知,频率锁定的时间与环路带宽、起始频率差有关系。锁相环路的带宽直接决定了锁定时间:环路带宽越大,锁定时间越短;环路带宽越小,锁定时间越长[5]。频率跳变的大小也决定环路的锁定时间:频率跳变越大,锁定时间越长;频率跳变越小,锁定时间越短。

减小锁相环锁定时间的主要方法有:

① 增加环路的带宽,可以减小频率锁定时间。但是增加环路带宽,减小杂散信号的衰减,增加相位噪声,当环路带宽增加到1/5的鉴相频率时,环路可能变得不稳定,环路失锁。

② 增加鉴相频率,鉴相频率决定了反馈信号和参考信号的比较速度,增加电荷泵的鉴相频率,加速电荷泵向环路滤波器的充放电,有效降低锁定时间。

③ 减小跳频的频率,跳频越小,环路频率锁定的时间越短,如果频率跳变在锁相环路的快捕带内,频率锁定的时间将会很短[6]。

预置电压法是减小频率跳变的起始频率差以达到快速捕获的目的。跳频的大小由系统决定,不能改变,但前馈补偿方法可以用来降低初始频率差,从而加快锁定速度,这就是预置电压法。

预置电压法有2种[7]:人工电调法和自动扫描法。人工电调法是直接向压控振荡器提供一个控制电压,改变压控振荡器的频率,从而减小起始频差,当起始频差减小到直接进入快捕带时,在环路本身的牵引作用下锁定频率;自动扫描法是当环路尚未锁定时,给压控振荡器加—个周期性扫描电压.使它的频率在足够宽的范围内摆动。当频率扫到环路快捕带时,环路通过自身捕获进入锁定,此时加在压控振荡器控制端的扫描电压自动去掉[8]。

通过在频率锁定的频点[9],对压控振荡器的电压进行测量;通过数模转换,将对应的频点的电压值存储到单片机,当频率开始跳变时,根据目标频点将此频点对应的电压读出;通过数模转换,经过加法器与原来环路中环路滤波器输出的模拟控制电压相加得到下一个频率所需的控制电压值,然后将此电压输入到压控振荡器的控制端,使压控振荡器的频率发生改变,接近要跳变的频点值,将环路直接拉入快捕带,实现频率的快速跳变[10]。电压预置方法的难度在于数模转换电压的精确度,并且提供的电压信号具有较高的纯度,纹波信号对环路的锁定有影响。精确的电压对数模转换要求较高,电路更加复杂[11]。

2 总体设计

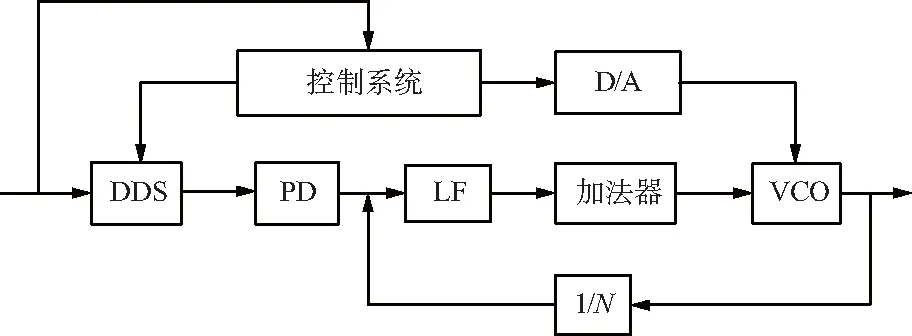

频率合成的方法有多种[12-13],但各有优缺点,通过取长补短使频率合成器达到理想的技术指标。通过对PLL和DDS的研究,采用DDS直接激励PLL,即用DDS的输出作为PLL的参考输入,来解决频率分辨率和相位噪声的矛盾[14],其原理框图如图1所示。当DDS的输出作为PLL的输入参考信号时,射频信号分频比固定不变,频率的步进由DDS改变实现,PLL相当于带有跟踪滤波功能的倍频器,PLL将有效抑制DDS的输出杂散,提高信号输出频谱质量[15],而且参考频率较高,可以通过增加PLL的环路带宽提高跳频时间[16]。

图1 宽带捷变源原理

DDS激励PLL的频率合成方式中,由于DDS的响应时间在ns级,因此频率跳变的时间主要取决于PLL的时间,PLL的频率跳变时间在μs级,甚至ms级。为了缩短PLL的频率响应时间,在DDS激励PLL的基础上,增加压控振荡器的电压预置快锁技术,将锁相环的起始频差迅速拉入鉴频鉴相器的锁定带内,减小环路锁定时间,以实现频率的快速跳变。当小步进时调整DDS的输出改变锁相环路的频率输出,当频率跳变步进大时,控制部分直接提供给压控振荡器一个控制电压,将其拉入快锁带进行频率锁定,减小锁定时间。

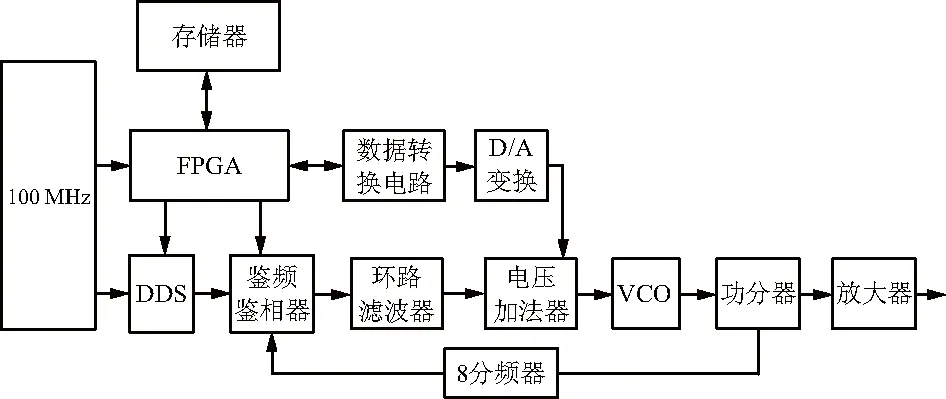

本文采用100 MHz晶振作为参考频率,分别提供给控制系统和DDS,由于VCO的输出频率为10~15 GHz,经过8分频后,输出频率为1.25~1.875 MHz,再经过鉴频鉴相器内部集成的分频器进行20分频,最终以62.5~93.75 MHz的频率进行鉴相比较,即DDS的输入到鉴相器的频率为62.5~93.75 MHz,经过环路滤波器后输出控制电压提供给VCO,当频率进行跳变时,由控制系统控制D/A变换器给出预置电压输出,同时改变DDS的输出频率,D/A控制器输出的预置电压通过加法器与锁相环路中环路滤波器的输出电压相加后输出给VCO,实现VCO输出频率的跳变,VCO输出频率经过分频反馈回路与DDS的输出频率进行鉴相比较,实现目标频率的再次锁定,如图2所示。

图2 方案原理

3 电路参数设计及仿真结果

环路带宽作为PLL的重要参数,通过设置环路滤波器的电阻电容值来改变环路的带宽和相位裕度参数。本文采用的是三阶低通滤波器,如图3所示。

图3 三阶低通滤波器

环路已确定参数设置如下:环路带宽(Closed-loop Bandwidth)为2 MHz;鉴相器输出峰值(Vp)为5 V;射频输出频率为10 000 MHz;鉴相频率为62.5 MHz;分频比(N)为160;相位裕度为60。

计算环路滤波器未知参数。经计算,Cc,C2,R2的值分别为232 pF,941 pF,316 Ω。

经过ADS仿真可知,环路的低通滤波器的环路带宽为2 MHz,相位裕度为54。

对未加电压预置时的频率锁定时间进行仿真分析。用ADS仿真,环路带宽为2 MHz,分别设定不同的跳变频率。锁相环最终锁定频率由10 GHz跳变到11 GHz时需要时间如图4所示。

图4 跳变频率与时间关系仿真结果

经过仿真,频率由10 GHz跳变到11 GHz的时间是7.532 μs,由10 GHz跳变到15 GHz的时间是11.96 μs,由仿真结果可知,当锁相环路的带宽固定时,锁定频率的范围越大,环路锁定需要的时间也就越长。

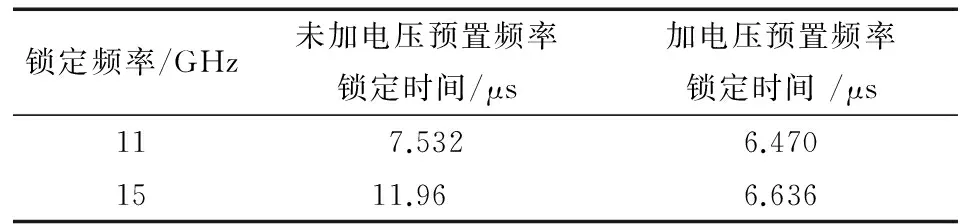

用ADS仿真,环路带宽为2 MHz,增加电压预置,以研究加入电压预置后对频率锁定时间的影响,如表1所示。

表1 电压预置对频率跳变时间影响

锁定频率/GHz未加电压预置频率锁定时间/μs加电压预置频率锁定时间 /μs117.5326.4701511.966.636

由表1可知,加入电压预置后频率锁定时间将减小,且锁定频率跳变带宽越大频率锁定时间减小的效果越明显。

经过仿真分析,频率在10~15 GHz进行跳变,可以实现跳变时间为10 μs以内。

4 试验结果

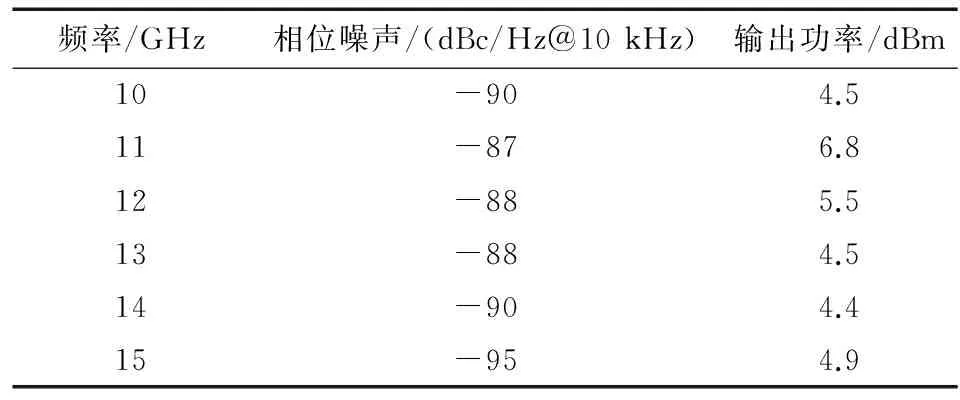

样机实物图如图5所示。相位噪声和输出功率测试结果如表2所示。

图5 样机实物

表2 相位噪声测试结果

频率/GHz相位噪声/(dBc/Hz@10 kHz)输出功率/dBm10-904.511-876.812-885.513-884.514-904.415-954.9

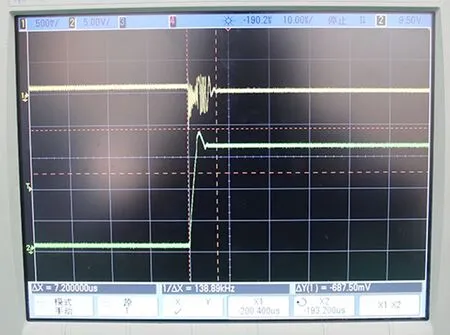

加电压预置后,通过示波器进行频率捷变时间的测试测试结果如图6所示,测量的频率捷变时间为7.2 μs。

图6 频率捷变时间测试结果

5 结束语

锁相环应用范围广泛,但是由于响应时间较慢,限制了它的应用。频率跳变起始频差影响锁相频率源频率跳变时间,通过电压预置的方法减小频率跳变时的起始频率差,可以有效提高频率锁定的时间,并且通过选用具较高鉴相频率的鉴相器,提高环路带宽,最终可以实现在5 GHz的宽带下,频率跳变时间在10 μs内的技术指标。