一种使用数字可编程技术的DDS信号发生器的设计*

[]

1 引言

信号发生器又称信号源或振荡器,在生产实践和科技领域中有着广泛的应用。能够产生多种波形,如三角波、锯齿波、矩形波(含方波)、正弦波的电路被称为函数信号发生器。函数信号发生器的实现方法通常是采用分立元件或单片专用集成芯片,但其频率不高,稳定性较差,且不易调试,开发和使用上都受到较大限制。随着FPGA的不断发展,DDS技术应用的愈加成熟,利用DDS原理在FPGA平台上开发高性能的多种波形信号发生器与基于DDS芯片的信号发生器相比,操作更加灵活,而且还能根据要求在线更新配置,系统开发趋于软件化、自定义化。[1]本文研究了基于FPGA的DDS信号发生器设计[2],实现了满足预定指标的多波形输出。

2 系统总体设计

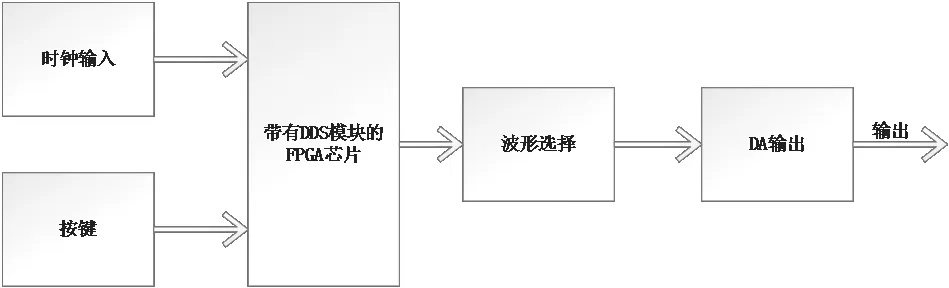

系统的整体设计图如图1所示,由时钟模块、按键模块、DDS模块、波形选择模块、DA输出模块构成。

本设计以FPGA作为控制器,通过DDS技术输出需要的波形数据,然后通过高速AD输出模块输出波形;并能经过按键模块调节频率的数值以及通过拨码开关切换波形种类。

3 模块部分设计

3.1 DDS信号源模块设计

在系统硬件设计中,DDS信号源模块包括了相位累加器、ROM波形存储器、按键接口模块设计和系统时钟控制模块设计。通过相关模块的介绍,可以了解到DDS信号源模块的内部组成及其工作方式。[3]

图1 系统设计框图

3.1.1 相位累加器模块设计

在DDS信号源的设计中,相位累加器是整个设计的关键。相位累加器包括一个加法器和一个数据寄存器。[4]其中加法器的一个输入端是频率控制字K,通过多次累加运算产生寻址ROM所需要的地址数据;数据寄存器用来保持所产生的地址数据,同时还具有的一个功能是将频率控制字发送到总线接口中,用于与主控模块的信息交互。其模块框图如图2所示,该模块有系统时钟,复位,频率控制字,键盘按键输入数,新采样数据时钟五个输入,以及ROM地址线位数及结果两个输出。

经验证,16位字长的相位累加器既可以保证输出信号频率具有较好的分辨率,又可以适应开发板存储空间的要求,匹配相应的ROM,使设计达到最佳的效果。在本设计中,通过外部按键模块更改相位累加器输入的频率控制字,从而改变累加运算的输出结果,进而改变输出信号的频率。

3.1.2 ROM存储器设计

本系统设计需要生成四种波形,所以需要四个.mif文件。本设计引用了四个256*8位的ROM,用于存储波形数据,有时钟和ROM地址线两个输入以及ROM数据线位值q。为了获得我们所需要的.mif文件我们必须对.mif文件进行编译,对于该文件的编译有两种办法:对于存储单元不是特别多的ROM我们可以进行手工编写,但是存储单元较多时用上种方法显得有点冗杂,也容易出错,故我们可以借助MATLAB来进行编写。每个波形的ROM表中所存储的信息不同,这是因为波形存储器储存的是一个完整波形离散的256个抽样值,故不同波形由不同的ROM查询表。

3.1.3 按键控制接口设计

在本设计中,需要有外置按键组来控制DDS输出信号的参数特性,包括调节输出信号的类型和频率等。按键接口模块的模块有时钟,复位,以及按键三个输入,有数码显示、行按键、按键数及新采样数据四个输出,其中新采样数据作为DDS模块中stepclk的输入。

在设计中加入了按键接口模块,则必然要加入按键消抖功能,以保障按键功能的正常使用。在本设计中,加入的按键消抖模块,通过检测连续两个时钟沿的电平输入情况,判断按键是否处于稳定输出状态。

3.2 波形选择模块设计

波形选择模块由一个四选一选择器构成.共有时钟,方波ROM数据线位值,三角波ROM数据线位值,正弦波ROM数据线位值,锯齿波ROM数据线位值及输入wave_mode六个输入,当输入wave_mode的值为二进制00时,wave_out输出为正弦波;当输入wave_mode的值为二进制01时,wave_out输出为方波;当输入wave_mode的值为二进制10时,wave_out输出为三角波;当输入wave_mode的值为二进制11时,wave_out输出为锯齿波。

4 系统测试与仿真

对硬件电路调试完成后,将该设计进行仿真[5],仿真时默认输出信号为正弦波,依次按下按键后,依次出现方波,三角波,锯齿波,仿真结果如图2所示。

5 结束语

图2 系统仿真结果

随着现代科技的不断发展,函数信号发生器在教学、通信、测量等领域的应用变得越来越广泛,信号发生器成为现代科研领域不可或缺的重要工具。然而制作高性能信号发生器的关键技术在于频率合成。随着时代的发展,频率合成技术经历了由简单到成熟的发展过程。目前,数字式直接频率合成技术已经成为现代频率合成技术中的佼佼者。在本设计中,借助现场可编程门阵列的独特优势,我们在FPGA实验板上进行了基于DDS技术的数字信号源的搭建,实现对DDS信号源的控制及实时参数显示。[6]