RISC-V处理器的低功耗模式设计

胡志杰

摘要:本设计提出了一种基于RISC-V指令集架构的SOC低功耗模式设计。该设计适用于小型、移动的处理器芯片,以及对低功耗模式需求越来越高的人工智能应用芯片。本设计分为低频模式、睡眠模式、停机模式。本设计通过VCS+VERDI联调仿真,观察整体设计的波形,通过VIVADO软件对不同工作模式下的电路综合分析。经过计算,处理器在三种不同工作模式下的功耗分别降低了正常模式下的4%、8%、63%。在FPGA板的功耗测试中,睡眠模式下FPGA板整体功耗降低了正常模式下的19%功耗。

关键词:时钟控制;低功耗;降频模式;睡眠模式;停机模式

中图分类号:TP216 文献标识码:A 文章编号:1007-9416(2019)02-0179-02

随着微电子技术的发展,在物联网和嵌入式领域,RISC-V指令集架构开始广泛地被应用。基于学习与研究的目的,本设计着手于国内开源的处理器软核蜂鸟E203处理器,对以往低功耗模式的研究分析后进行改进,提出一种新的低功耗模式的方案[1-3]。

1 低功耗模式设计基础

在蜂鸟的E203处理器核是一种超低功耗的2级流水线处理器核,它本身没有设计针对SOC本身的低功耗模式。因此本设计主要围绕蜂鸟E203的低功耗模式方案讨论。

蜂鸟E203 SOC的时钟域分为常开域、主域与调试域三部分。其中常开域主要是采用的是来自处理器外部的低速时钟,时钟频率为32.768 KHz。主域的时钟主要包含了整个芯片的主体部分,此部分时钟主要是供给处理器核、总线部分以及SOC部分的外设。

2 低功耗模式设计方案

一般来讲,芯片的总功耗为静态功耗与设计的动态功耗的总和。而静态功耗的数值为器件静态功耗与设计的静态功耗之和。其中器件静态功耗为器件上电的时候,还没有设置数值时的晶体管泄露功率。设计静态功耗为器件被设置时,在没有切换电路数值的状态下的功耗。而设计中的动态功耗是用户控制电路过程中,电路切换活动得出的平均功耗。

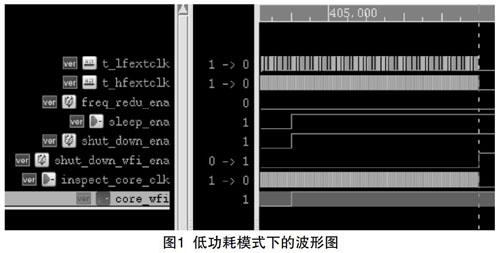

对于降频模式设计来说,主要是面向主域进行处理。通过时钟控制模块,向SOC顶层模块、CPU(Central Processing Unit)顶层模块、CORE顶层模块、GPIO(General Purpose Input Output)等外设及处理器控制器模块进行时钟转换。如图1所示,其中freq_redu_ena信号是指的降频模式下的降频使能信号,以波形图中的处理器时钟信号inspect_core_clk为参考对象,在降频使能到来之时,降低整体SOC的时钟频率。其中,sleep_ena信号是SOC的睡眠模式下的使能信号,在睡眠模式使能到来之时,整体的处理器高频时钟在睡眠模式下关闭时钟,但是处理器的各级使能仍然存在。

本设计下的睡眠模式在sleep_ena睡眠信号到来之时,由时钟控制模块输出到处理器的SOC顶层模块、CPU顶层模块、CORE顶层模块,然后通过控制译码模块与执行模块中的WFI(Wait For Interruption)指令实行,实现整体的睡眠模块功能设计。在停机模式下,停机模式使能信号shut_down_ena与shut_down_wfi_ena信号分别通过时钟控制单元输出到SOC顶层模块、CPU顶层模块与CORE顶层模块之中,shut_down_ena使能信号需要在整体时钟信号停止之时,调用WFI指令先进入睡眠模式,同时在睡眠模式中由于多周期指令的存在,执行阶段的时钟是常开的,因此需要在一段时间之后通过shut_down_wfi_ena使能信号关闭,更大程度上降低功耗。在停机模式下,所有时钟控制模块下的时钟全部关闭,外部低频时钟域外部高频时钟全部隔开,外部低频模式下的常开域时钟域外部高频模式下的主域时钟也全部关闭,等待实时计数器或者中断的唤醒,继续工作。

3 设计结果分析

如图2所示,停机模式下,功耗是正常模式下的36%,也就是说停机模式下,理论上可以降低原来的64%的功耗。在降频模式下,功耗是正常模式下的96%,可以说,在较低频率的时钟下,稳定状态下相比于正常模式下的功耗减少了4%。在睡眠模式下,功耗是正常模式下的91%,可以说,在睡眠模式的时钟下,稳定状态下相比于正常模式下的功耗减少了9%。

如图3所示,是在FPGA板上运行的结果,该板为ARTIX A7板,可以看出,烧录软核,跑LED灯之时,正常模式下电流为0.18A,电压为5V。此时功耗包括整个FPGA板上的SOC功耗部分与其它未涉及但是开发板实际上是处于供电状态下的功耗。在睡眠模式与降频模式下,整体开发板处于低频时钟控制下,包括處理器核的执行阶段也是降频模式,在双重低功耗模式下,开发板可以降低功耗达到原来的19%,这一部分的数据是极为可观的,也就是说随着处理器电路工作量越大,降频模式与睡眠模式所带来的低功耗百分比越大。

4 结语

本文提出的SOC低功耗模式设计,解决了蜂鸟E203处理器核进一步降低功耗的工作模式设计,使得其更加适用于低功耗与小面积方面的应用场景,特别是在物联网与嵌入式领域。

参考文献

[1] 史兴强,范学仕.一种SoC低功耗模式设计与实现[J].电子与封装,2018,18(2):40-45.

[2] 郭涛,张修钦,罗军.一种基于SoC的低功耗设计[J].集成电路应用,2018,35(7):22- 24.

Low Power Mode Design of RISC-V Processor

HU Zhi-jie

(College of Physics and Information Engineering, Fuzhou University, Fuzhou Fujian 350116)

Abstract:This design presents a low power mode design of SOC based on RISC-V instruction set architecture. This design is suitable for small, mobile processor chips, and artificial intelligence application chips with increasing demand for low power mode. This design is divided into low-frequency mode, sleep mode, shutdown mode. Through VCS + VERDI simulation, the design observes the waveform of the overall design, and comprehensively analyses the circuit under different working modes by VIVADO software. After calculation, the power consumption of the processor in three different working modes is reduced by 4%, 8% and 63% respectively in the normal mode. In the power consumption test of the FPGA board, the overall power consumption of the board in sleep mode is reduced by 19% in normal mode.

Key words:clock control; low power consumption; down frequency mode; sleep mode; shutdown mode