基于FPGA+SCV64架构的VME总线从模块开发

白 煊1, 罗运虎1, 郑永龙, 周勇军

(1.南京航空航天大学 自动化学院,江苏 南京 210016;2.中国人民解放军第5720工厂 安徽省航空设备测控与逆向工程实验室,安徽 芜湖 241007)

VME总线概念最早源自于VERSA总线,被命名为VERSAbus-E,之后改名为VME总线。VME总线作为一种欧洲通用模块背板总线,具有高性能、支持多处理器计算机系统的特点。经过数十年的发展,坚固耐用的VME总线已拥有一大批成品制造商,被广泛应用于军事、医疗、交通运输以及工业控制系统中。

由于VME总线已被应用在新型飞机上,故它将会被越来越多的人关注。许多学者都对其展开了相关研究。文献[1]和文献[2]基于ARM或PowerPC等处理器,实现VME总线控制器功能;文献[3]阐述了VME接口协议芯片SCV64的应用概况。文献[4]采用FPGA设计了DFT1总线数据采集方案。文献[5]则利用FPGA实现VME总线控制器功能。文献[6]和文献[7]通过FPGA解析了VME总线信号数据。

目前飞机检修过程中,分解的VME模块无法完成单个数据通信检测,因此本文在对VME总线通信规范深入了解的基础上,基于“SCV64+FPGA”架构,开发了VME总线从模块,可与待检测VME模块构成数据通路,从而为航电部件检修奠定基础。

1 模块硬件设计

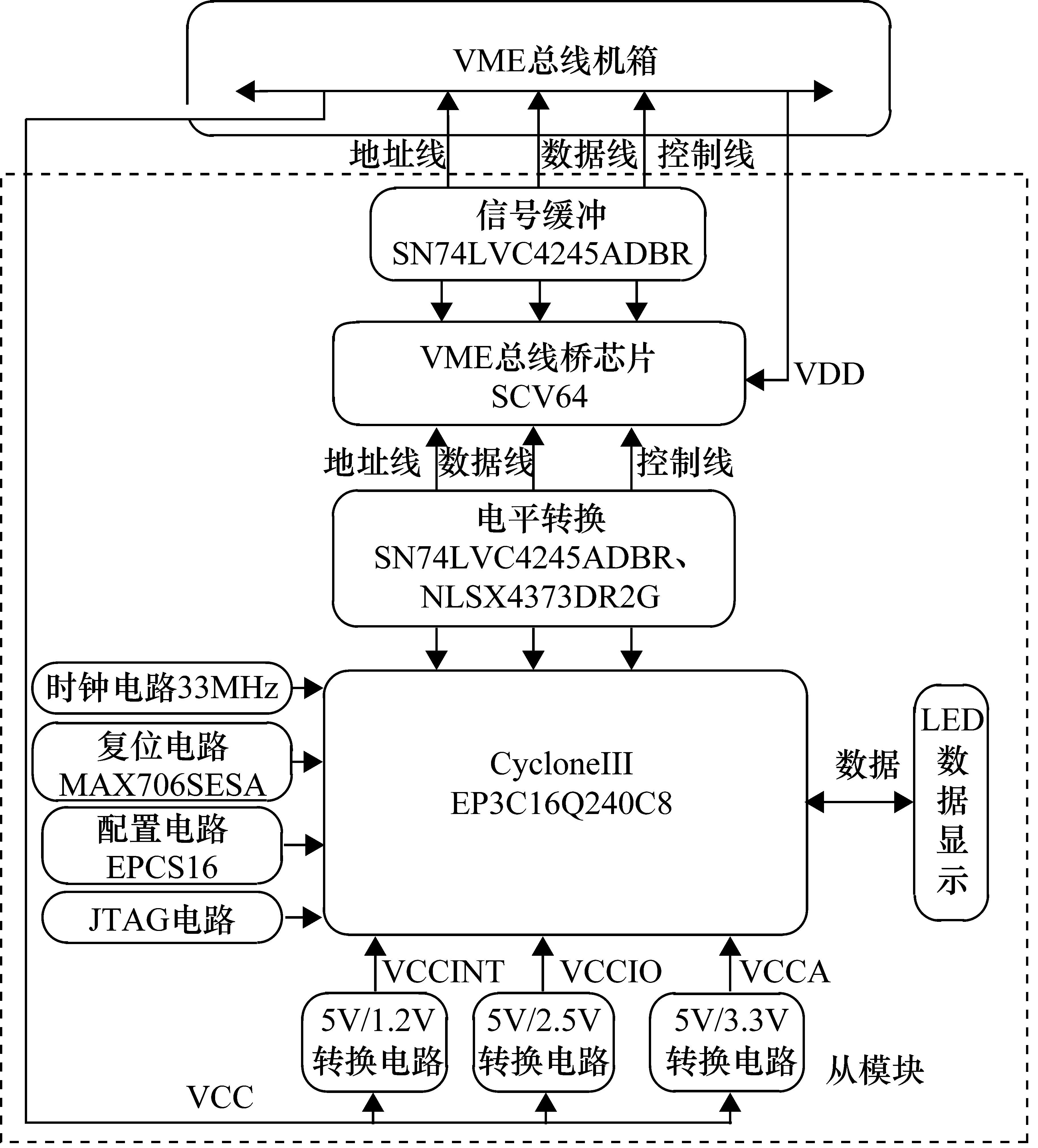

所研制的VME总线通信模块可以在VME主控板发起传输后,接收VME主控板发出的数据,并通过LED指示灯显示当前操作读写的数据内容,其架构如图1所示。

图1 模块硬件结构框图

1.1 FPGA最小系统电路设计

① 供电电压电路设计。所选FPGA为EP3C16Q240C8,其供电电压主要包括VCCINT、VCCIO和VCCA。其中VCCINT为内核电压1.2 V;VCCIO为I/O电压3.3 V;VCCA为PLL的模拟供电电压2.5 V。

② 复位电路设计。复位电路由MAX706SESA芯片构成。MAX706SESA是一款微处理器监控芯片,可监控3~5 V电平。比起早期的多个元件电路,其可靠性和精度都大大提高,常常作为上电、下电时复位电平输出。

③ 配置电路设计。由于Cyclone系列FPGA是SRAM结构,断电后FPGA的配置信息就会丢失,需要重新使用JTAG接口下载配置信息,或者使用配置器件在重新上电时对FPGA进行自动配置。所采用的FPGA配置芯片为EPCS16。

1.2 SCV64外围电路设计

早期VME总线桥接控制器多采用VIC068A或VIC64。VIC系列的接口器件兼容性差,且只提供8位地址和数据通道,使用很不方便。SCV64是Tundra公司生产的VME总线接口。其功能灵活,可以为各种VME数据环境制定接口。

SCV64利用VME接口在总线间实现解耦传输和耦合传输。解耦传输:VME主模块向SCV64数据传输结束后即释放VME总线,之后由SCV64完成数据向本地总线传输;耦合传输:VME主模块向SCV64数据传输结束后不释放VME总线,在SCV64完成数据向本地总线传输后VME总线才被释放。

SCV64的VME总线接口需要通过8位转换器对VME总线的地址、数据、地址修正信号以及数据选通信号进行缓冲。8位转换器的方向由SCV64的VADDROUT、VDATAOUT、VSTRBOUT信号控制。VADDROUT控制地址线A31~A00、LWORD;VDATAOUT控制数据线VDATA31~VDATA0;VSTRBOUT控制VAS、VDS1、VDS0、VER、VAM5~VAM0。本设计采用SN74LVC4245ADBR作为信号缓冲。

SCV64本地接口提供了总线请求仲裁,若不需要此仲裁过程可以绕过本地总线仲裁。在PWRRST信号的上升沿期间保持KBGACK为低,可以绕过SCV64本地总线仲裁。

可以通过上电时序使SCV64本地接口仅为从器件使用,该选项使SCV64能够自动初始化所有需要访问VME总线的内部寄存器。

上电复位信号PWRRST上升沿时,需要保持KDS为高电平,SCV64采样KFC0和KFC2信号,若KFC0为低电平、KFC2为高电平,则SCV64进入从器件模式。此时SCV64会读取本地总线数据端口的输入值,利用此值配置VMEBAR寄存器。

VMEBAR寄存器中存储了SCV64作为VME从模块的基地址与从窗口的范围大小。VME从窗口映射可通过24位(A24)或32位(A32)地址线访问,不能通过16位地址访问。A32窗口基地址可以被设置为128 MB(地址线0~26位)内的任意值,窗口范围在4~128 KB之,A24窗口可以被设置为小于16 MB的512 KB倍数大小。在本地总线上SCV64驱动低位地址线匹配VME从地址空间。而高于可配置从空间大小的地址线KADDR31~KADDR27将不被驱动,其余未使用的地址线被驱动为低电平。当VME主设备发起的传输地址属于该从窗口范围时,则判定对该从模块进行传输。SCV64将VME从窗口地址映射至本地总线,本地总线起始地址0x0对应VME从模块基地址,本地总线终止地址为从窗口的范围大小。

为配置SCV64为从模式并绕开本地仲裁,本设计通过4.7 kΩ电阻上拉信号KFC1、KFC2、KDS、KAS、KBERR至5 V;通过4.7 kΩ电阻下拉KFC0、KBGACK至地;短接本地总线申请信号KBRQ与授权KBGR;通过10 kΩ电阻上拉BG3IN*信号至5 V。

通过NLSX4373DR2G与SN74LVC4245ADBR将SCV64的5 V电平信号转换为3.3 V与FPGA连接。

2 模块软件设计

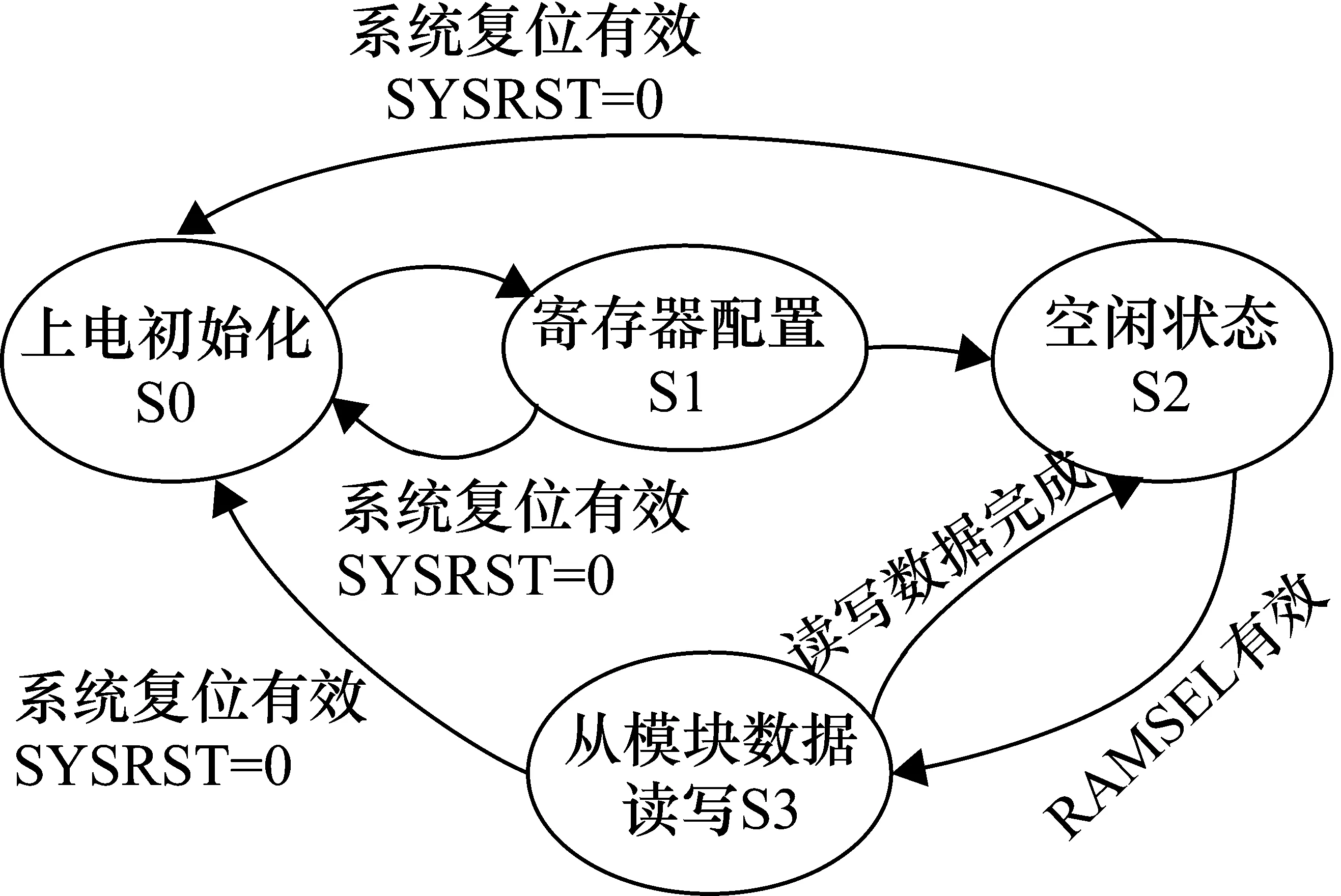

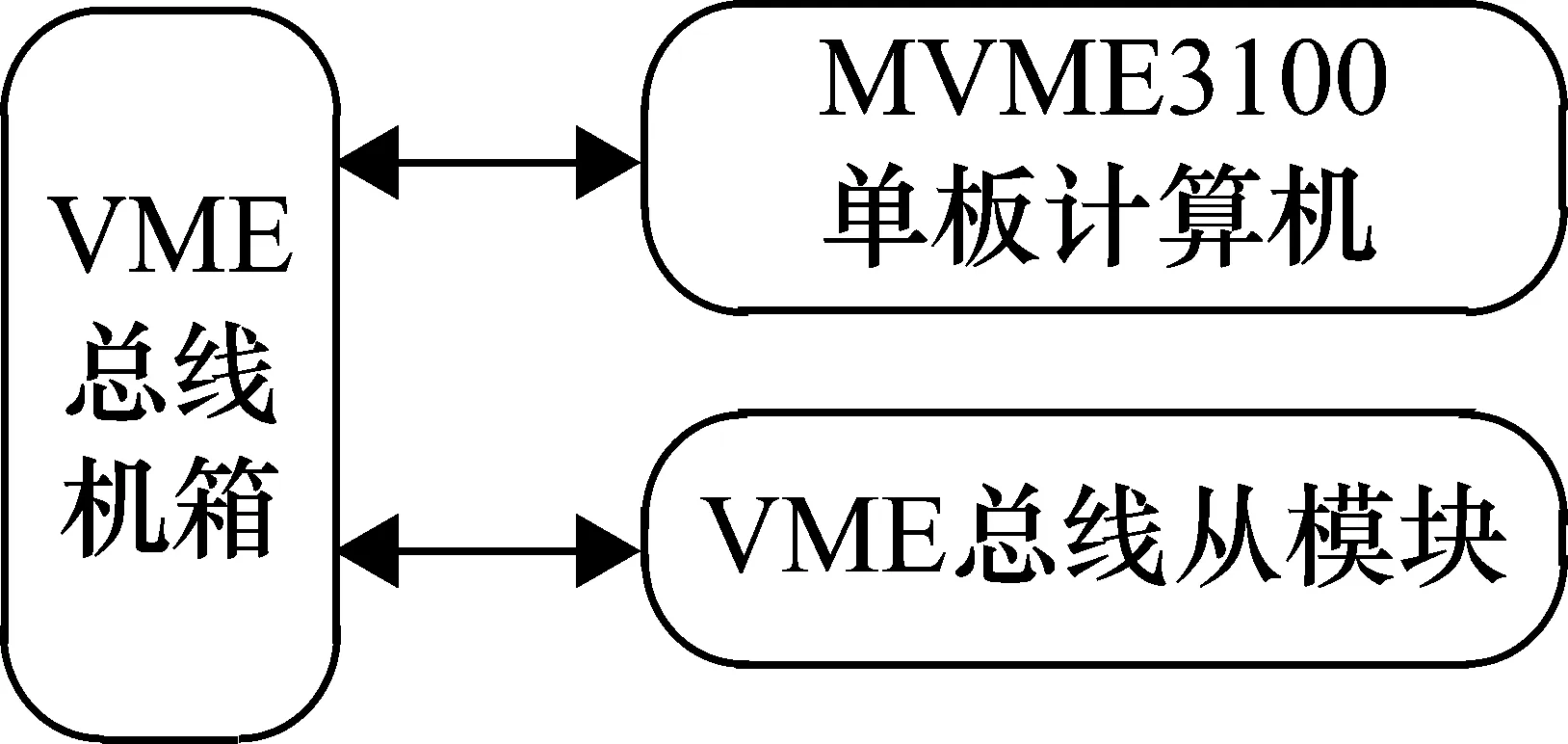

图2为软件整体工作状态机。S0为上电初始化状态,S1为MODE寄存器配置状态,S2为等待数据传输状态,S3为从模块数据传输状态。

图2 从板程序状态机

2.1 上电初始化、寄存器配置(S0、S1)

VME系统主器件通过基地址以及以基地址起始的从空间范围来区别操作各个系统中的模块,图2中S0状态为上电初始化状态,在此状态上电复位信号PWRRST由有效变为无效出现上升沿,此刻FPGA将在SCV64的本地端口数据信号线(KDATA)上输出寄存器VMEBAR值,并自动配置MODE寄存器中的从窗口使能位。本设计中配置VME从空间地址宽度为32位,大小为1 MB,基地址为0x08000000。将VME空间全部映射至从模块32位LED数据,对该VME地址空间读写全部反映至32位LED数据。

VME读取从设备SCV64中数据必须为耦合传输;VME向从设备SCV64写数据可以为耦合传输也可为解耦传输。SCV64的MODE寄存器中的RXATOM位和TXATOM位默认读写FIFO的模式皆为解耦传输,需要通过图2中S1状态利用本地接口访问SCV64的MODE寄存器进行修改。MODE寄存器地址为:32′h0000003C。这里不改变该寄存器其他位默认值,所以写入寄存器值为:32′h00001C01。

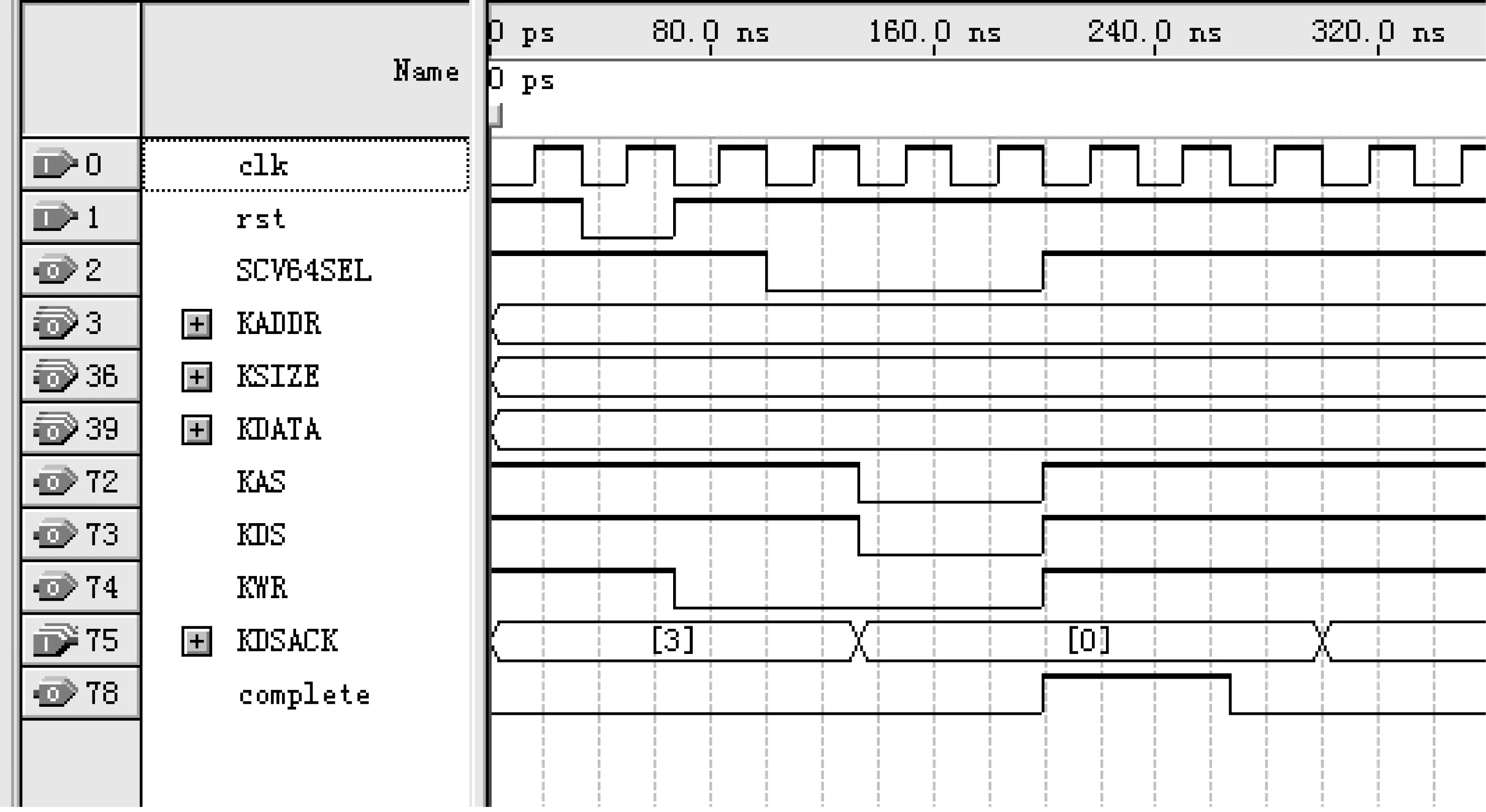

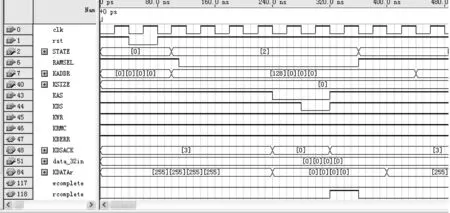

图3为MODE寄存器配置流程,首先FPGA驱动KWR信号为低电平表示写入数据,驱动KADDR、KDATA为地址和数据;其次SCV64SEL片选信号输出低电平,表示访问SCV64内部寄存器;之后KAS地址有效信号输出低电平,KDS数据有效信号输出低电平;最后等待KDSACK信号低电平有效,表示寄存器写入成功。图4为MODE寄存器配置仿真。

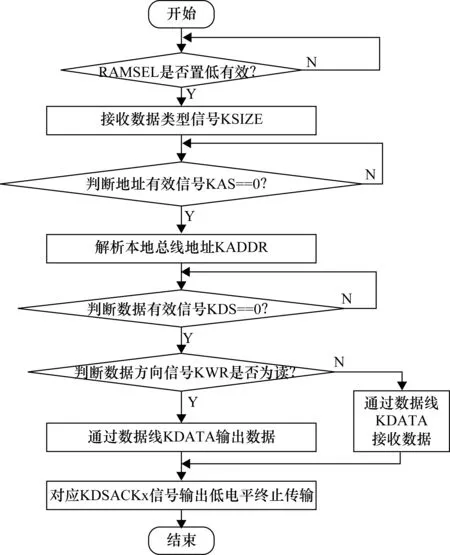

2.2 从模块数据读写(S3)

修改完成后若SCV64读取VME总线传输地址在自己的从窗口范围内,则从模块开启传输过程。存储片选信号RAMSEL低电平有效,FPGA程序进入图2中S3状态。图5为从模块传输逻辑流程。通过SCV64本地接口信号KSIZE读取数据宽度、KWR信号读取数据传输方向。当KAS信号低电平有效时,可读取KADDR信号在VME总线映射至本地总线的地址。当KDS*低电平有效时,若为写入数据可通过KDATA读取数据,若为读取数据可通过KDATA发送数据。在数据传输完成后,本地总线通过低电平有效KDSACK信号终止传输。图6、图7分别为从模块读、写传输仿真,读传输中,KDATAr默认值为32位高电平(仿真显示256进制数:255 255 255 255),读出数据位32位低电平;写传输中,KDATAw默认值为32位低电平(仿真显示256进制数:0 0 0 0),读出数据位32位高电平。

图4 MODE寄存器配置仿真

3 模块测试验证

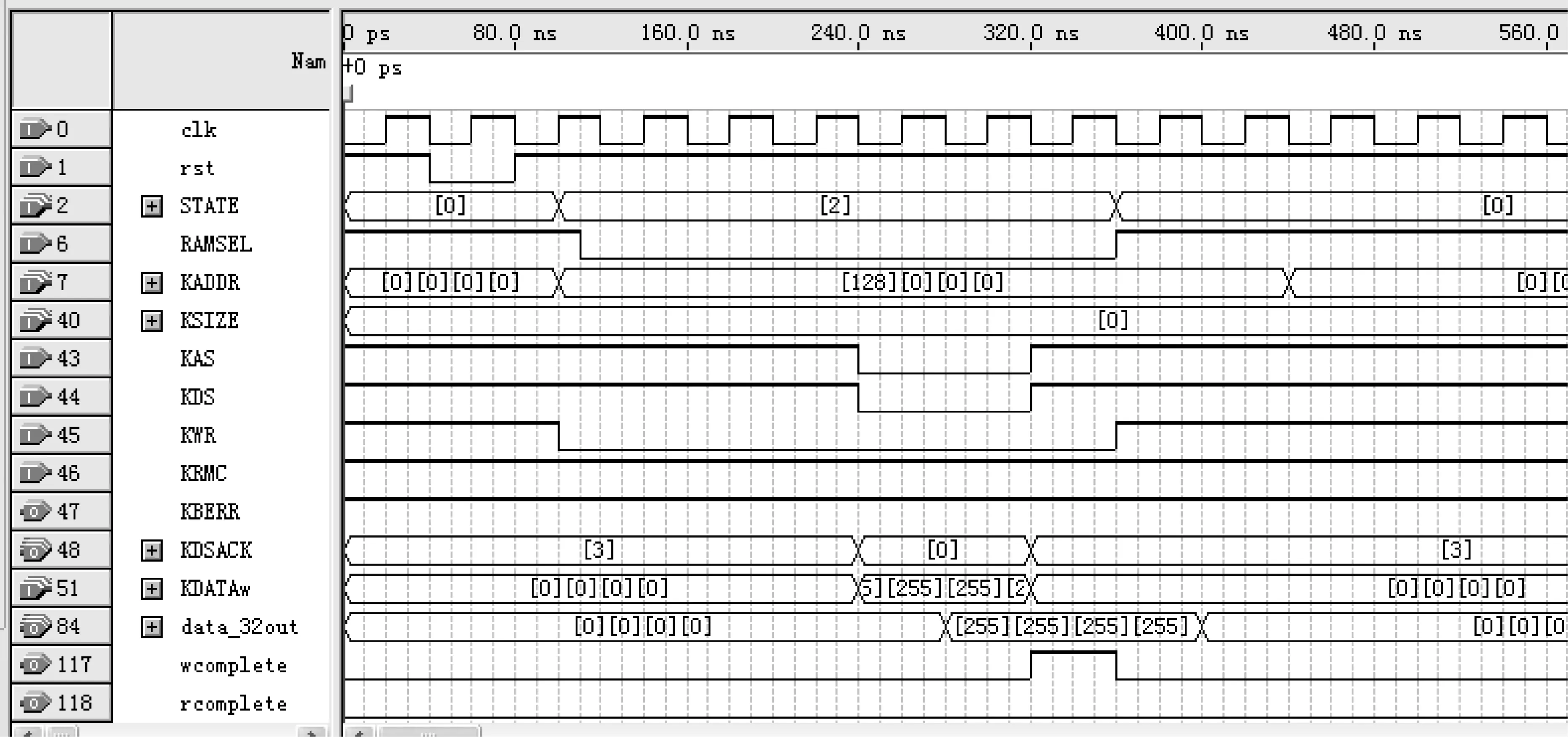

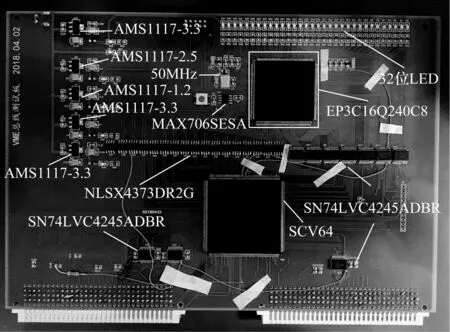

运用MVME3100作为VME总线主控模块,运行VxWorks操作系统,通过开发主机对MVME3100进行控制。可通过主机利用VxWorks开发工具Tornado的shell控制MVME3100发起传输。在39E系列VME测试开发平台机箱内进行测试。图8为VME总线从模块正面,图9为VME总线从模块背面。图10为模块测试框架。

3.1 测试条件

① MVME3100单板计算机。本实验运用MVME3100作为VME总线主控模块,发起针对VME总线从模块的数据传输。MVME3100单板计算机采用了MCP8540处理器,不仅仅提供了更快的VME总线传输速率,内存子系统、本地总线和I/O子系统的平衡性也更好。

图5 从模块传输逻辑流程

图6 从模块读传输仿真

图7 从模块写传输仿真

② 软件条件。本实验利用Tornado开发环境中的shell工具对MVME3100进行命令操作。Tornado是WRS公司推出的一套实时操作系统开发环境,界面风格类似Microsoft Visual C,但是较之后者提供了更丰富的调试、仿真环境和工具。其中的shell工具允许下载应用程序模块,调用VxWorks及应用程序模块的子程序。shell虽然运行在开发主机上,但它允许对目标机发起任务,读出或写入目标设备。

图8 VME从模块正面

图10 模块测试框架

3.2 测试步骤

① 通过网口与串口连接开发主机与MVME3100。在开发主机中运行FPT通信协议,启动MVME3100。

② 在开发主机中打开Tornado启动目标机MVME3100,即可通过shell对MVME3100进行操作。

③ 调用函数“sysTempeWinShow”得到MVME3100中PCI地址窗口与VME地址窗口间的映射关系。

地址空间Outbound window0为系统为操作mailbox寄存器预留的空间,不可通过其访问VME地址空间。所以通过地址空间Outbound window1读写VME地址空间数据。

空间Outbound window1:

PCI起始地址:00000000_80000000;PCI终止地址:00000000_800fffff

VME起始地址:00000000_08000000;VME终止地址:00000000_080fffff

④ 输入命令“d+PCI地址”(d 0x80040000)读取栈地址空间Outbound window1中数据。

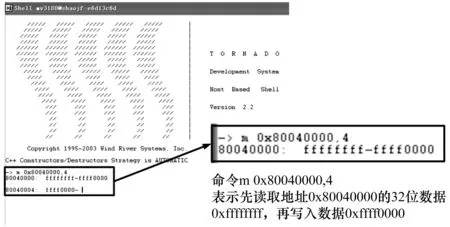

⑤ 输入命令“m+PCI地址”(m 0x80040000)改写Outbound window1中数据,即向对应VME空间地址发送数据。

3.3 测试结果

通过MVME3100向从模块LED发送数据0xffff0000。图11为Tornado下shell命令读取并写入内存空间地址0x80040000,原数据为0xffffffff。再通过读取内存空间地址0x80040004读取LED数据。图12为LED显示写入从模块数据。从图中不难看出从模块数据读写的有效性。

图11 MVME3100发起读写数据0xffff0000

4 硬件设计与软件开发注意事项

4.1 硬件设计方面

① 为保证信号稳定,SCV64需要通过8位转换器对VME总线的地址、数据、地址修正信号以及数据选通信号进行缓冲。

② 为防止SCV64在VME总线系统中被配置为主控模式,BG3IN*信号不与总线相连,而应通过10 kΩ电阻上拉至VDD;

③ 为保证SCV64正常工作,在上电复位PWRRST上升沿期间,要KDS保持高电平,因此KDS管脚需要通过4.7 kΩ电阻上拉至VDD。

④ 为保证菊花链通畅,需要短接总线信号BG3IN*与BG3OUT*。

4.2 软件开发方面

① 为保证软件运行过程中,SCV64保持硬件配置,上电复位PWRRST仅在上电复位时有效一次,之后的任何系统复位都不应造成PWRRST有效,PWRRST复位信号复位SCV64中全部硬件配置。

② 在不同操作中,FPGA与SCV64间的信号传输方向不同。为使传输正确,应注意SN74LVC4245ADBR的方向控制信号的切换。

③ 访问SCV64内部寄存器时,需选通SCV64SEL片选信号。

④ 由于SCV64硬件模式在软件运行中没有更改,程序上电初始化和寄存器配置状态,仅在系统整体复位时运行。

5 结束语

为满足后续新机VME总线模块电路板深修的需要,针对目前VME总线的研究现状,基于SCV64这款VME接口协议芯片,研制一块具有接收VME总线信号读写操作的从模块。所研制的VME总线从模块为后续丰富VME总线数据功能系统的搭建和完善打下了坚实基础。