GaAs功率芯片AuSn20共晶焊接技术研究

任卫朋 刘凯 罗燕 陈靖 余之光

摘 要:针对GaAs功率芯片共晶焊接工艺中,因焊接空洞、虚焊致使芯片烧毁的问题,对AuSn20共晶焊接技术进行研究。通过自动共晶设备,对共晶温度曲线参数进行实验分析。结果表明,共晶温度曲线设置260℃、320℃的温度梯度可以保证焊料的充分融化、浸润,共晶熔融时间控制在15-30s可以形成适量的IMC层。对优化后的共晶焊接面进行热阻分析,在满负荷条件下,功率芯片最高节温为93℃,满足小于125℃的要求,说明共晶质量良好。

关键词:功率芯片;AuSn20焊料;共晶焊接

中图分类号:TN405 文献标志码:A 文章编号:2095-2945(2019)25-0109-03

Abstract: In order to solve the problem of chip burnout caused by welding cavity and virtual welding in the eutectic welding process of GaAs power chip, the technology of AuSn20 eutectic welding is studied. The parameters of eutectic temperature curve are experimentally analyzed by automatic eutectic equipment. The results show that the sufficient melting and infiltration of solder can be ensured by setting the temperature gradient of 260℃ and 320℃ in the eutectic temperature curve, and an appropriate amount of IMC layer can be formed when the eutectic melting time is controlled at 15~30s. The thermal resistance of the optimized eutectic welding surface is analyzed. Under the condition of full load, the maximum temperature saving of the power chip is 93℃, which meets the requirement of less than 125℃, indicating that the eutectic quality is good.

Keywords: power chip; AuSn20 solder; eutectic welding

1 概述

GaAs功率芯片由于具有體积小、带宽宽、一致性高等优点,在相控阵雷达、微波通信系统等领域发挥着重要的作用,成为雷达 T/R组件的关键器件[1]。功率芯片与基板的焊接质量直接影响组件整体的可靠性与电学性能,因此必须要有良好的微波接地性能与散热能力。共晶焊接由于具有焊接强度高、剪切力强、连接电阻小、传热效率高等优点,因此广泛应用于高频、大功率器件和LED等高散热要求的器件焊接中。

共晶是指在相对较低的温度下共晶焊料发生共晶物熔合的现象,共晶合金直接从固态变化到液态,而不经过塑性阶段,其热导率、电阻、剪切力、可靠性等均优于传统的环氧粘接[2,3]。本文主要对微波GaAs功率芯片,AuSn20共晶焊接温度曲线进行实验分析,通过扫描电镜研究合金层组织演变及界面,以此为基础对共晶焊接工艺进行优化。

2 试验方法

实验设备采用自动贴片机,压力控制为10g-250g,每次贴放均可编程控制,并具有压力实时反馈系统,热台为脉冲加热方式,具有实时温度检测系统。原材料清洗采用UV紫外光清洗机、BT等离子清洗机。

对于实验材料,不同尺寸的AuSn20焊料片采用划片机进行机械切割[4],之后进行酒精超声清洗。垫块采用1:2:1的Cu/Mo/Cu垫块,表面溅射Ni、Pd、Au作为功率芯片的载体。垫块溅射完成后,依次经过酒精超声→烘干→紫外光清洗→等离子清洗工序后备用。芯片采用GaAs功率芯片。实验材料备好后以华夫盒形式放入贴片机供料台上,然后通过编程来控制温度曲线、压力、刮擦等参数,整个共晶过程由贴片机自动完成,减小人为因素影响。共晶完成之后测量剪切力。

3 实验结果分析

共晶温度曲线设定:

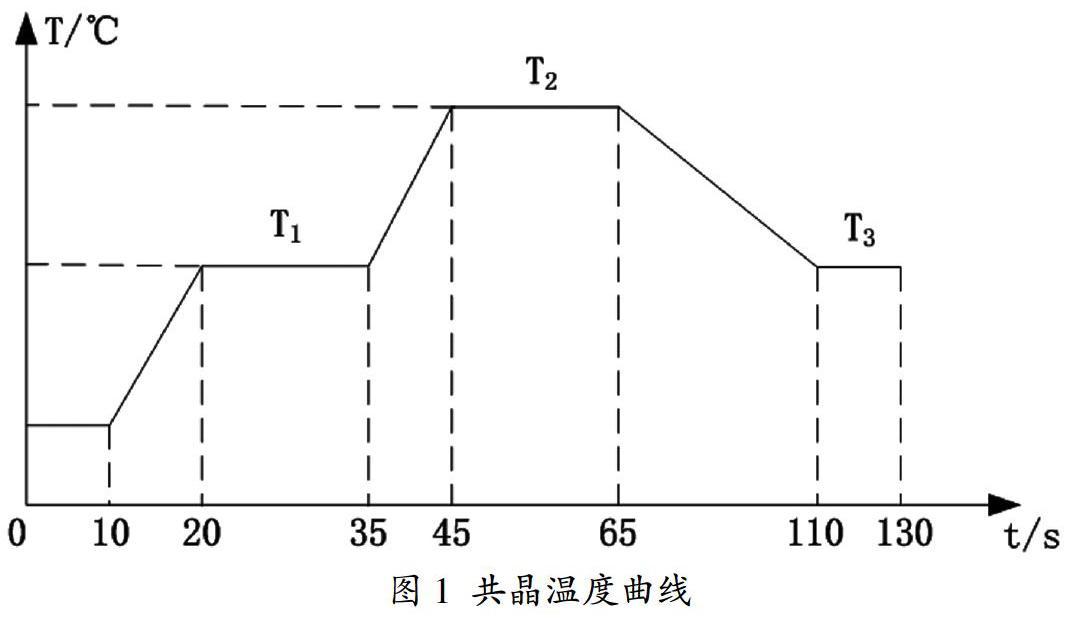

共晶温度曲线主要包括三个阶段:预热阶段、共晶阶段、冷却阶段。预热阶段主要作用是去除器件内水汽以及减小热失配应力;共晶阶段主要作用为共晶层熔融合金的形成,是共晶焊过程最重要的阶段;冷却阶段为共晶完成后器件散热降温过程,冷却温度及速率会影响器件内部残余应力的大小。典型温度曲线如图1所示。

其中,T1为预热温度,一般比共晶温度T2低30-60℃左右。T2为共晶温度,T3为冷却温度,可设置为200-260℃。由于共晶温度T2对共晶层质量影响最为显著,对于T2采用单因素对比试验进行确定。试验结果分析可知,热台温度为320℃时焊料完全熔融,可进行共晶焊接,为了增加AuSn焊料浸润性、流动性,在金锡共晶焊时将共晶温度设为320-330℃。

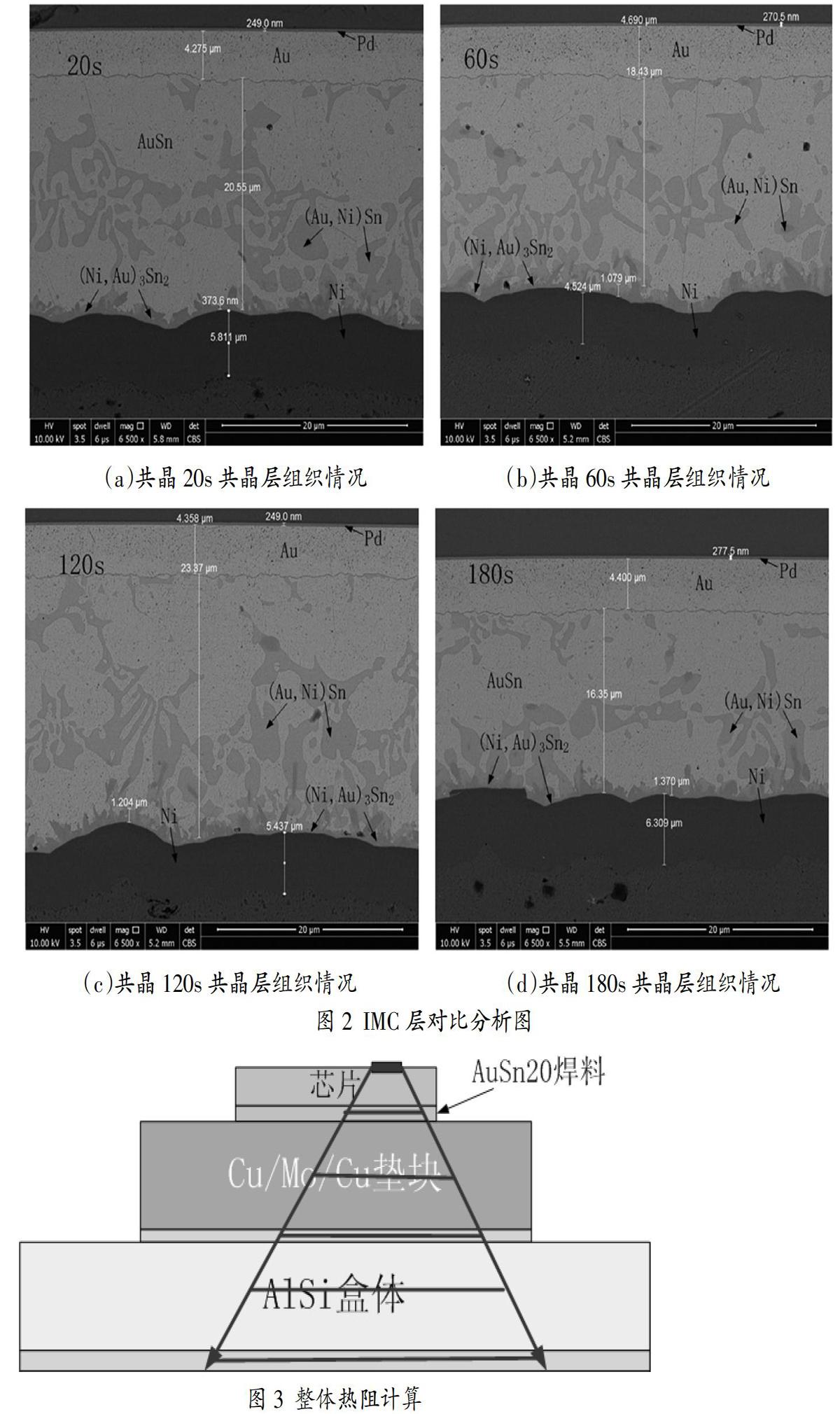

另外,对于共晶温度T2保持时间,通过对比试验,使用扫描电子显微镜(COXEM EM-30)观察不同T2时间下共晶层组织情况,试验结果如图2所示。

通过对比分析发现,随着共晶时间的增加,IMC层厚度由0.373μm逐渐增至1.370μm,共晶160s之后IMC厚度增长缓慢。通过能谱分析可知,在焊料/镍界面处形成由(Au,Ni)Sn和(Ni,Au)3Sn2组成的IMC复合层。分析可知,在共晶过程中,合金Ni元素逐渐向AuSn合金层扩散,使合金组织中固溶了少量Ni的(Au,Ni)Sn层逐渐增大,这导致IMC层的增长[5]。(Ni,Au)3Sn2层的增长会消耗焊料中的(Au,Ni)Sn,因此到一定时间后,(Au,Ni)Sn层含量不再明显变化而(Ni,Au)3Sn2逐渐增加。固态反应时金属间化合物(IMC)的厚度与共晶熔融时间的平方根成正比,如下式所示,其中K为比例系数。

共晶焊接中異质金属的连接需要IMC来实现,因此一定厚度的IMC层有助于提高焊接质量。但是IMC层为一种脆性化合物,过厚的IMC层会显著降低焊接的剪切强度[6]。为保证形成适量厚度的IMC层,控制整体共晶时间为2-3min,其中共晶熔融时间为15-30s,此条件下IMC层厚度可控制在0.3μm-0.9μm之间,共晶芯片剪切强度超过9.15kgf,符合GJB548B-2005要求。

4 测试验证

共晶焊接相对于环氧焊接优势在于其热阻更小,能满足大功率芯片的散热要求,因此共晶焊接的热阻情况十分重要。对于共晶焊结构的热阻,可通过热阻公式进行分析[7]:

其中,R为热阻值,h为焊料层厚度,K为AuSn20焊料热导率,S为焊料横截面积。

对于整体结构热阻,其模型如图3所示。分析过程按有源区扩散传热计算,按45°扩散计算,截面积按有效面积计算,即梯形面的中间剖面长宽积计算(粗实线所示),焊料面按有效面积计算,最后可得整体热阻为3.2259℃/W,比环氧贴片热阻减少58%。

共晶完成后,进行实际加电检测,测量共晶结构的散热性能。对共晶芯片进行加电检测,通过热成像仪测试芯片表面节温,如图4所示。芯片三级放大区域产热较集中,因此此区域温度较高。在满负荷条件下,功率芯片最高节温为93℃,满足小于125℃的要求,说明共晶质量良好。

5 结论

本文针对GaAs功率芯片共晶焊接中空洞、虚焊问题,通过扫描电镜分析合金层组织演变及界面,对共晶温度曲线进行实验分析,结果表明,共晶温度曲线设置260℃、320℃的温度梯度可以保证焊料的充分融化、浸润,共晶熔融时间控制在15-30s可以形成适量的IMC层。对优化的共晶焊接面进行热阻分析,在满负荷条件下,功率芯片最高节温为93℃,满足小于125℃的要求,说明共晶质量良好。

参考文献:

[1]庞婷,王辉.真空共晶焊接技术研究[J].电子工艺技术,2017,38(1):8-11.

[2]霍灼琴,杨凯骏.真空环境下的共晶焊接[J].电子与封装,2010,10(11):11-14.

[3]夏艳.3D集成的发展现状与趋势[J].中国集成电路,2011,146:23-28.

[4]胡永芳,姜伟卓,丁友石,等.芯片共晶焊接焊透率测量系统改进研究[J].现代雷达,2010,32(11):97-100.

[5]贾耀平.功率芯片低空洞率真空共晶焊接工艺研究[J].中国科技信息,2013(8):125-126.

[6]张建宏,王宁,杨凯骏,等.真空共晶设备的改进对共晶焊接质量的影响[J].电子工业专用设备,2010,39(10):44-47.

[7]KELLER F,HUNTER M S,ROBINSON D L. Structural features of anodic oxide films on aluminum[J].J Electrochem Soc,1965,100:55-56.