CMOS片上无源电感的Q值提升电路

戴强 杨格亮

摘 要:片上无源电感是射频集成电路中广泛使用的重要器件,它决定着一些关键组成电路的主要性能指标。但CMOS衬底的高电导率特性使片上无源电感的损耗变大、Q值降低。为了解决这个问题,一种基于有源负阻架构的片上无源电感Q值提升电路在文中被提出。利用该电路不但可以在较宽的频率范围内大幅提升片上无源电感的Q值,还能够使电路的等效感值在有效带宽内仍取决于无源电感本身。

关键词:CMOS;片上电感;Q值

中图分类号:TN432文献标识码:A

在成本、集成度和功耗等方面因素的推动下CMOS技术已经获得了前所未有的发展。然而,在射频电路设计方面由于普通CMOS工艺的低电阻率衬底导致了无源电感的低Q值,这在很大程度上限制了一些射频电路,如:低噪声放大器、压控振荡器和滤波器的工作性能。

国内外对片上无源电感Q值优化的研究主要是基于对硅基无源器件损耗机理的认识,这种损耗主要有三个来源:[1]金属的欧姆损耗、介质的极化损耗和半导体硅衬底与金属电磁耦合形成的损耗。因此,为优化电感的Q值可以采用降低金属欧姆损耗的方案,如:增加线宽、使用高电导率金属做导线、多层金属并联[2]等;或采取在电感下方放置屏蔽层来降低金属—衬底耦合损耗的方案;[3]还可以采用改变元件形状的方案,[4]这种方案利用的原理是面积一定、形状越接近圆形的正多边形周长越小。因此,虽然器件的Q值得到了小幅提升,然而感值却下降了。

除了直接对片上无源电感的Q值进行优化外,还可以利用CMOS负阻电路设计高Q值的有源电感替代无源电感,但这种应用非常有限。主要是由于传统有源电感的通用性较差,需要同时调节晶体管的尺寸和电流来改变所需频率处的Q值,而且晶体管尺寸的改变会导致感值的改变。利用相同有源电感架构在不同频率处实现高Q值的电路设计过程既复杂又困难。

为了克服现有技术在优化无源电感Q值方面的不足,本文基于感性有源负阻电路的架构,提出一种射频无源电感的Q值提升电路,利用感性有源负阻电路的特性将其与无源电感并联,融合它们各自的优点,在所需频率处抵消无源电感的寄生电阻而保持无源电感的感值基本不变,最终实现无源电感Q值的大幅提升。

1 电路设计

为解决上述技术问题,本文通过以下电路设计来实现:一种射频无源电感的Q值提升电路,其特征在于:包括第一NMOS晶体管M1、第二NMOS晶体管M2、第三NMOS晶体管M3、第四NMOS晶体管M4、有损射频无源电感器L、电阻器R和直流电流源I。

直流电源VDD分别连接电感器L的一端、电阻器R的一端和第四NMOS晶体管M4的漏极,电感器L的另一端分别连接第三NMOS晶体管M3的漏极、第四NMOS晶体管M4的栅极和射频无源电感的Q值提升电路的引出端,电阻器R的另一端连接第三NMOS晶体管M3的栅极,第三NMOS晶体管M3的源极分别连接第一NMOS晶体管M1的漏极和第二NMOS晶体管M2的栅极,第四NMOS晶体管M4的源极分别连接第二NMOS晶体管M2的漏极和第一NMOS晶体管M1的栅极,第一NMO0S晶体管M1的源极和第二NMOS晶体管M2的源极连接在一起后接在直流电流源I的一端,直流电流源I的另一端接到直流地。

其中,所述的第二NMOS晶体管M2的栅宽与栅长之比均大于第一NMOS晶体管M1和第三NMOS晶体管M3的栅宽与栅长之比;第四NMOS晶体管M4的栅宽与栅长之比均大于第一NMOS晶体管M1和第三NMOS晶体管M3的栅宽与栅长之比。

2 电路实现

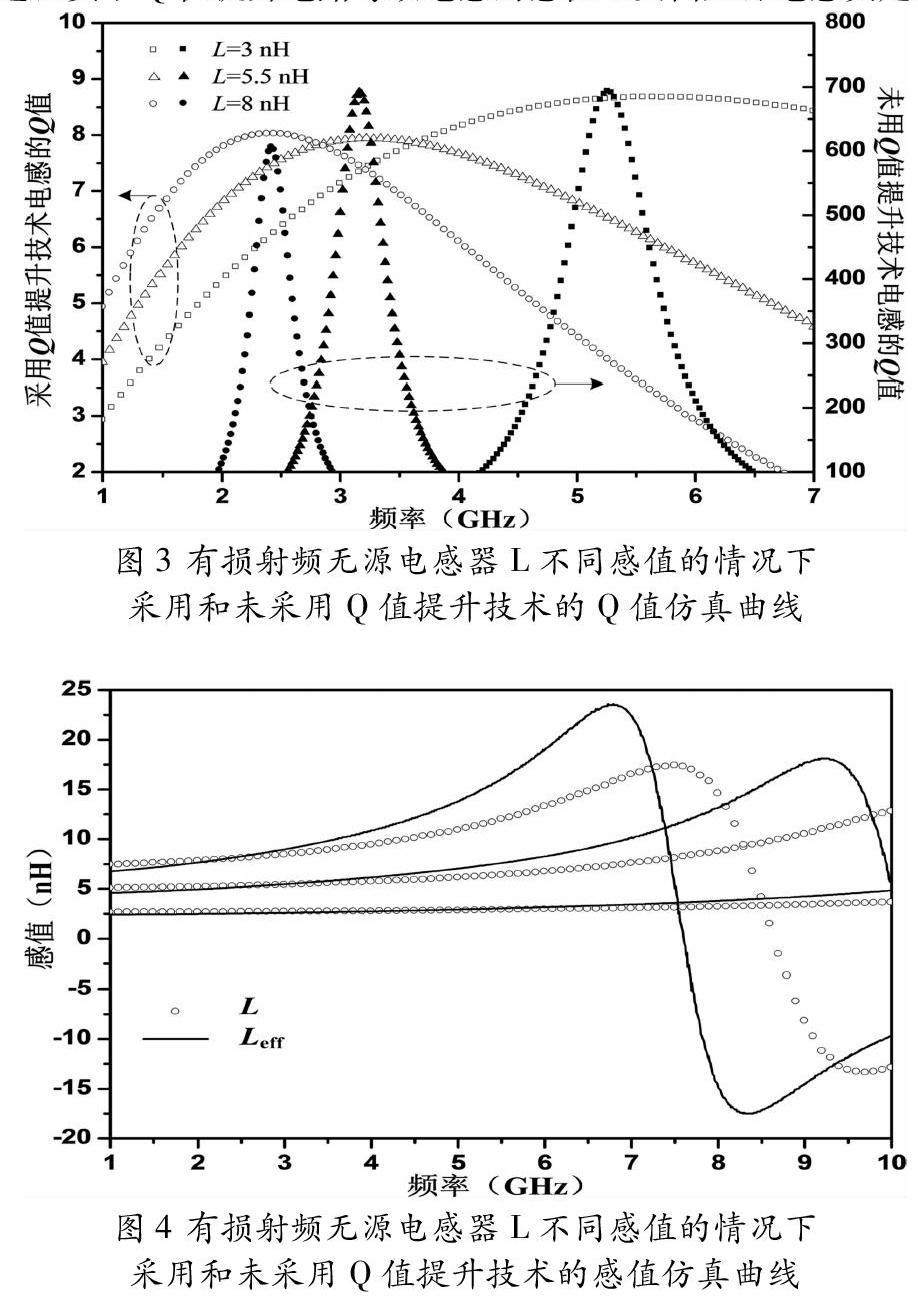

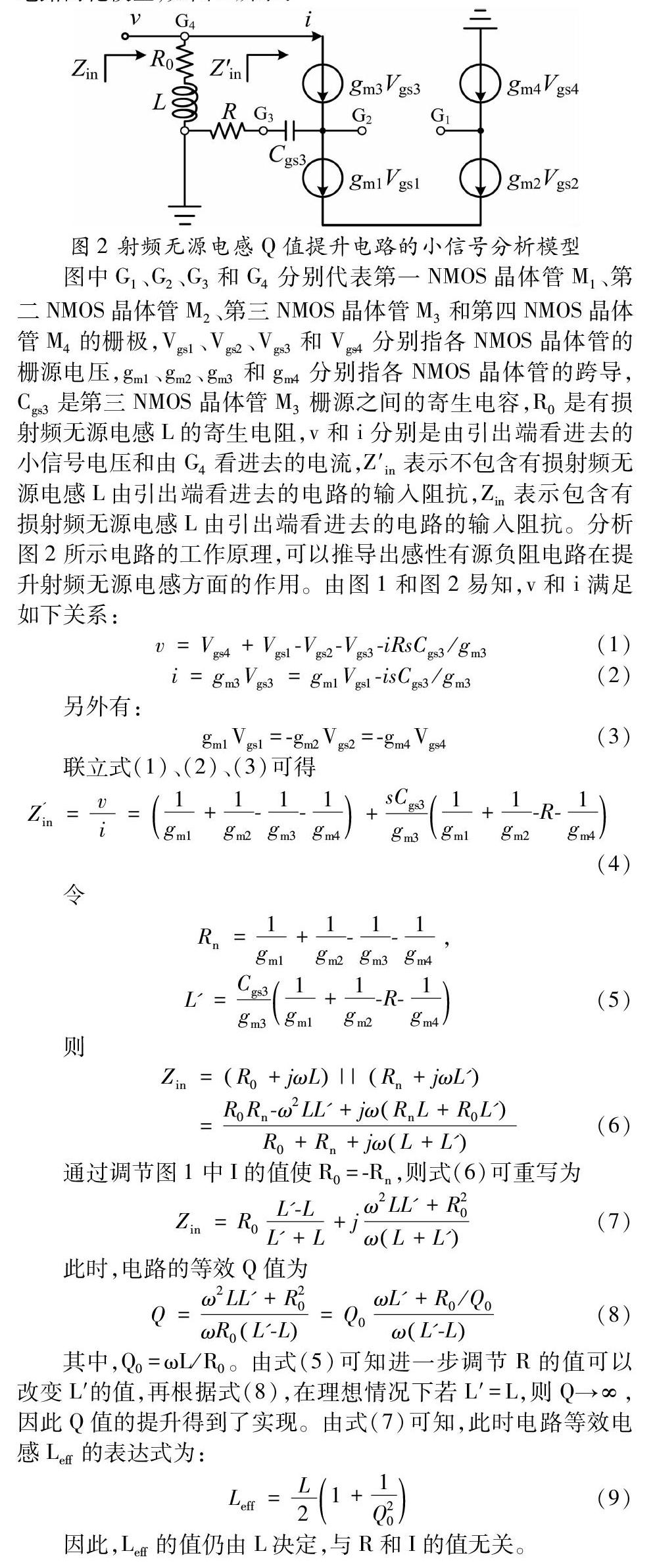

本文利用四个NMOS晶体管、电阻器R和直流电流源I组成一个有源感性负阻电路以改善与之并联的有损射频无源电感器L的Q值。参看图1,所提出的射频无源电感Q值提升电路包括第一NMOS晶体管M1、第二NMOS晶体管M2、第三NMOS晶体管M3、第四NMOS晶体管M4、一个有损射频无源电感器L、一个电阻器R和一个直流电流源I,第一NMOS晶体管M1和第二NMOS晶体管M2相互连接成交叉互耦对,即:直流电源VDD分别连接电感器L的一端、电阻器R的一端和第四NMOS晶体管M4的漏极,电感器L的另一端分别连接第三NMOS晶体管M3的漏极、第四NMOS晶体管M4的栅极和射频无源电感的Q值提升电路的引出端,电阻器R的另一端连接第三NMOS晶体管M3的栅极,第三NMOS晶体管M3的源极分别连接第一NMOS晶体管M1的漏极和第二NMOS晶体管M2的栅极,第四NMOS晶体管M4的源极分别连接第二NMOS晶体管M2的漏极和第一NMOS晶体管M1的栅极,第一NMOS晶体管M1的源极和第二NMOS晶体管M2的源极连接在一起后接在直流电流源I的一端,直流电流源I的另一端接到直流地,从引出端看进去该射频无源电感Q值提升电路实际上形成一个新的有源电感电路。

第二NMOS晶体管M2的栅宽与栅长之比均大于第一NMOS晶体管M1和第三NMOS晶体管M3的栅宽与栅长之比;第四NMOS晶体管M4的栅宽与栅长之比均大于第一NMOS晶体管M1和第三NMOS晶体管M3的栅宽与栅长之比。NMOS晶体管尽量采用CMOS工艺所支持的射频管,栅长选工艺能够支持的最小尺寸;根据有损射频无源电感L自身的Q值峰值频率初步设定第一NMOS晶体管M1~第四NMOS晶体管M4的总栅宽,再通过改变电阻器R和直流电流源I的值对有损射频无源电感L的Q值及其峰值频率进行细调。

利用四个NMOS晶体管和直流电流源I组成一个负阻可以精细调节的感性有源负阻电路,负阻通过改变直流电流源I的值进行调节,电阻器R跨接在第三NMOS晶体管M3的栅极和直流電源VDD之间用来调节Q值的峰值频率,从引出端看进去的Q值提升电路的感值由跨接在引出端和直流电源VDD之间的无源电感的感值决定。

根据图1所示射频无源电感Q值提升电路的结构,按所有NMOS晶体管栅长为0.18μm,第一NMOS晶体管M1的总栅宽4.5μm、第二NMOS晶体管M2的总栅宽10.2μm、第三NMOS晶体管M3的总栅宽4μm和第四NMOS晶体管M4的总栅宽10.5μm配置好晶体管的尺寸,电阻器R和直流电流源I的值根据有损射频无源电感L的值来选取。