混合忆阻器-CMOS逻辑运算的优化设计研究

冯朝文,白 鹏,杨晓阔,危 波

(空军工程大学 基础部,陕西 西安 710051)

0 引 言

传统CMOS技术[1]发展由于受到各种物理限制变得越来越困难,因此需要其他方法来制造更高性能的内存和逻辑应用程序,其中一个可行的候选新器件是忆阻器。1971年,Chua根据电荷与磁链的关系推测出存在第四种基本电路元件,并把该元件命名为忆阻器[2]。2008年,HP实验室的Williams团队制备出一种二氧化钛纳米级器件在物理上实现了忆阻器,并把这一成果发表在《Nature》期刊上,随后成为物理和电子技术界内的研究热点[3]。忆阻器以其优异的非易失性、抗疲劳性强、能耗低、工作速度快、集成度高以及与CMOS工艺兼容性等优点[4-7],广泛应用于电路设计[8]、混沌系统[9]、非易失性存储器[10]和神经网络[11]等领域。

忆阻器的数字电路设计和应用一直是一个热点研究方向。忆阻器可用于逻辑电路[12-13]、逻辑阵列[13-14],以及其他如PLA、PMLATLA[13,15]、忆阻器-CMOS混合[16-17]、FPGA类忆阻器系统[18-19]等。研究人员对不同的忆阻器组合行为(并行、反并行、串联和反串联)进行了详细研究,发现忆阻器可以用于构成实质蕴含操作的逻辑门设计[12]。但是,这类设计中的“与”“或”“非”逻辑门需要多个实质蕴含操作步骤,运算比较复杂且消耗大量时间,易造成计算误差累计[15]。另外,与传统CMOS技术相比,忆阻器-CMOS混合电路虽然具有功耗低、物理面积小、运行速度快等优点[5-6],但这类逻辑电路由于潜通路存在信号衰减问题,并随着电路规模的增大,可能导致逻辑混乱和故障[17]。因此,忆阻器的逻辑电路设计需要折中考虑到结构、面积、功耗、运算速度、性能优劣等多种因素。文中基于忆阻器模型的特点,分析指出基本已有忆阻器-CMOS混合逻辑门设计存在的缺陷,进而提出一种通过变型逻辑运算表达式对应改进电路结构的方案解决信号衰减这一问题。

1 混合忆阻器-CMOS逻辑门及其信号衰减分析

忆阻器是一种二端元件,本质上是描述磁链和电荷之间关系的器件,而实际电路设计和应用中,通常反映了电压和电流之间一种连续动态变化关系,其瞬时电阻取决于流过它的电流的历史。忆阻器的极性用粗黑线表示,当电流从极性端流向忆阻器另一端时,忆阻器的电阻减小;反之,电阻增大,如图1所示。

图1 忆阻器符号

纳米交叉线存储器是集成忆阻器件中最常见、最成熟的电路结构,且读写纳米交叉线存储器多用于实现集成状态逻辑函数运算[20-23]。状态逻辑运算是由HP实验室[12]提出的,它利用忆阻器的电阻状态来表示逻辑运算的输入和输出。这类结构普遍存在潜通路问题,泄漏电流会干扰正确的读写操作,使得位线电压不能达到正常电压值,不同位线之间的串扰也影响正常的运算过程。对于潜通路电流问题的一种可能的解决方案是将不相关的字线连接到一个固定电压上进行保护,使得每个位线的电压电平相互独立。但在这种情况下,该固定电压本身会影响位线的电压值。因此,应谨慎选择该固定电压值,使其对操作过程的影响尽可能小[21]。另一种解决方案是将一个双向二极管串联在每个忆阻器上,隔离所有不相关的忆阻器,但这将导致更复杂的电路结构和更高的硬件成本[22]。

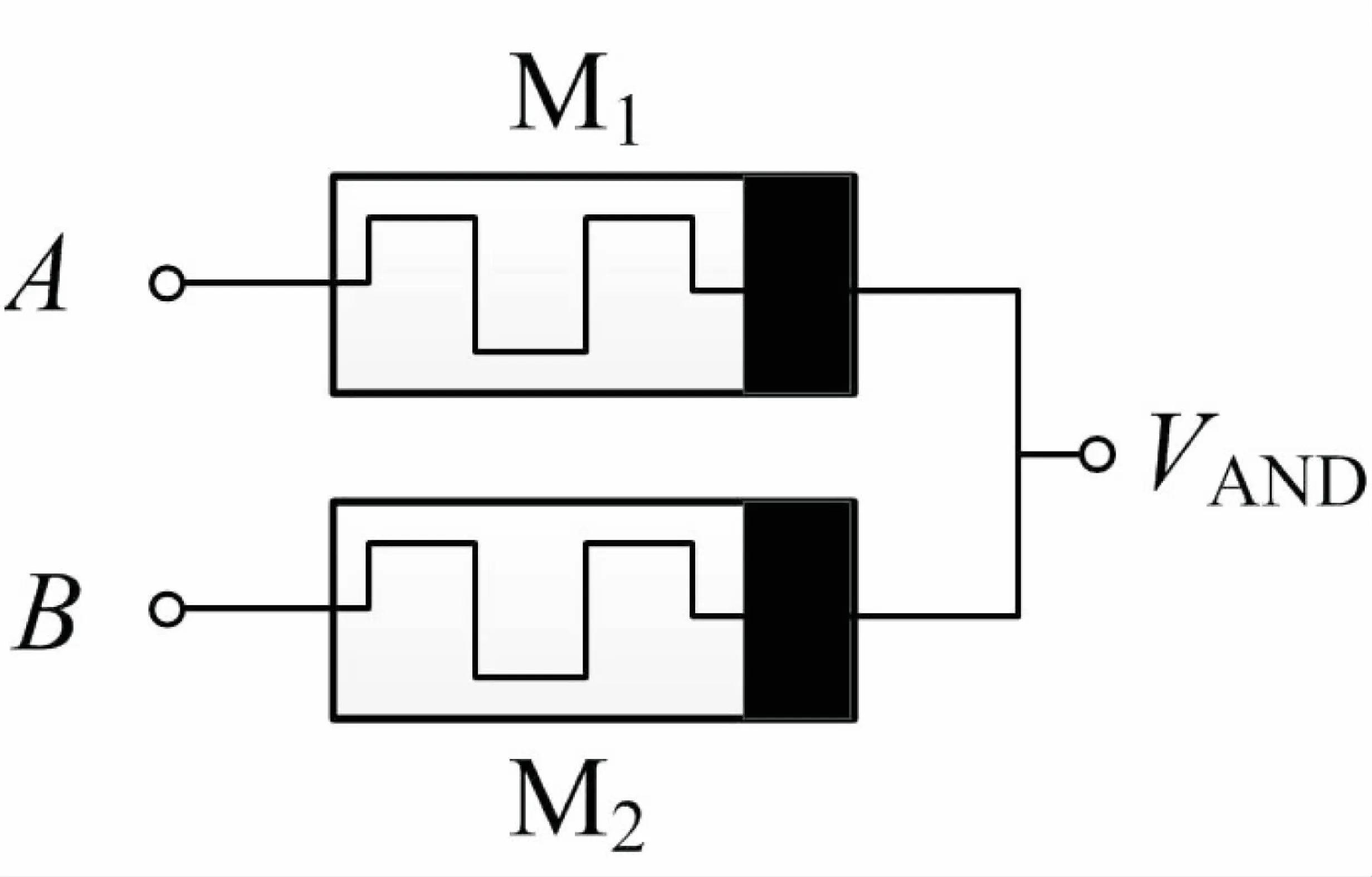

忆阻器与CMOS混合的逻辑电路或系统设计与应用也是一个研究热点。文献[7]最早提出忆阻器-CMOS混合逻辑电路并进行一系列逻辑门设计。基本的布尔逻辑运算“与”和“或”逻辑门是由两个忆阻器按照极性反向串联而成,如图2(a)、(b)所示。A和B是两个忆阻器M1和M2的输入信号,VAND和VOR是输出信号。

如果将两个逻辑门的输入A和B同时设定为逻辑态1(或0),即两个输入端均与高电平VCC相连(或均接地),由于串联的忆阻电路中没有电流流过,所以VAND和VOR将输出高电平(或低电平),即逻辑态1(或0)。

如果输入端A和B设定为相反的逻辑状态,即A=1,B=0或A=0,B=1。

前一种情况,A接高电平VCC,B接地。对于“与”逻辑门而言,电流从忆阻器M1流向M2,M1的电阻逐渐增大到Roff,M2的电阻逐渐减小到Ron(这里Roff与Ron分别为忆阻器的最大值和最小值)。由欧姆定律以及串联电路电压分配关系,当Roff远大于Ron时(Roff>10Ron),VAND输出低电平,即逻辑态0。对于“或”逻辑门而言,M1的阻值逐渐减小到Ron,忆阻器M2的阻值逐渐增大到Roff,VOR将输出高电平,即逻辑态1。

后一种情况,电流则从M2流向M1,分析方法相同,VAND输出低电平,即逻辑态0,而VOR将输出高电平,即逻辑态1。

忆阻器模型有电流阈值型[23]和电压阈值型[24],相比于电流阈值型,电压阈值型更利于逻辑电路或阵列的设计和信号控制。

电压阈值型开关忆阻器数学模型[25]方程如下:

dR/dt=f(VM(t))W(R,VM(t))

(1)

f(VM(t))=β(VM(t)-0.5(|VM(t)+VT|-

|VM(t)-VT|))

(2)

W(R,VM(t))=θ(VM(t))θ(Roff-R)+

θ(-VM(t))θ(R-Ron)

(3)

其中,R为忆阻器电阻;VM(t)为忆阻器两端电压;VT为阈值电压;参数β为描述电阻变化率的正值常量;f(·)为建模忆阻器阈值电压特性的函数;W(·)为窗函数;θ(·)为忆阻值在[Ron,Roff]范围内变化的阶梯函数。

设置参数:β=1014,VT=0.2 V,b=10-5,Roff=20 kΩ,Ron=1 kΩ,VCC=1.8 V。以逻辑输入A=0101和B=1100为例,利用PSpice电路仿真软件对“与”逻辑门和“或”逻辑门进行功能仿真,可以得到各自输出的暂态响应功能波形,如图2(c)所示。

(a)“与”逻辑门设计图

(b)“或”逻辑门设计图

(c)“与”“或”逻辑门暂态响应曲线

由图2(c)仿真结果可见,无论“与”逻辑门还是“或”逻辑门,当输入A和B均为高电平,即逻辑1时,输出逻辑为1,且对应输出高电平非常接近1.8 V,与输入电压基本相等。当输入A和B均为低电平,即逻辑0时,输出逻辑为0,对应的输出低电平为0 V。但当A和B两个输入逻辑态不同,即A=0,B=1或A=1,B=0时,“与”逻辑门输出逻辑0对应的低电平信号减弱,明显大于理想输出状态0 V,而“或”逻辑门输出逻辑1对应的高电平信号也减弱,明显小于理想输出状态1.8 V,因而产生了逻辑输出信号衰减现象,对应于图中椭圆虚线圈标注区域。这对于逻辑门多级互联设计非常不利。究其原因,当输入端逻辑态不同时,两个忆阻器中有电流通过,对互联的下一级逻辑门会产生电流泄露,进而引起本级逻辑输出发生一定误差。由于误差累计效果,最终导致逻辑门多级互联时输出发生逻辑混乱甚至出错。

忆阻器-CMOS混合逻辑电路的“非”门是由CMOS反相器实现,进一步结合忆阻器构成的“与”和“或”逻辑门就可以设计任意二进制逻辑运算电路。在基于忆阻器-CMOS混合设计的典型逻辑电路中同样存在级间互联的逻辑信号衰减问题。图3所示为基于混合忆阻器-CMOS的“异或”和“异或非”典型逻辑门设计图及其功能仿真曲线。其中,参数设置同图2,逻辑输入设为A=0101,B=1100。

(a)“异或”逻辑设计图

(b)“异或非”逻辑设计图

(c)“异或”“异或非”暂态响应输出曲线

由图3(c)可见,两个逻辑门的输入端无论是哪种逻辑态组合,输出端的逻辑态电平都会产生信号衰减现象,对应于图3(c)中椭圆虚线圈标注的区域。

2 降低信号衰减的逻辑电路新设计

忆阻器在逻辑电路中潜通路泄露电流的存在关系着电路逻辑信号处理的正确性以及传输的准确性,影响着运算功能及其性能优劣,所以忆阻器逻辑电路的设计非常重要。

CMOS反相器是数字逻辑电路中的一个基本逻辑电路模块,具有放大和反相功能,可以实现逻辑运算的“非”功能。在电路级联时,CMOS反相器可当作级间信号隔离器,使前后级信号不发生衰减或使信号衰减减小,又可以实现信号的恢复。因此,为了解决基于忆阻器-CMOS逻辑电路中的信号衰减问题,文中提出一种改进基于混合忆阻器-CMOS的“异或”、“异或非”等基本典型逻辑门结构的设计方案,即变换逻辑运算表达式,在电路输出端连接CMOS反相器并进行结构优化,实现对输出信号的恢复,从而降低甚至消除信号衰减。

2.1 “异或”和“异或非”逻辑门新结构设计

在数字逻辑电路中,逻辑函数的表达式决定了电路的拓扑结构,不同的表达式对应不同的电路结构。例如,“异或”和“异或非”逻辑门的经典表达式为式4和式5。观察分析表达式,两者最后一步逻辑操作均为“或”逻辑,由上一节对于忆阻器-CMOS典型逻辑电路研究可知,输出信号发生衰减将不利于多个逻辑门互联。

(4)

(5)

如果将逻辑表达式进行变形,令最后一步操作为“非”逻辑操作,对应可用CMOS反相器实现。因此,可将式4和式5分别变形为:

(6)

(7)

根据变形表达式,文中提出了“异或”和“异或非”逻辑门的新设计结构,分别如图4(a)和(b)所示。与图3(a)和(b)所示电路相比,虽然忆阻器和CMOS反相器的数量相同,但CMOS反相器作为逻辑门输出端,一方面完成“异或”和“异或非”的最后一步“非”逻辑操作,另一方面可以确保输出信号不发生衰减。

(a)“异或”逻辑门设计图

(b)“异或非”逻辑门设计图

2.2 全加器新结构设计

基于忆阻器的“与”“或”逻辑门和改进后的“异或”“异或非”基本逻辑门可以实现混合忆阻器-CMOS的任意逻辑电路功能。全加器是二进制逻辑电路的基本运算模块,也是复杂数字逻辑运算的基础。文中基于上述四个逻辑门设计一种新的一位全加器电路结构。

设A和B为二进制逻辑输入,Cin为进位输入,S为求和输出,Cout为进位输出,考虑到“异或”逻辑门在全加器结构中的重要作用,以及每一步组合逻辑运算以“非”为逻辑输出,全加器的逻辑运算表达式可设计如下:

(8)

(9)

进而由逻辑表达式可设计出一位全加器的电路结构,如图5所示。该电路由两个“异或”门、一个“与”门、三个“非”门构成,结构优化前后器件数量不变,复杂度不变,但优化后的信号输出准确性将得到有效提高。

图5 改进后的一位全加器设计结构

3 改进后的忆阻器-CMOS逻辑电路的仿真验证

设置忆阻器模型参数:β=1014,VT=0.2 V,b=10-5,Roff=20 kΩ,Ron=1 kΩ,VCC=1.8 V。假设逻辑输入A=0101和B=1100,利用PSpice电路仿真软件对改进后的“异或”逻辑门和“异或非”逻辑门进行功能仿真,得到输出暂态响应曲线,如图6所示。与图3(c)相比较,改进后提出的新设计电路逻辑输出分别为1001和0110,逻辑操作功能正确,输出信号衰减很少,高低电平分别达到了1.8 V和0 V。

图6 “异或”“异或非”逻辑门改进新结构的暂态响应波形

假设逻辑输入为A=01010101,B=11001100,进位输入为Cin=11110000,电路参数设置同图6,对图5所示一位全加器改进电路进行功能仿真,可以得到暂态响应输出波形,如图7所示。

图7 提出的一位全加器功能暂态响应波形

由图7可见,全加器仿真逻辑运算求和输出S=01101001,进位输出Cout=11010100,逻辑功能正确,波形上除了在逻辑运算转换时有一些尖峰毛刺波动现象外,暂态响应没发生信号衰减现象;无论对于求和输出信号S还是进位输出信号Cout,逻辑输出高电平接近1.8 V,低电平近似0 V,提出的一位全加器结构能正确执行逻辑运算功能,验证了所提出的降低输出信号衰减方案是有效可行的,为进一步由基本逻辑门和全加器构建大规模组合逻辑电路提供新设计思路。

4 结束语

忆阻器作为第四种基本电路元件,已成为微纳集成电路领域的重要候选者。忆阻器在逻辑电路方面虽然具有天然优势,但目前仍存在一些需要解决的问题,其中潜通路泄露电流作为一个重要因素影响着逻辑功能的正确性以及电路集成化设计。文中通过研究四种典型的忆阻器—CMOS混合逻辑电路揭示了其信号衰减现象甚至逻辑混乱的工作机制,忆阻器输出端的电流泄露是造成信号输出衰减的主要原因。进而提出一种降低信号输出衰减的方法,将CMOS反相器作为逻辑门级输出,通过变形逻辑表达式,以“非”逻辑运算传递级间信号,避免流经忆阻器的电流发生泄露,从而解决了信号衰减问题。这一方法通过改进设计“异或”、“异或非”和一位全加器的新结构得到了仿真验证,不仅避免了多个逻辑电路级联时的输出信号衰减现象,而且为下一步完善大规模逻辑电路设计及其应用奠定了基础。