基于信号完整性的高速PCB优化设计与研究

袁为群,宋建远,陈世荣

(1. 崇达技术股份有限公司,广东 深圳 518132;2. 广东工业大学 轻工化工学院,广东 广州 510090)

电子信息产业进入5G时代带来新一代印制电路板的设计开发[1],PCB的设计密度也在不断增加,保证信号完整性成为高速数字PCB设计的重点关注问题[2]. PCB板设计则是高速数字电路设计中保证高速电路运行安全性的最关键因素[3]. 这需要PCB在产品前端设计和工艺上进行重点研究. 郑常斌[4]通过分析串扰和反射的形成机理,得出解决PCB上的串扰和信号反射等信号完整性的方法和设计规则. 秦德淳等[5]探讨了阻抗匹配的原因、目的,以及应用于电路设计的一些经验法则. 王磊[6]借助阻抗设计软件对电路板传输线的导线宽度、导线间距、填充截至进行仿真,使阻抗匹配以保证数据的高速传输. 张华[7]基于电磁建模仿真结合电路系统的分析方法,试图建立设计规则用来指导高速电路的设计. 滕丽[8]对互连通道的微带线和过孔创建仿真模型,并通过数据眼图评估传输通道的信号质量. 这些研究论文主要从信号完整性分析、PCB设计、过孔仿真对信号完整性的某方面进行阐述,至于信号传输线在制造过程中会出现什么具体问题少有论及.

本文将结合信号完整性的串扰、反射和电磁干扰的分析方法,分析高速PCB设计中存在的铜桥、阻抗线和导通孔的制作问题,借助案例分析优化设计并进行试验证明,进而完善信号完整性设计规则,阐明高速PCB设计需要与可制造性相结合,以提升高速PCB的电气性能和信号质量.

1 相关理论

1.1 信号完整性

高频高速PCB传输速率20 Gbps以上,高速电路信号完整性分析在国内外受到广泛的重视. 从广义上讲,信号完整性指的是在高速产品中由互连线引起的所有问题,它主要研究互连线与数字信号的电压电流波形相互作用时其电气特性参数如何影响产品的性能. 电磁干扰、反射和串扰是信号完整性问题的3个主要方面.

(1) 电磁干扰EMI(Electron Magnetic Interference). 由基尔霍夫定律可知,第一电流总是在闭合回路中流动,第二回路电流总是从阻抗最小的路径通过,即信号从走线上流过,回流信号在走线下方的参考层中流过. 因此,控制EMI最重要的原则就是控制回路面积.

(2) 反射. 反射是指信号在传输线上的回波. 信号功率的一部分传输到线上并到达负载,一部分被反射了. 避免反射需要具备2个条件:第一,导线无限长;第二,导线必须是绝对均匀的. 当在参考层上存在着一个缝隙,一条阻抗受控的走线穿过了这个缝隙,回流信号一定会绕过这个缝隙,再次回到走线下方,从而使走线的整体形状发生改变,引起阻抗不连续.

(3) 串扰. 信号之间的耦合称为串扰,它是指当信号在传输线上传播时,因电磁耦合对相邻的传输线产生的不期望的电压噪声干扰,分为电容性耦合串扰和电感性耦合串扰. 当面对串扰问题时,可以把所有的敏感走线都设置为带状线[9].

1.2 高速PCB的阻抗控制

高速电路采用的元器件集成度高,速度快,引出端子多,密度高,层数至少16层,能控制传输线的特性阻抗[10]. 特性阻抗就是传输线和介质共同作用结果下的阻止电磁场变化传播的固有特性,因而和传输线的宽度、厚度、离参考层间距及介电参数等有关. 传输线的特性阻抗是影响信号品质的最重要因素,如果信号传播过程中阻抗始终保持一致,那么信号可以很平稳地向前传播. 当阻抗发生了改变时,信号能量中的一部分反射回来,信号传输的连续性就被破坏,将导致信号失真.

2 案例分析

客户设计了一款高速PCB板,做了V1.1,V1.2测试版本,20层通孔板,单板设计尺寸470 mm×416 mm,最小孔径0.25 mm且孔数5万个以上,板厚3 mm,采用低损耗高速板材,树脂塞孔和背钻工艺. 阻抗线公差很严格,例如内层差分线阻抗为90±4 Ω和100±5 Ω,外层差分线阻抗为100±6 Ω,孔阻抗 ≥83 Ω,这些阻抗控制都是难度很高的. 客户端把阻抗测试合格的样品组装后,信号完整性测试的结果并不理想. 经过分析和优化设计,解决了所有问题,最终升级为V1.3版本的22层盲孔板.

2.1 问题分析

任何阻抗突变都会引起电压信号的反射和失真,这使信号质量出现问题,只要信号的阻抗保持不变,就不会反射和信号失真,衰减效应是由串联和并联阻抗引起的. 阻抗不仅可以描述与信号完整性相关的问题,而且还可以得到信号完整性的解决方案和设计方案[11]. 虽然样品阻抗测试值在客户的要求范围内,但这并不一定表示信号完整性验证合格. 因为阻抗突变会引起信号反射失真或者耦合串扰,所以要从阻抗分析入手. 下文利用信号完整性的相关理论分析问题并给出解决方案.

2.2 高速电路的阻抗线设计及优化

阻抗线设计有单端线和差分线2种,单端线设计在内层的焊球阵列封装BGA(Ball Grid Array)区域下两过孔之间的夹线,阻值50±3 Ω,内层差分线(带状线)有90±5 Ω和100±5 Ω,外层差分线(微带线[12])有100±8 Ω. 前者出现的问题在于铜桥作为参考层带来的参考层不连续性,后者发生的问题在于内层差分线宽的控制和外层差分线设计过长带来的电路板可制造性不好.

2.2.1 地层铜桥设计与优化分析

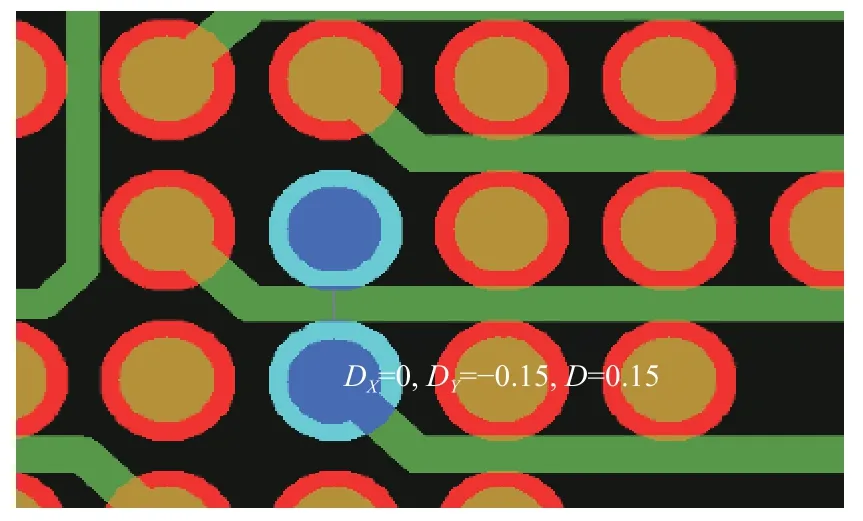

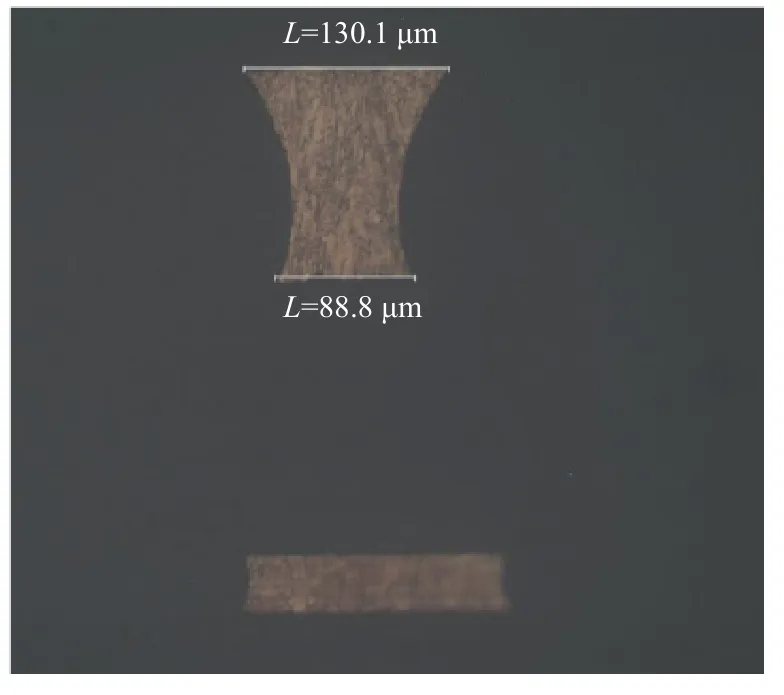

BGA区域单线用铜桥作为参考层,如图1所示,阻抗单线宽0.15 mm,对应的铜桥宽度0.15 mm,铜桥所在层的基铜厚140 μm. 根据参考层的有关理论,为了保持参考层连续性,该铜桥不允许取消或减小宽度. 在V1.1版本制作时,对铜桥要求理解不到位,导致单线阻抗测试不好,分析是铜桥加工出来的宽度不合格. 在PCB制造过程中,两焊盘(pad)之间的夹线在焊盘处缩小25 μm对整体阻抗没有影响[13]. 在V1.2版本制作时,削减反焊盘,增加铜桥宽度,减小阻抗线宽,如图2所示,其中DX表示X方向距离,DY为Y方向距离,D表示距离.

图 1 BGA区两过孔夹单线Fig.1 One line between 2 vias in BGA

图 2 BGA区两过孔夹单线设计优化后Fig.2 One line between 2 vias in BGA after optimization design

2.2.2 外层差分线设计与优化分析

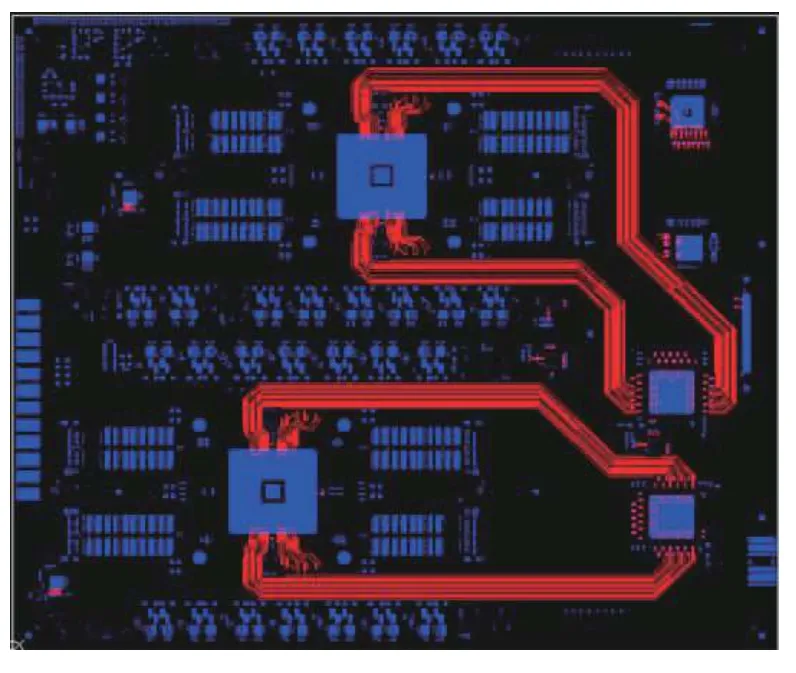

BGA区的外层差分线在V1.1、V1.2版本都设计为微带线,如图3所示元件面,图中红色为差分线,蓝色为差分线的参考层,左边大BGA的外层阻抗线直接与右边小BGA在外层相连. 采用这种设计电路制作的样品在组装器件后进行信号完整性测试结果并不好. 经过差分线阻抗值和线宽的分析,找到问题根源为电路板尺寸大,通过外层线路把2个BGA用阻抗线连接,则差分线长度360 mm. 而外层线宽的铜厚均匀性较内层差,蚀刻出来的线宽均匀性不好,引起左右两端阻抗差异大,因为高速PCB布线时有长距离走线,端端匹配阻抗不易设置[14].

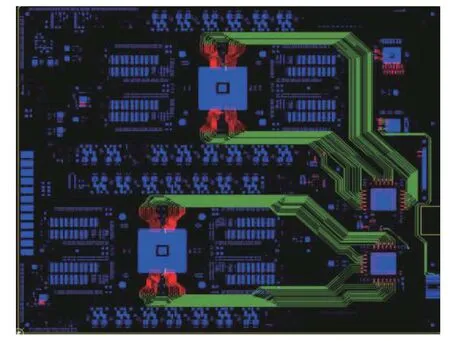

设计仿真表明,信号经过过孔的传输路径虽短,但过孔处特性阻抗对整个传输链路信号完整性有不容忽视的影响[15]. 过孔能起到线路转移的作用,过孔盲孔可做成微孔且传输路径短,有利于实现信号完整性. 在元件面的差分线上加0.15 mm机械盲孔和新增1个内层,通过盲孔把绝大部分的外层差分线转移到新增层L7;同理,焊接面的差分线转移到新增层L16. 这样就把通孔板改变为盲孔板并且层数由20层改为22层,设计为L1~L8和L15~L22盲孔,中间6层芯板,即“8+6+8”盲孔结构. 如图4所示,图中绿色部分为转移到内层L7的差分线. 优化设计后外层差分线长30 mm,大幅缩短原设计长度360 mm,比例不到9%.

图 3 2个BGA的外层差分线Fig.3 Outerlayer differential lines in BGAs

图 4 2个BGA外层+内层差分线的优化设计Fig.4 Outerlayer and innerlayer differential lines in BGAs after optimization design

2.3 高速电路的导通孔设计及优化

导通孔是PCB上的1个重要的阻抗不连续点. 当高速信号通过时,导通孔的寄生电容会造成信号上升时间延长,传输速度减慢,而寄生电感会消弱电源旁路电容的滤波功能,这样高频高速信号在电路板中流窜而引发串扰和EMI问题[16].

导通孔的寄生电容估算公式为

式(1)中,C为寄生电容(pF),T为PCB厚度(mm),Dk为介电常数,D1为焊盘直径(mm),D2为反焊盘直径(mm).

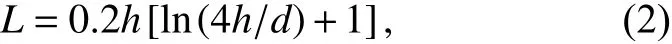

导通孔的寄生电感估算公式为

式(2)中,L为寄生电感(nH),h为导通孔长度(mm),d为导通孔直径(mm).

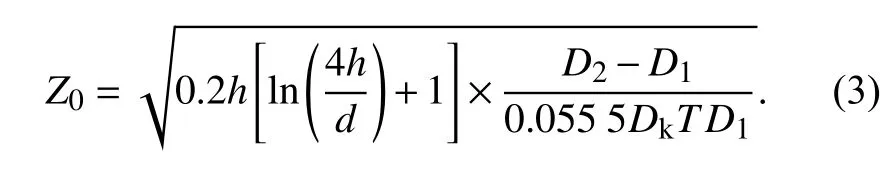

由式(3)可知,加大反焊盘D2或减小焊盘D1,或减小导通孔直径,可增大导通孔阻抗值[17].

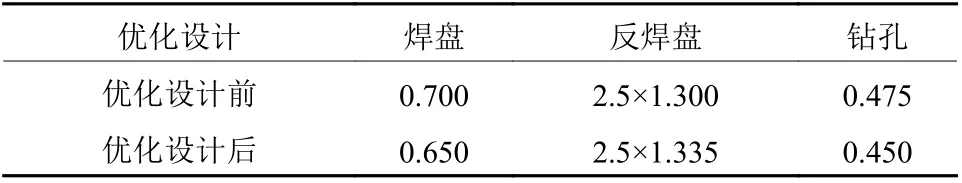

导通孔0.36±0.05 mm,孔阻抗 ≥83 Ω. 在V1.1和V1.2设计,孔阻抗在80 Ω左右,达不到83 Ω. 分析得出问题在于导通孔的反焊盘和焊盘尺寸设计上. 根据孔阻抗的公式,加大反焊盘,减小焊盘和钻孔直径. 优化设计前后数据见表1.

表 1 0.36 mm导通孔的优化设计参数Table 1 The design parameter of 0.36 mm vias mm

2.4 优化设计的试验结果及分析

进行优化设计前、后高速PCB样品制作,进行数据分析并验证升级后的优化效果.

2.4.1 地层铜桥的制作要求

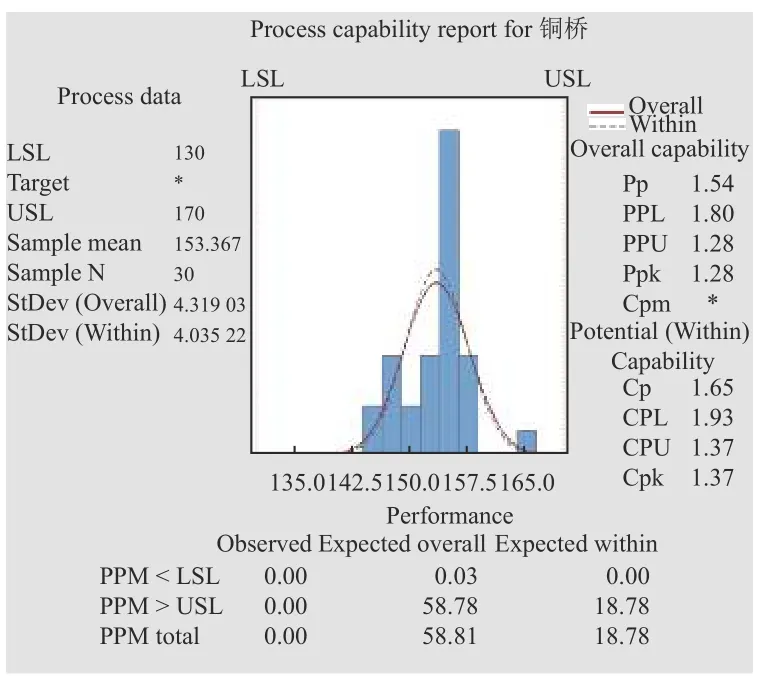

在V1.1样品加工时,切片分析铜桥的上线宽仅0.07 mm,下线宽0.125 mm,上下差值超过0.05 mm,这导致参考层的连续性变差. 对V1.2进行优化设计中,生产稿适当加大铜桥补偿值和削减反焊盘,改变蚀刻线的工艺参数,切片见图5,铜桥上线宽0.088 mm,下线宽0.130 mm,则上下宽度差值小于0.05 mm. 但减小过孔到铜桥的间距就增加了高层板的对位难度,对PCB厂家制作能力提高了技术要求. 铜桥制程能力分析用过程能力指数Cpk(Process Capability Index)表示,Cpk=1.37( ≥1.33),如图6所示,说明制程稳定可控.

为了保证铜桥作为参考层的有效性,先得确定铜桥的制作标准:下线宽为0.13±0.02 mm,上线宽至少0.08 mm. 这样才能保证单线阻抗值可控,客户端的信号完整性测试效果满足要求.

2.4.2 外层差分线的阻抗分析

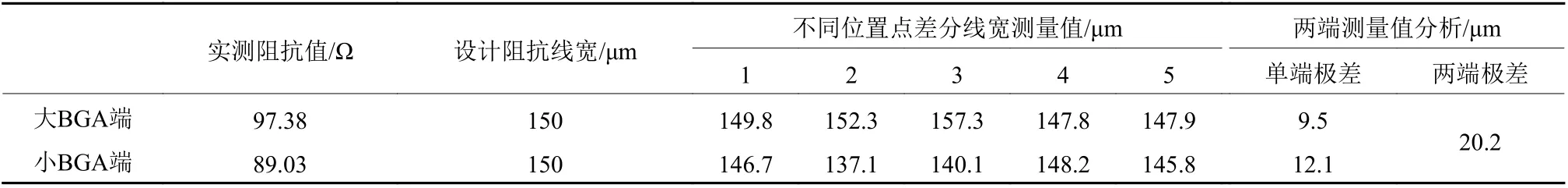

外层差分线阻抗控制要求两端差值小于8 Ω,但V1.1和V1.2的PCB制作时,从两端测量的阻抗值有明显差异. 共测量了15块样品的阻抗值如表2所示.

图 5 优化设计后铜桥切片图Fig.5 X-section of copper bridge after optimization

图 6 内层铜桥制程能力分析Fig.6 Process capability of innerlayer copper bridge

从表2可知,大BGA端测试点的阻抗实测值都在100±8 Ω以内,极差8.31 Ω;但小BGA端测试点的阻抗实测值偏低且有一部分超出范围,极差9.23 Ω;两端平均差值有8.07 Ω,这不能满足高速电路的高传输速率V≥25 Gbps的要求. 为了分析两端阻抗实测值差异的原因,选取其中12号板来测量蚀刻后的差分线宽,分别取靠近大、小BGA端的5点进行测量,记录下测量数据,如表3所示.

表 3 12号板外层100 Ω差分线的蚀刻线宽实测数据Table 3 Line width measured data of outerlayer 100 Ω differential for number 12 board

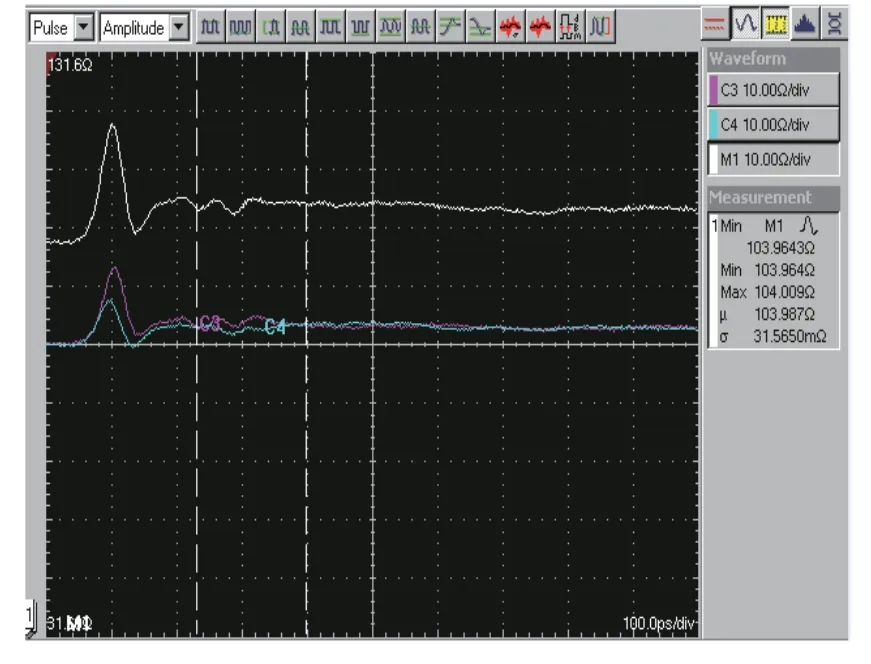

由表3可知,对于大BGA到小BGA长360 mm的差分线,整条线线宽极差超过20 μm,使两端测试的差分阻抗差值超过8 Ω. 对优化前后的阻抗TDR(Time Domain Reflectometry)测试波形进行比较,如图7和图8所示. 按V1.3制作的样品,外层100±8 Ω阻抗值控制效果很好,进行阻抗测试值Cpk分析得知Cpk ≥1.66. 客户端的信号完整性测试结果表明,优化设计的高速PCB能够满足信号完整性要求. 因此,在外层差分线上的一点增加盲孔,把绝大部分外层微带线设计转移为内层带状线是完全可行. 根据信号完整性理论来分析,原因主要有:第一,差分线转移到内层,而内层蚀刻出来的差分线更加均匀且极差小,能够减少信号反射;第二,差分线转移到内层变成带状线,能够减小信号串扰;第三,过孔的寄生电容和寄生电感值相对整个传输线的阻抗可以忽略不计.

图 7 外层100 Ω差分线优化设计前TDR波形Fig.7 TDR waveform for Outerlayer 100 Ω differential before optimized design

2.4.3 导通孔的孔阻抗分析

导通孔0.36±0.05 mm的孔阻抗在V1.2之前版本,孔阻抗最小只能做到80 Ω. 减小钻孔直径,增大反焊盘尺寸和缩小焊盘尺寸,可以把孔阻抗做到83 Ω以上. 对L20的孔阻抗在优化设计前、后测试数据进行分析,通过孔径、反焊盘和焊盘优化设计可提升孔阻抗值2.98 Ω. 进行流程能力分析Cpk=1.66( ≥1.33),说明流程稳定.

3 结论

高速PCB一直是PCB行业宠儿,是电子电路设计和制造研究的热点,高速PCB在5G时代将会得到更多的发展机遇. 密度更高、运行速度更快、信号完整性直接决定高速PCB电气性能、可靠性及其稳定性. 本文基于信号完整性分析高速PCB设计中遇到的信号失真问题,利用相关理论找到传输线阻抗设计和制造的解决方案. 对地层铜桥、外层阻抗线和导通孔阻抗进行优化设计,将设计与制造联系在一起可以让设计者和厂家更好地运用信号完整性分析解决高速PCB的实际问题.