基于FPGA动态重构的快速车牌识别系统*

訾 晶, 张旭欣, 金 婕

(上海工程技术大学 电子电气工程学院,上海 201600)

0 引 言

在卷积神经网络(convolutional neural network,CNN)出现之前,视频图像处理任务效果都不尽如人意,很难实现大规模的商业应用,直到2012年,Krizhevsky A等人提出了一种新的深度神经网络模型AlexNet CNN[1],此后,更大更深的CNN模型被陆续提出,如GoogLeNet[2]。

CNN在计算机视觉领域的应用大都是在软件平台实现的,随着硬件设备的更新迭代,计算能力的提升,使得在硬件平台开发CNN成为了可能,尤其是现场可编程门阵列(field programmable gate array,FPGA)的快速发展[3]。

硬件加速网络的设计侧重于网络并行化的实现,快速算法的应用等方面,但针对FPGA自身重构特性的研究较少。Kaestner F等人的研究[4]充分展现了FPGA部分重构的优势,利用有限的硬件资源,通过部分重构实现卷积,采用软硬件结合的实现形式,有效提高神经网络执行速度。

本文将采用FPGA动态部分重构技术和高层次综合工具,完成快速车牌识别的系统设计。设计CNN模型,利用Caffe深度学习框架训练相关数据[5];按照动态部分重构(dynamic partial reconfiguration,DPR)实现流程[6],生成完整及部分比特流,完成CNN的两种软硬件方案设计;基于PYNQ-Z1开发板,完成车牌识别系统设计。

1 卷积神经网络

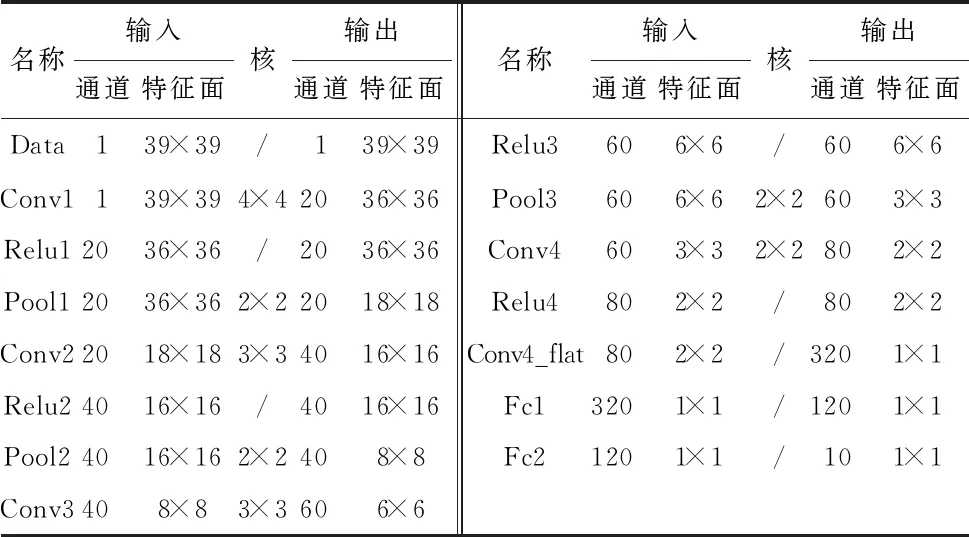

针对车牌字符的特点,设计CNN模型。该网络包含卷积层,修正线性单元(rectified linear unit,ReLU),最大池化层以及全连接层。结构信息如表1所示。

表1 CNN结构信息

卷积后加ReLU作为激活函数,一方面减少反向传播(back propagation,BP)求误差梯度的计算量,另一方面稀疏网络,减少参数的相互依赖性,缓解过拟合;此外,最大池化层,压缩了卷积后的特征面,提取主要特征,进一步简化网络计算复杂度。

2 车牌识别系统结构设计

2.1 系统结构

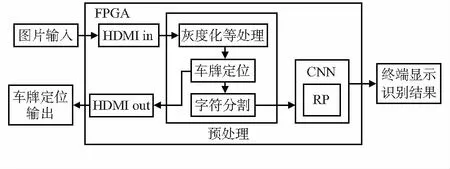

车牌识别系统的结构设计如图1所示。在Xilinx PYNQ-Z1上实现FPGA的部分重构,开发板包含一个ZC7020芯片,该芯片有一个双核ARM A9处理器,配备各种外围设备,作为一个处理系统(processing system,PS);此外,还有一个可编程逻辑(programmable logic,PL)XC7Z020。异构FPGA本身内嵌了处理器,因此使得软硬件设计更加灵活。

计算密集型且模块化较强的部分,利用FPGA的PL实现,即所有硬件接口和部分卷积神经网络模块;图片的预处理由PS实现。该系统优点是采用软硬件结合的形式,以及FPGA的部分重构特性,对硬件资源重复利用,节省资源,提高识别效率。

2.2 硬件设计

该系统通过高清多媒体接口(high definition multimedia interface,HDMI)接收、输出图片,利用动态局部重配置(dynamic partial reconfiguration,DPR)技术,实现对CNN计算密集的卷积层重构,因此硬件设计主要包括HDMI接口调用以及卷积的重构。

HDMI是PYNQ-Z1上的外设,可以直接调用相关IP(即Overlay)和接口IP来驱动HDMI。所以硬件设计的重点即实现卷积的重构,包括卷积IP设计与优化。

2.2.1 卷积IP设计

CNN中最为密集的计算是卷积,利用FPGA来实现可以有效地提高卷积计算效率,并降低功耗。在FPGA上实现卷积,首先设计实现卷积的硬件电路并生成相应的IP,在片上系统(system on chip,SoC)设计时进行调用。

尽管使用Verilog语言进行RTL(register transfer level)级设计,效率更高,但对于网络和FPGA器件来说,由于考虑到后期调整结构和充分发挥FPGA器件的灵活性需要,本文利用Xilinx Vivado HLS 2017.3软件,采用高层次综合(high-level synthesis,HLS)工具和C++作为设计语言,通过综合自动产生RTL级电路,并生成IP,减少重复设计工作量并提高设计效率。

默认情况下,卷积的所有嵌套循环都是按顺序执行的,在卷积过程中,Vivado HLS提供了不同的编译指令(pragma)来影响循环调度和FPGA资源分配。用于优化的两个最重要的指令是unrolling和pipelining[7],因此,根据每一层卷积的特点,以并行或流水线方式处理嵌套循环,优化IP。卷积的嵌套循环在整个输入深度、高度和宽度上进行,还要考虑卷积的输出深度以及卷积核,整个卷积有6层嵌套循环,可以对这些循环进行优化,然而性能的线性增长取决于硬件资源利用率,所以要在每个卷积层的资源利用和性能之间找到最佳的平衡点。

图1 车牌识别系统模块框图

2.2.2 部分重构流程

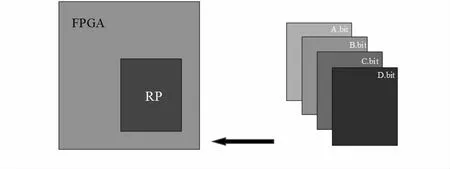

FPGA的部分重构,在FPGA上开辟一块可重构分区(reconfigurable partition,RP),重构RP逻辑,如图2所示。

图2 部分重构

FPGA设计中的逻辑分为可重构逻辑和静态逻辑,图2中FPGA的灰色区域表示静态逻辑,RP部分表示可重构逻辑,通过加载几个比特流(bitstream)中的一个来修改RP中的功能,完成部分重构,而静态逻辑保持运行,不受部分比特流加载的影响。

本文针对4层卷积实现重构,因此要进行4次重构循环,生成4组可用的完整及部分比特流。

第一次循环,综合后画出RP,并设置重构属性,优化、布局、布线后保存可共享静态逻辑,供后续循环调用,同时第一次生成比特流;后续循环,替换卷积IP,综合后只要将卷积部分的设计检查点(design check point,DCP)加载到共享静态逻辑,同样优化、布局、布线后直接生成比特流。

2.3 软件设计

软件的设计主要是实现图片的预处理,根据图1所示,图片预处理主要包括车牌定位及字符分割,这一部分通过软件来设计。

首先,从HDMI帧缓冲区提取接收的图片,调用OpenCV的图像处理库进行预处理,根据颜色先定位车牌的大致区域,在处理颜色信息时,须变换通道,车牌图片是3通道的RGB图,经过HDMI输入FPGA后,变成GBR通道,而Opencv是BGR通道。之后,调用Opencv的轮廓提取函数,提取所有检测到的轮廓,根据轮廓的长宽比及大小,筛选掉干扰轮廓。字符分割也利用轮廓提取的方式。

3 实 现

3.1 硬件实现

在Xilinx Vivado 2017.3软件上,利用卷积IP以及其他一些必要IP和接口IP,完成SoC的块设计(block design),即原理图设计。主要包括1个AXI Interconnect IP和3个功能模块:AXI Interconnect IP实现将一个或多个AXI(advanced extensible interface)存储器映射的主器件连接到一个或多个存储器映射的从器件;hdmi模块实现图片接收与输出,并用VDMA(video direct memory access)IP作为帧缓冲区,缓存数据;proc模块实现卷积操作;ps模块包含两个ARM A9的硬核,实现各IP初始化与配置。

Proc模块中的卷积IP,在部分重构过程是可替换的,卷积IP每次替换后都需要复位,这里通过一个简单的通用输入/输出(GPIO)IP来实现重构复位。此外,输入到卷积IP的数据通过一个简单的DMA(direct memory access)IP连接。

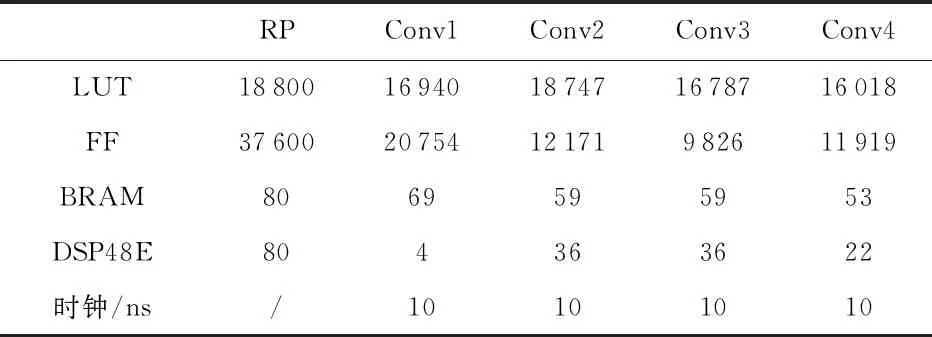

由于FPGA可重构区域的有限性,分配RP时要考虑最大区域限制和时序要求,RP区最多占用29 %BRAM,37 %DSP48E,36 %FF以及36 % LUT。RP和各卷积层的资源占用如表2。

表2 卷积资源占用

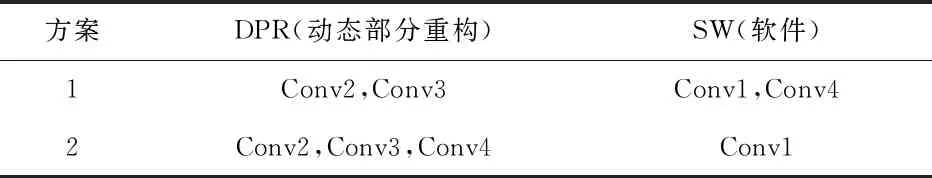

当FPGA的可编程逻辑资源和存储资源较少时,FPGA不能同时实现所有的卷积层,所以本设计采用部分重构,以及软硬件结合的方式。采用软硬件组合的方案,实现4层卷积,如表3。

表3 软硬件组合方案

3.2 软件实现

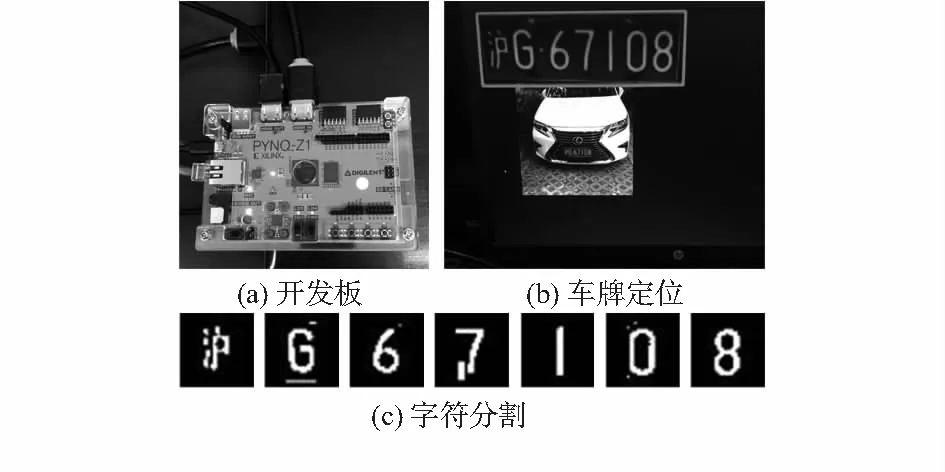

在Xilinx SDK 2017.3软件上,借助开发板HDMI接口,获取外部图片,首先处理颜色信息,调用C++图像类Mat中的通道函数channels分离图片的3个通道,根据2.3节中的设计,重组通道顺序,通过颜色锁定车牌的大致区域。之后利用C++调用Opencv图像处理库,对图片灰度化、去噪等处理,调用轮廓提取函数,提取检测到的所有可能轮廓,经过筛选、定位,由HDMI输出到显示器。然后分割车牌字符,将字符处理成39×39的二值图,完成图片的预处理。预处理效果如图3所示。

图3 系统预处理

3.3 数据训练

利用Caffe深度学习框架,搭建CNN模型,网络训练主要针对车牌字符。众所周知国内的家用车车牌大部分是蓝底白字,有3类字符,31个汉字(不包括港澳台)、24个大写英文字母(不包括I和O)以及10个阿拉伯数字。

考虑到已有MNIST手写数字数据集,所以尝试以MNIST格式来制作字符数据集,字符统一采用39×39的二值图。通过实地拍摄大量车牌,并对车牌字符分割、分类,最后取3类汉字(沪、浙、苏)、10类数字以及24类字母的图片来制作,每类字符2 500张,每类再取250张用于测试。

根据不同的数据集,相应改变表1中最后的全连接层的输出通道即分类数,结果为MNIST和自制数据集的分类数分别为10和37,准确率分别为99.08 %和99.45 %。

4 结 果

在Ubuntu16.04操作系统下,系统的软件开发基于 Xilinx SDK 2017.3软件,硬件开发基于系统开发板PYNQ—Z1。数据训练利用NVIDIA Quadro P2000 GPU实现加速。

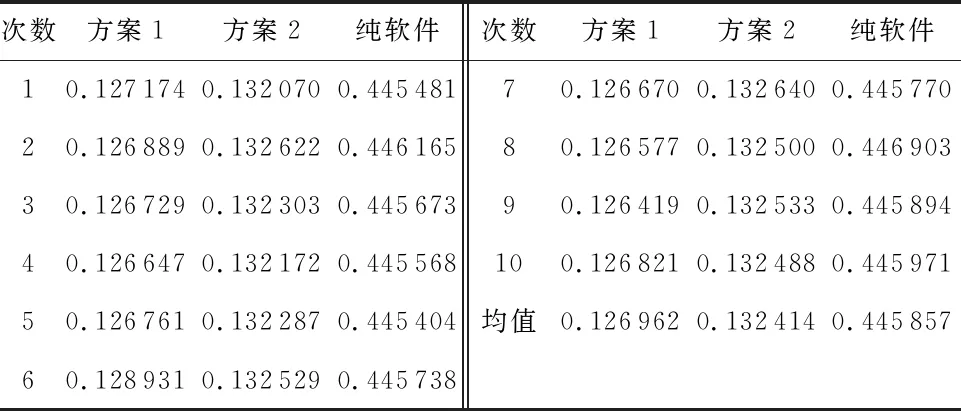

系统预处理部分实现结果如图3所示,车牌被成功定位,并通过HDMI输出显示,字符也成功分割并二值化,说明软件的预处理设计可行。由于FPGA的重配置需要耗费一定的时间,因此重构的次数不是越多越好。为了比较表3所列2种方案的优劣,本文进行了10次测试,并与纯软件执行方式进行比较,结果如表4。

表4 10次实验的执行时间 s

方案1和方案2的执行速度均比纯软件的方式快,速度都提高了3倍以上,通过软硬件联合的方式,有效提高了速度,方案1执行速度最大提升了3.51倍。

实验中为了验证所设计的系统对车牌识别的效果,随机取5张车牌,最终识别结果在开发板的终端显示,如图4。

对比输入图片,随机的5张车牌字符都能被正确识别,字符识别率与训练结果相当,证明所设计的车牌识别系统可行。

本设计的实现方法不仅能得到99 %以上的字符识别精度,同时相比纯软件方式,提高了执行速度,通过FPGA加速,有效解决了传统网络精度与速度不可兼顾的问题。

5 结束语

本文充分利用FPGA动态部分重构技术和HLS工具,实现了快速车牌识别。但还有进一步优化的空间,比如改进神经网络的结构和字符二值化后的降噪,改进预处理方法,减少预处理时间等。神经网络的应用有很多,如目标追踪、车辆检测等[8],未来,将本系统与微型机器人相结合,可以实现对高速公路、住宅区或停车场车辆的灵活管理。